模型机设计报告

一、设计目的

完整、连贯地运用《数字电路与逻辑设计》所学到的知识,熟练掌握 EDA

工具基本使用方法,为学习好后续《计算机原理》课程做铺垫。

二、设计内容

- 按给定的数据格式和指令系统,使用EDA工具设计一台用硬连线逻辑控制的简易计算机系统;

- 要求灵活运用各方面知识,使得所设计的计算机系统具有较佳的性能;

- 对所做设计的性能指标进行分析,整理出设计报告。

简易计算机系统

- 数据格式

数据字采用8位二进制定点补码表示,其中最高位(第7位)为符号位,小数点可视为最左或最右,其数值表示范围分别为:-1≤X<1或-128≤X<127。

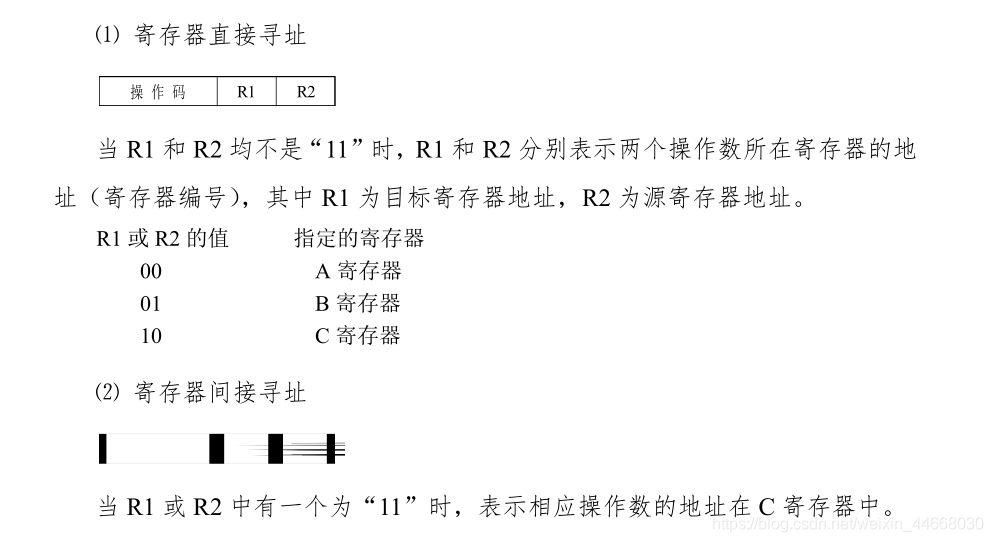

- 寻址方式

指令的高4位为操作码,低4位分别用2位表示目的寄存器和源寄存器的编号或表示寻址方式。

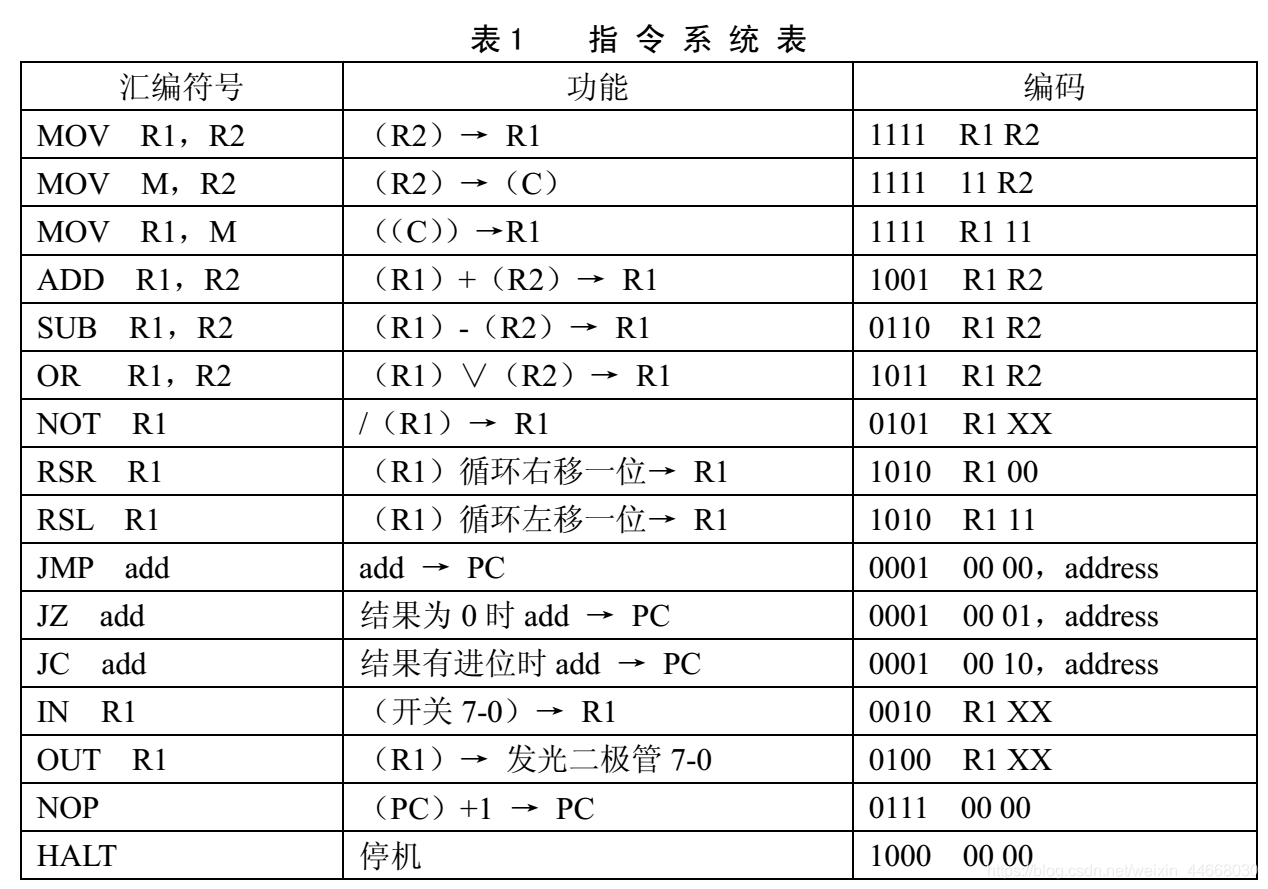

主要实现以下指令:

- 详细设计

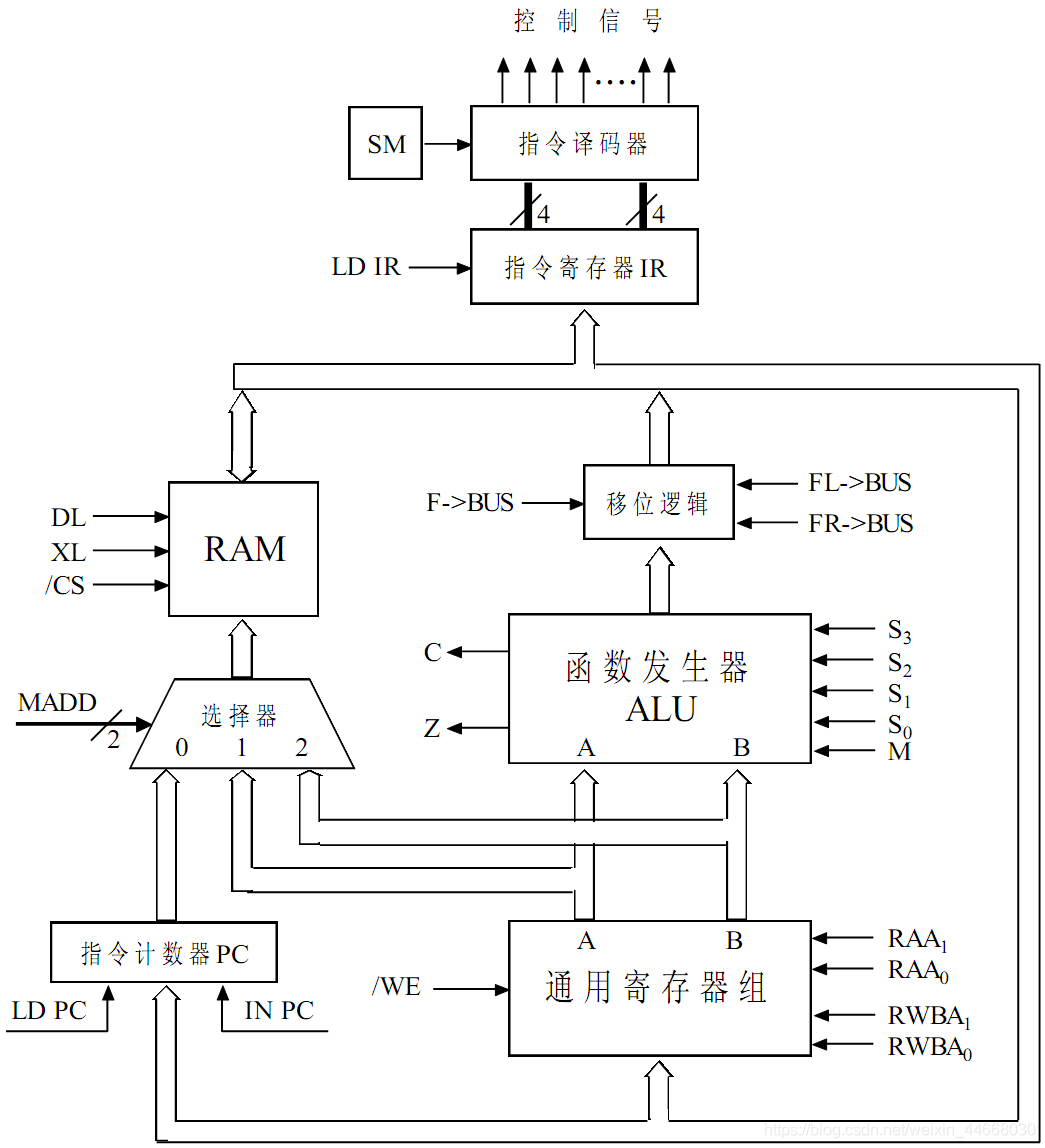

3.1设计的整体架构

整个CPU的设计通路为:

控制信号:

指令寄存器 IR 接收到一条机器指令后,这条指令会被译码执行。指令通过译码产生出的各种控制信号在时钟信号的配合下控制着指令执行的全过程。

因此,需要将执行每条指令所对应的全部的控制信号生成出来,进行综合分析、化简,并使他们在不同的周期和时间对不同的器件产生作用,然后实现整个操作。

以下是所用基本控制信号列表。

由数据通路可知要实现简易计算机系统主要包括以下几个模块:

- 指令计数器PC 控制信号:LD_PC,IN_PC,clk

- 3-1选择器 控制信号:MADD

- 可读可存存储器RAM_IO 控制信号:DL,XL,/CS,clk

- 指令寄存器IR 控制信号:LD_IR,clk

- SM信号发生器 控制信号:clk

- 指令译码器 控制信号:SM

- 控制信号发生器 控制信号:指令译码器发出的所有信号,SM,C,Z

- 通用寄存器组 控制信号:/WE,RAA1,RAA2,RWBA1,RWBA2

- 函数发生器ALU 控制信号:M,S[3..0]

- 移位逻辑 控制信号:F_BUS,FL_BUS,FR_BUS

- C,Z寄存器 控制信号:clk

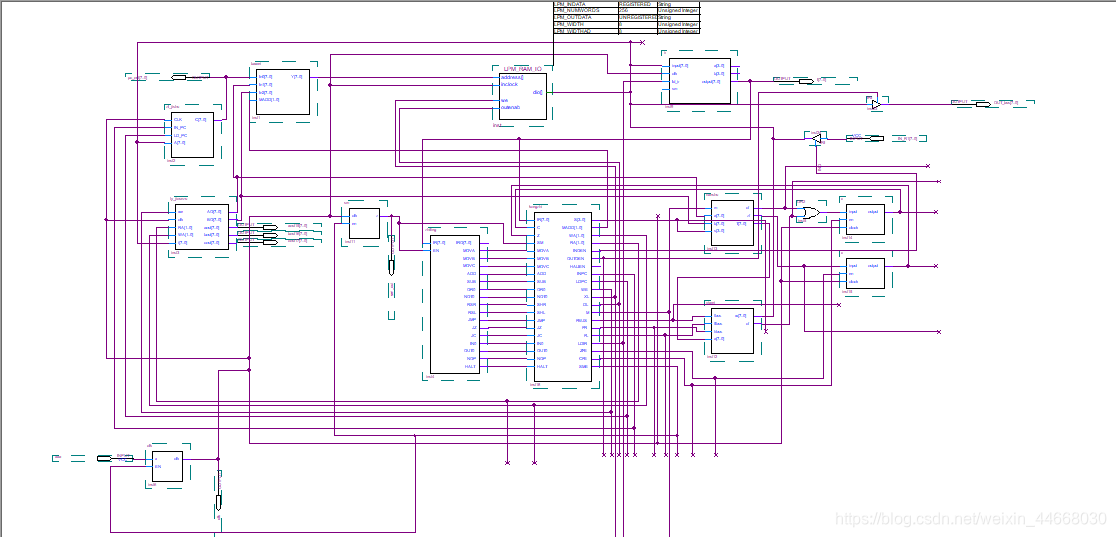

总逻辑图:添加了部分输出端口便于波形仿真时观察

3.2各模块的具体实现

(此部分必须有模块的接口设计,功能实现,功能的仿真验证等内容。)

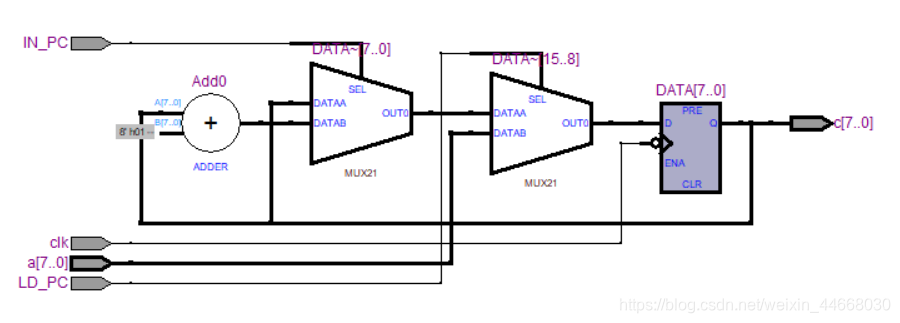

- 指令计数器PC

- 模块的接口设计

控制信号:LD_PC,IN_PC,clk

输入数据:地址值 a[7..0] 输出数据:地址值 c[7..0]

-

- 功能实现

根据指令计数器PC的功能可知:

在时钟的下降沿,若LD_PC = 1,输入外部的地址值,并输出该地址值;

若IN_PC = 1,将原先的地址值加一,并输出该地址值。

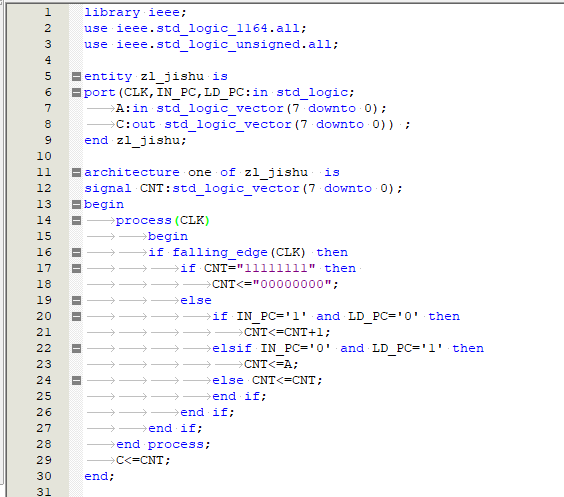

VHDL实现如下所示:

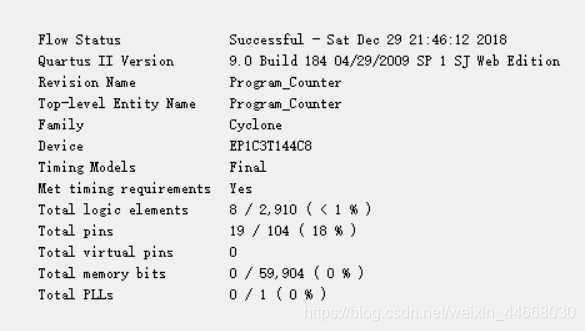

分析与综合( Analysis & Synthesis ),适配( Fitter ),编程( Assembler ),时序分析Classical Timing Analysis )均通过。如下所示:

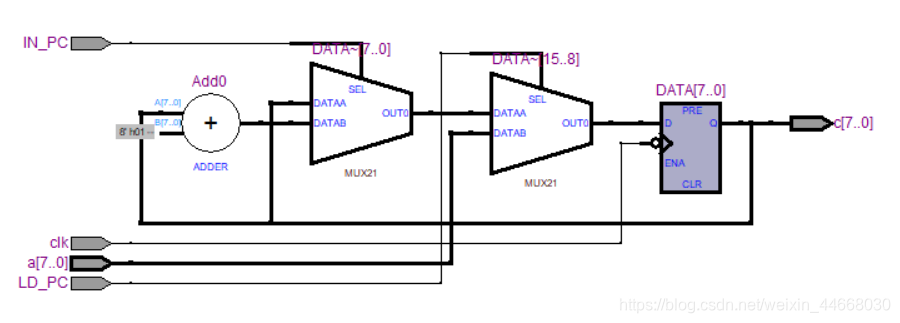

RTL如下所示:

-

- 功能的仿真验证

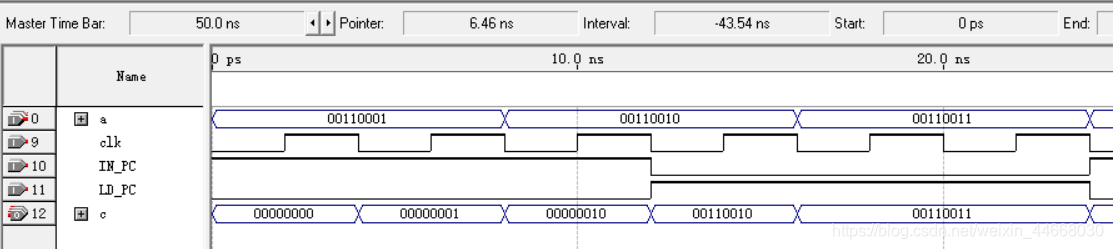

根据指令计数器PC的功能,设计clk,LD_PC,IN_PC,a[7..0]的值

进行功能仿真,其仿真结果如下所示:

完全实现了指令计数器PC的全部功能。

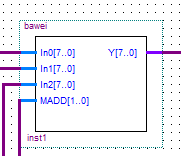

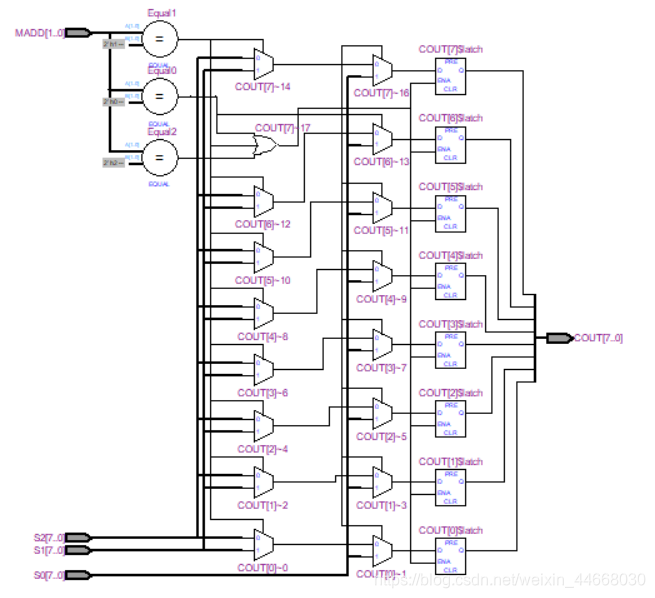

- 选择器

- 模块的接口设计

控制信号:MADD

输入信号:ln0[7..0],ln1[7..0],ln2[7..0] 输出信号:Y[7..0]

-

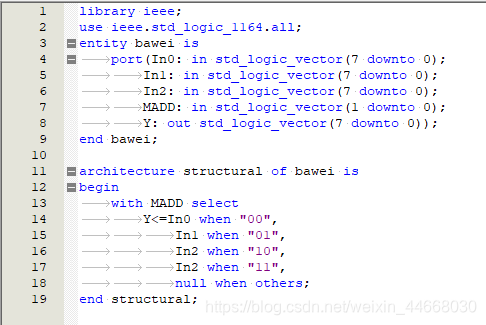

- 功能实现

当MADD = 00时,输出信息 Y[7..0] 为输入信息 ln0[7..0];

当MADD = 01时,输出信息 Y[7..0] 为输入信息 ln1[7..0];

当MADD = 10时,输出信息 Y[7..0] 为输入信息 ln2[7..0]。

VHDL的实现如下所示:

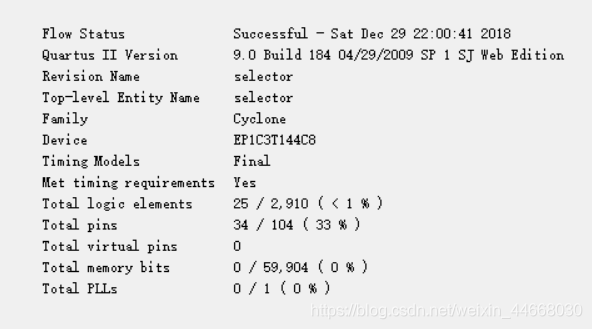

分析与综合( Analysis & Synthesis ),适配( Fitter ),编程( Assembler ),时序分析Classical Timing Analysis )均通过。如下所示:

RTL如下所示:

-

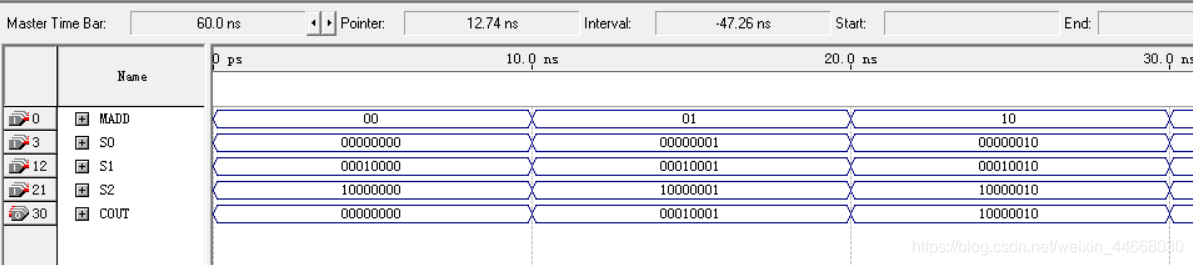

- 功能的仿真验证

根据选择器的功能可以设计控制信号:MADD,输入信号:S0[7..0],S1[7..0],S2[7..0]的值,得到输出信号COUT[7..0]。

进行功能仿真,其仿真结果如下所示:

完全实现选择器的全部功能。

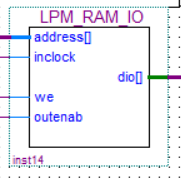

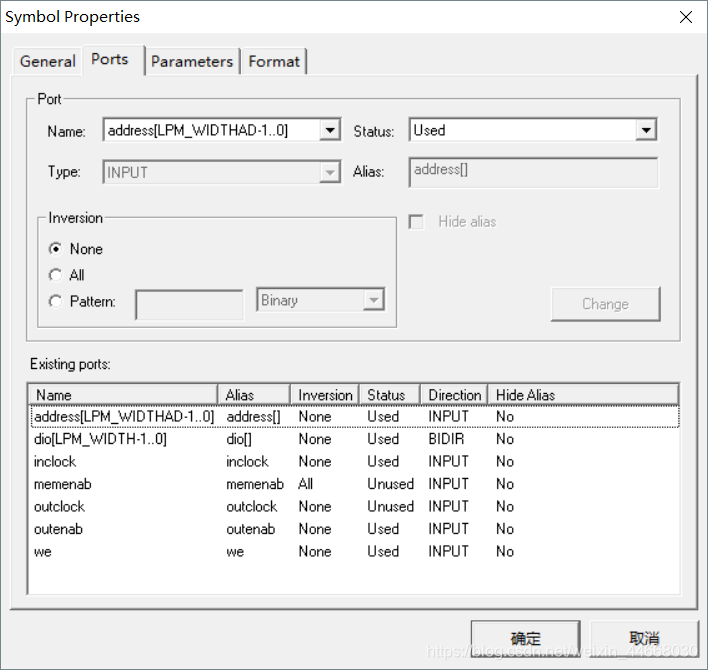

- 可读可存存储器RAM_IO

- 模块的接口设计

控制信号:inclock ( clk ),we (XL),outenab(DL)

输入信号:address[7..0] 输出信号:dio[7..0]

-

- 功能实现

在左侧的工具栏中选择【Symbol Tool】

在Name中输入 LPM_RAM_IO可以用这个元件。

把LPM_RAM_IO元件提出来,按照逻辑图的设计安装在原理图中。

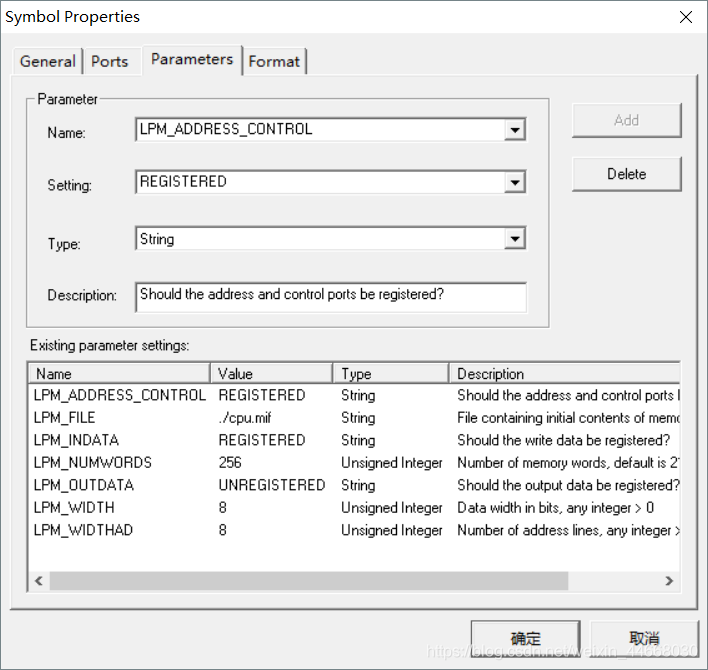

设置LPM_RAM_IO的各项参数,如下所示:

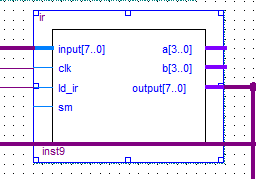

- 指令寄存器IR

- 模块的接口设计

控制信号:LD_IR,clk

输入信号:需执行指令input[7..0] 输出信号:需执行指令output[7..0]

-

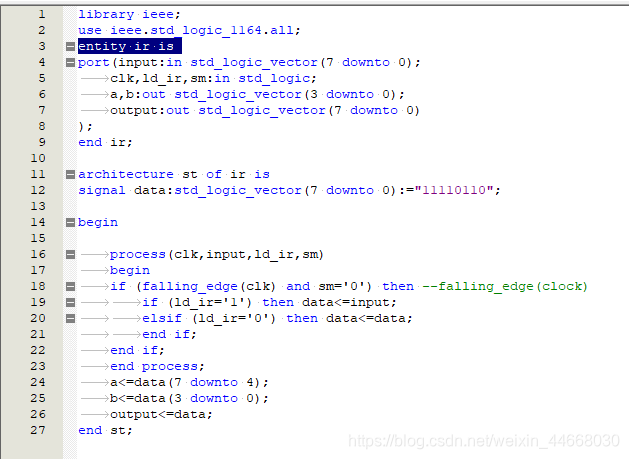

- 功能实现

根据指令寄存器IR的功能可知:

当处于时钟下降沿时,LD_IR = 1时,输出信号output[7..0]为输入信号input[7..0]。

VHDL的实现如下所示:

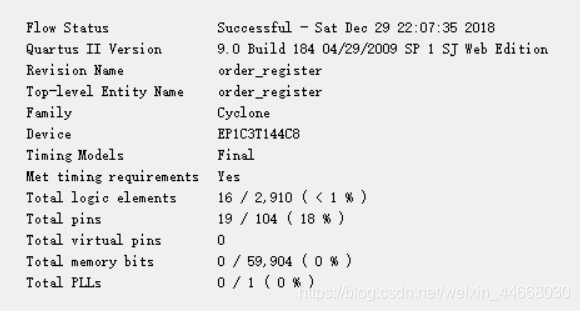

分析与综合( Analysis & Synthesis ),适配( Fitter ),编程( Assembler ),时序分析Classical Timing Analysis )均通过。如下所示:

RTL如下所示:

-

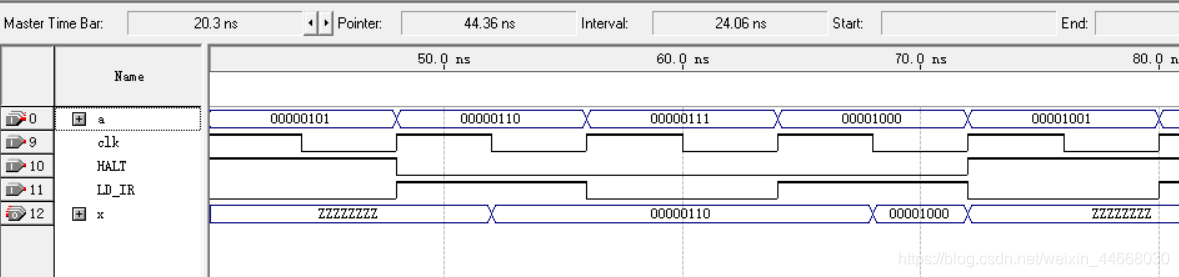

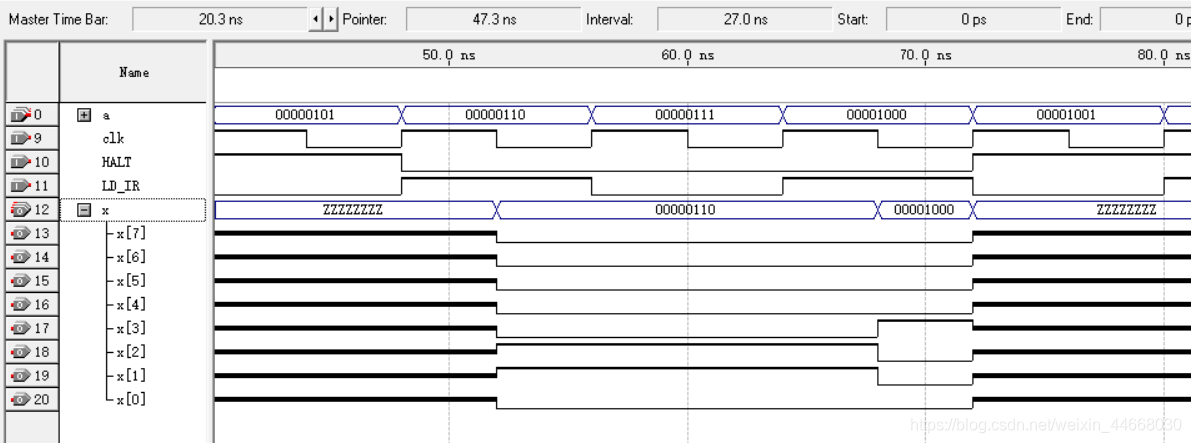

- 功能的仿真验证

根据指令寄存器IR的功能可以设计控制信号:LD_IR, clk,输入信号:需执行指令input[7..0] 的值,得到输出信号:需执行指令output[7..0]。

进行功能仿真,其仿真结果如下所示:

完全实现指令寄存器IR的全部功能。

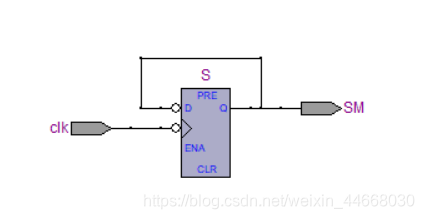

- SM信号发生器

- 模块的接口设计

控制信号:clk,en 输出信号:SM

-

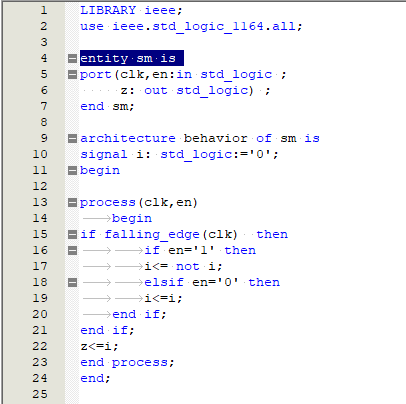

- 功能实现

根据SM信号发生器的功能可知:

当处于时钟下降沿并且en=1时,输出信号与之前状态的输出信号相反。

VHDL的实现如下所示:

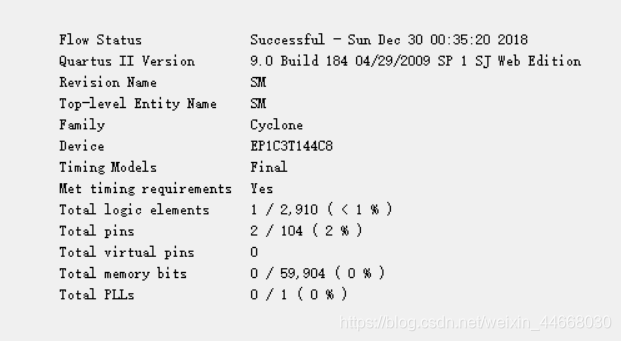

分析与综合( Analysis & Synthesis ),适配( Fitter ),编程( Assembler ),时序分析Classical Timing Analysis )均通过。如下所示:

RTL如下所示:

-

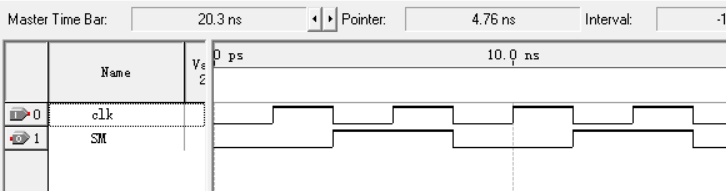

- 功能的仿真验证

根据SM信号发生器的功能可以设计控制信号: clk,得到输出信号:SM。

进行功能仿真,其仿真结果如下所示:

完全实现SM信号发生器的全部功能。

- 指令译码器

- 模块的接口设计

控制信号:EN(SM) 输入信号:需执行指令IR[7..0]

输出信号:需执行指令IRO[7..0],

各项指令的控制信号:MOVA,MOVB,MOVC,ADD,SUB,OR0,NOT0,RSR,RSL,JMP,JZ,JC,IN0,OUT0,NOP,HALT

本报告介绍了一款基于EDA工具设计的简易计算机系统。系统采用8位二进制定点补码表示,支持多种指令集,包括数据处理和控制指令。设计包括指令计数器、选择器等关键模块。

本报告介绍了一款基于EDA工具设计的简易计算机系统。系统采用8位二进制定点补码表示,支持多种指令集,包括数据处理和控制指令。设计包括指令计数器、选择器等关键模块。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?