描述

题目描述:

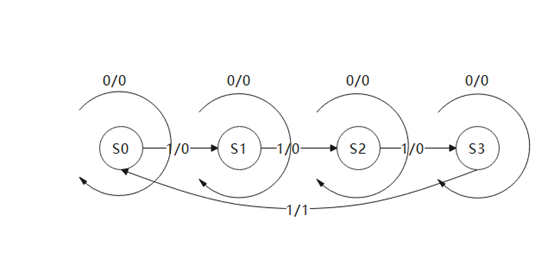

如图所示为两种状态机中的一种,请根据状态转移图写出代码,状态转移线上的0/0等表示的意思是过程中data/flag的值。

要求:

1、 必须使用对应类型的状态机

2、 使用三段式描述方法,输出判断要求要用到对现态的判断

注意rst为低电平复位

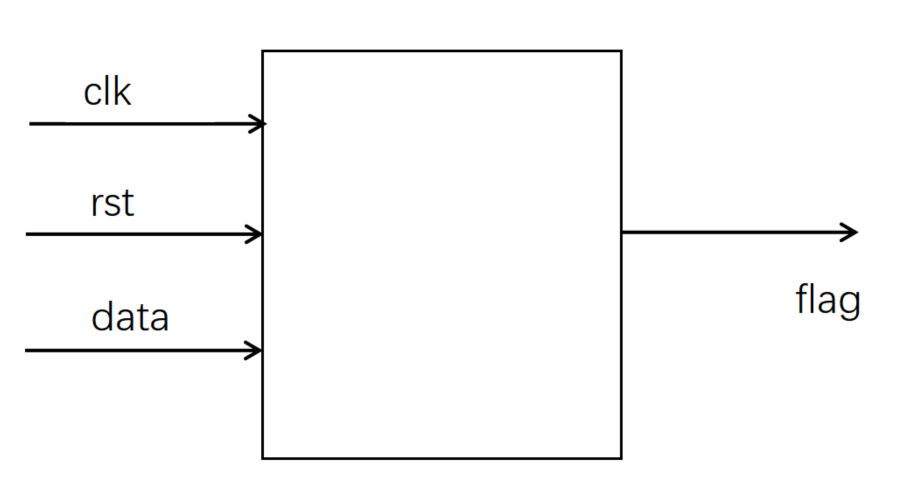

信号示意图:

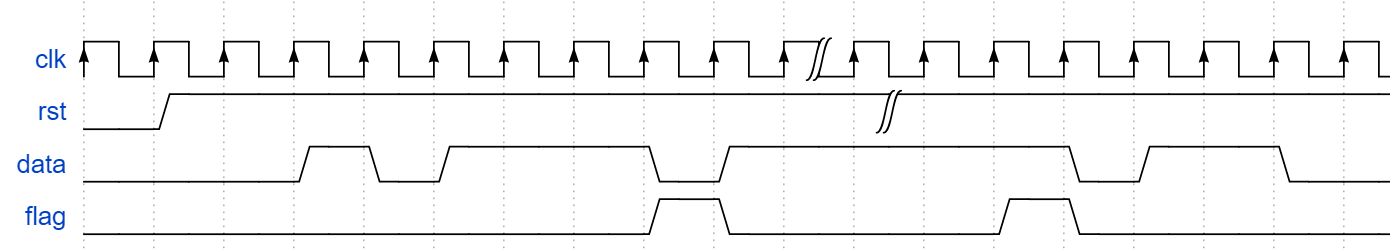

波形示意图:

输入描述:

输入信号 clk rst data

类型 wire

输出描述:

输出信号 flag

类型 reg

1、Moore型:转换的输出由当前状态决定,,每个节点(状态)都标有输出值。

2、Mealy型:转换的输出由当前状态和当前输入的组合决定,每个弧(过渡)都标有输出值。

`timescale 1ns/1ns

module fsm1(

input wire clk ,

input wire rst ,

input wire data ,

output reg flag

);

//*************code***********//

parameter s0 = 0;

parameter s1 = 1;

parameter s2 = 2;

parameter s3 = 3;

reg [2:0] cur_state ,nx_state;

always@(posedge clk or negedge rst)begin

if(!rst)

cur_state <= s0;

else

cur_state <= nx_state;

end

always@(*)begin

case(cur_state)

s0:

if(!data)

nx_state = s0;

else

nx_state = s1;

s1:

if(!data)

nx_state = s1;

else

nx_state = s2;

s2:

if(!data)

nx_state = s2;

else

nx_state = s3;

s3:

if(!data)

nx_state = s3;

else

nx_state = s0;

endcase

end

always@(posedge clk or negedge rst)begin

if(!rst)

flag <= 0;

else begin

if(cur_state == s3 && data == 1)

flag <= 1;

else

flag <= 0;

end

end

//*************code***********//

endmodule

391

391

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?