五、存储器与CPU的连接

1、存储器容量的扩展

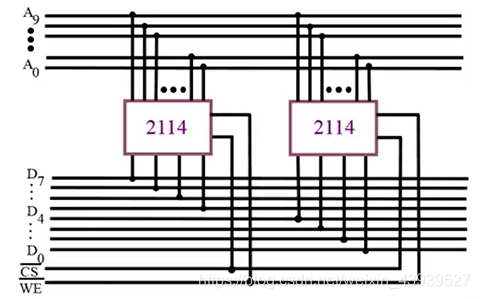

(1)位拓展(增加存储字长)

用2片 1K x 4位存储芯片组成1K x8位的存储器

1K:10根地址线

8位:8根数据线

位拓展就是将两个芯片连接当成一个芯片使用

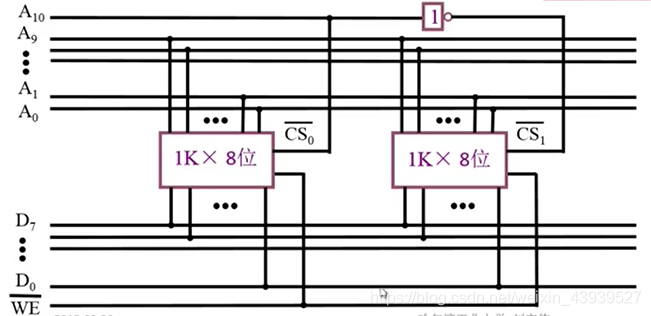

(2)字拓展(增加存储字的数量)

用2片1K x 8位存储芯片组成2K x8位的存储器

2K:11根地址线

8位:8根数据线

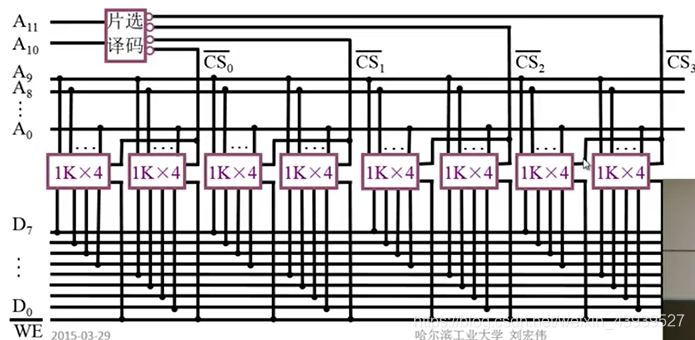

(3)字、位拓展

用8片1K x 4位存储芯片组成4K x 8位的存储器

4K:12根地址线

8位:8根数据线

2、存储器与CPU的连接

(1)地址线的连接

(2)数据线的连接

(3)读/写命令线的连接

(4)片选线的连接

(5)合理选择存储芯片

(6)其他 时序、负载

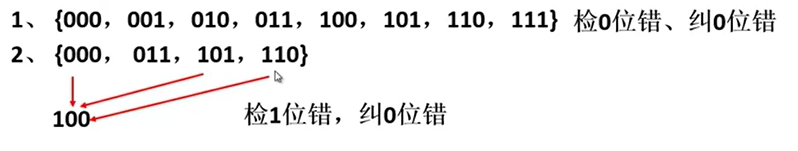

六、存储器的校验

合法代码集

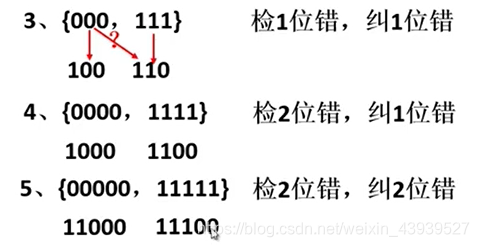

1、编码的最小距离

任意两组合法代码之间二进制数的最小差异

编码的纠错、检错能力与编码的最小距离有关

L-1=D+C(D>=C)

L—编码的最小距离 L=3

D—检测错误的位数,具有一位纠错能力

C—纠正错误的位数

汉明码是具有一位纠错能力的编码

2、汉明码的组成

汉明码采用奇偶校验

汉明码采用分组校验

汉明码的分组是一种非划分方式

分成三组,每组有一位校验位,共包括四位数据位

组成汉明码的三要素

汉明码的组成须增添2^k>=n+k+1位检测位

检测位的位置2^i

检测位的取值与该位所在的检测“小组”承担的奇偶校验任务有关

3、汉明码的纠错过程

形成新的检测位Pi,其位数与增添的检测位有关,如增添3位(k=3),新的检测位为P4P2P1

P1=1⊕3⊕5⊕7

P2=2⊕3⊕6⊕7

P4=4⊕5⊕6⊕7

对于按“偶校验”配置的汉明码,不出错时P1=0,P2=0,P4=0

七、提高访存速度的措施

- 采用高速器件

- 采用层次结构Cache-主存

- 调整主存结构

1、单体多字系统

2、多体并行系统

(1) 高位交叉 顺序编址

(2)低位交叉 各个体轮流编址

3、高性能存储芯片

(1)SDRAM(同步DRAM)

在系统时钟的控制下进行读出和写入

CPU无需等待

(2)PDRAM

由Rambus开发,主要解决存储器带宽问题

(3)带Cache的DRAM

在DRAM的芯片内集成了一个由SRAM组成的Cache,有利于猝发式读取

1292

1292

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?