CPU 执行的指令:

“ldr r0,[某个地址 A]”,ldr 是装载 4个字节,这是从这个地址里读取某个数据存到 r0 里去。

A 地址的 1 字节数据。

A+1 地址的 1 字节数据。

A+2 地址的 1 字节数据。

A+3 地址的 1 字节数据。

即, ldr 是得到 4 个地址上的数据共4字节。

“ ldb r0,[某个地址B]”, ldb是装载1个字节。对CPU来说一个地址对应的数据是 1 字节。

B 地址的 1 字节数据。

例1:

Mov R1,#0

Ldr R0,[R1]

从R1把的地方即0地址读到4字节。

相当于:

从0地址取1字节

从1地址取1字节

从2地址取1字节

从3地址取1字节

假设 NOR 是 16 位(有 16 条数据线), CPU 发出“ldr r0,[0]” ,则 0 是对应NORFLASH。这里是想得到 4 个字节的数据。 NORFLASH 是以 16 位来访问的,意思是说访问 NOR 时,一次只能返回一个 16 位的数据。(16 位的 NORFLASH 硬件上只能一次提供 2 字节数据)。

所以,上面的情况是 CPU 一次要读 4 字节,而 16 位的 NOR 一次只能提供 2 字节。这个

问题,就由“内存控制器”来处理。

“内存控制器”要发起 2 次传输:

①,第一次,发出 0 地址,得到 2 字节。(地址 0~1 处的 2 字节)

②,第二次,发出 2 地址,得到 2 字节。(地址 2~3 处的 2 字节)

③,将两次得到的字节数据组合后返回给 CPU。

所以要设置“内存控制器”位宽,CPU 想得到 4 字节数据时,内存控制器就知道要发出 2 次操作。至于如何将数据提交过来,就由内存控制器来确定。

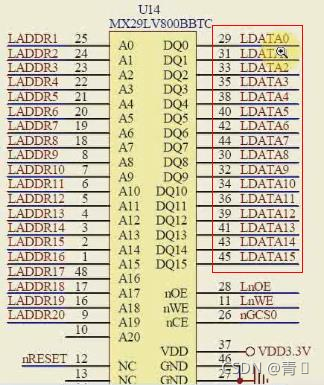

如上 NORFLASH, CPU 的发出的地址 1“ LADDR1”接到了 NORFLASH 的“ A0”地址。

则:“内存控制器”要发起 2 次传输:

NOR:

①,第一次,发出 0 地址,得到 2 字节。 NOR 得到 0 地址,返回第 0 个 2 字节。

②,第二次,发出 2 地址,得到 2 字节。 2 为 000010,而 LADDR0 没有接,而是接的

LADDR1-A0,这时 NOR 看到的是地址 1 。故返回第一个 2 字节。

③,将两次得到的字节数据返回给 CPU

例 2:

Mov R1,#3

Ldb R0,[R1]

CPU想得到地址 3 的一个字节数据。

“内存控制器”要发起 2 次传输:

①发地址 3(000011)

NOR 得到地址 1(LADDR0 没接,则是从第 2 个 1 接的),返回第0个2字节。

②内存控制器从这2字节里取出高字节那一位,传给CPU。这也说明了为什么地址线错开一位。

取出哪一位是由没有接的那根地址线来决定的,比如这里没有接的LADDR0为1,所以返回两字节中高位(计算机是从0开始计数),

一般的规律是,8位位宽不错位,16位位宽错一位,32位位宽错二位,以此类推。

本文详细阐述了CPU执行指令加载数据的过程,特别是当CPU试图从16位NORFLASH中读取4字节数据时,内存控制器如何通过两次传输来完成任务。内容涉及ldrr0和ldbr0指令,以及内存控制器如何处理位宽不匹配问题,解释了地址线错位的原理,并给出了具体例子进行说明。

本文详细阐述了CPU执行指令加载数据的过程,特别是当CPU试图从16位NORFLASH中读取4字节数据时,内存控制器如何通过两次传输来完成任务。内容涉及ldrr0和ldbr0指令,以及内存控制器如何处理位宽不匹配问题,解释了地址线错位的原理,并给出了具体例子进行说明。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?