1.地址多路器模块的作用

地址多路器用于选择输出的地址是PC(程序计数)地址还是数据/端口地址。每个指令周期的前4个时钟周期用于从ROM中读取指令,输出的应是PC地址,后4个时钟周期用于对RAM或端口的读写,该地址由指令给出。

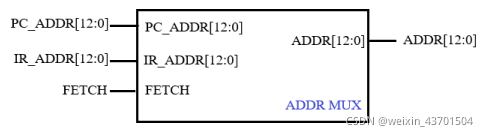

2.模块端口图

3.端口功能描述

地址的选择输出信号由时钟发生器产生的8分频信号FETCH提供。PC_ADDR为程序计数器产生的指令地址;IR_ADDR为指令寄存器输出信号OPC_IRADDRS的低13位。

4.Verilog代码

module addr (

pc_addr ,

ir_addr ,

fetch ,

addr

);

input [12: 0] pc_addr ;

input [12: 0] ir_addr ;

input fetch ;

output [12: 0] addr ;

assign addr = fetch? pc_addr: ir_addr;

endmoduletestbench:

`timescale 1ns / 1ps

//

// fetch = 0, output pc_addr;fetch = 1, output ir_addr

//

module addr_tb();

reg [12: 0] pc_addr ;

reg [12: 0] ir_addr ;

reg fetch ;

wire [12: 0] addr ;

addr u5(

.pc_addr ( pc_addr ),

.ir_addr ( ir_addr ),

.fetch ( fetch ),

.addr ( addr )

);

initial begin

pc_addr = 12'b0000_0000_1111;

ir_addr = 12'b1111_1111_0000;

fetch = 0;

#80;

fetch = 1;

#80;

pc_addr = 12'b1111_0000_1111;

ir_addr = 12'b0000_1111_0000;

#80;

fetch = 0;

#80;

fetch = 1;

#80;

end

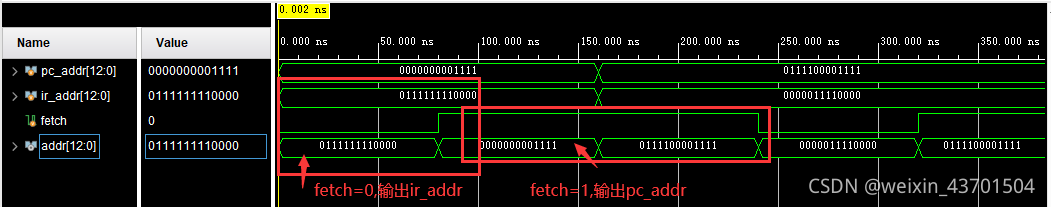

endmodule仿真图:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?