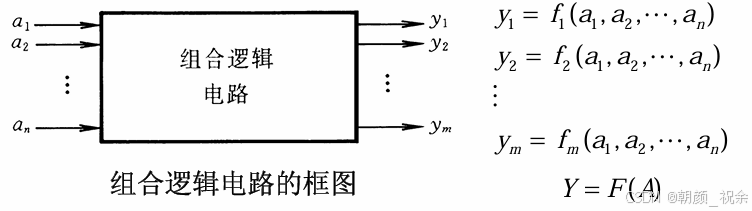

4. 数字逻辑电路分类:

组合逻辑电路和时序逻辑电路

组合逻辑电路的特点:

任意时刻的输出仅取决于该时刻的输入,与电路原来的的状态无关。

逻辑功能的描述:

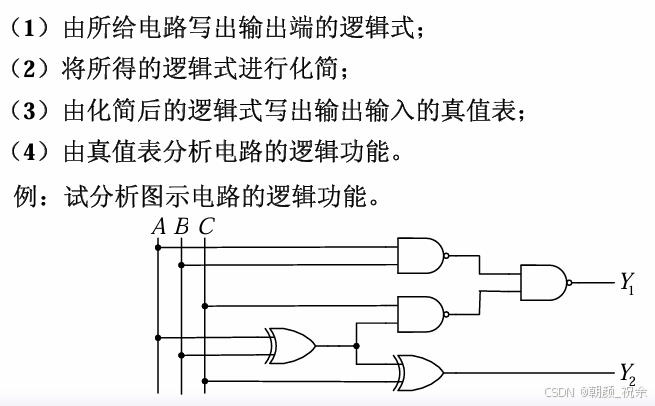

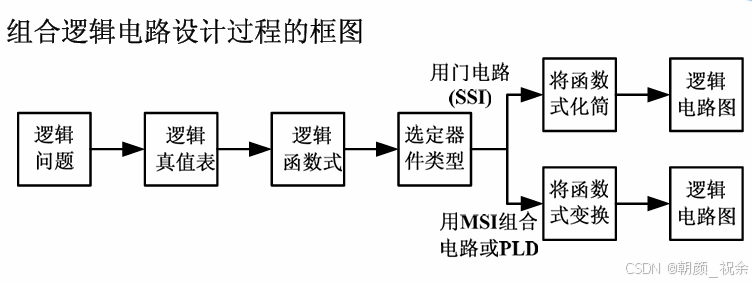

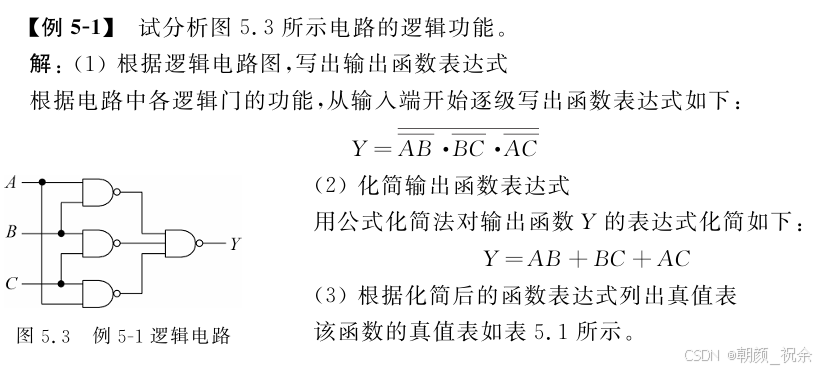

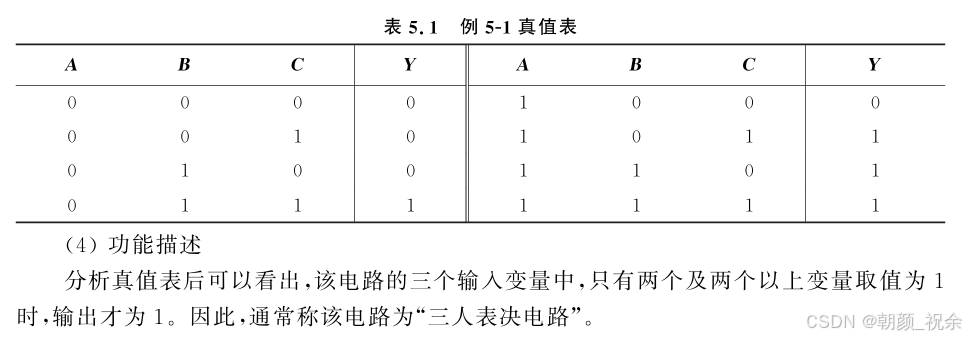

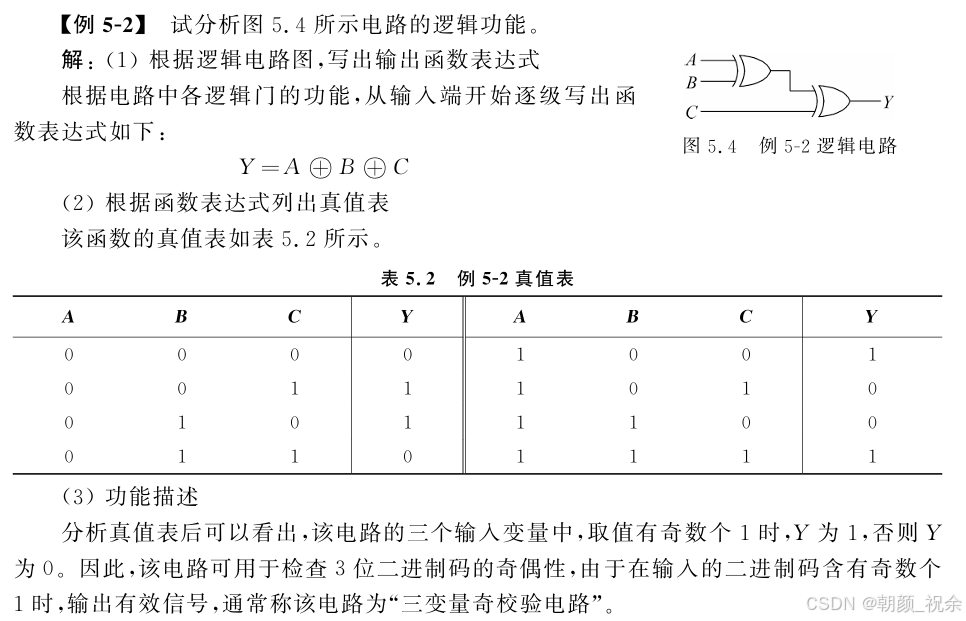

组合逻辑电路的分析方法:

给定某逻辑电路,分析其逻辑功能。分析步骤:

若干常用的组合逻辑电路模块

编码器、译码器、数据选择器、数值比较器和加法器等。

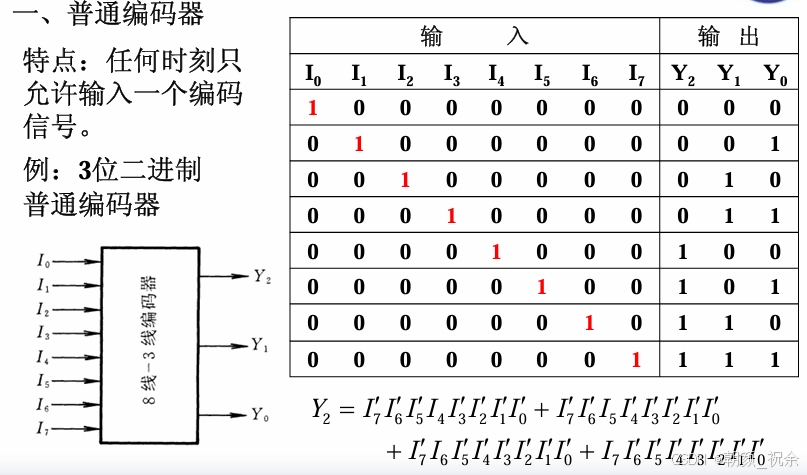

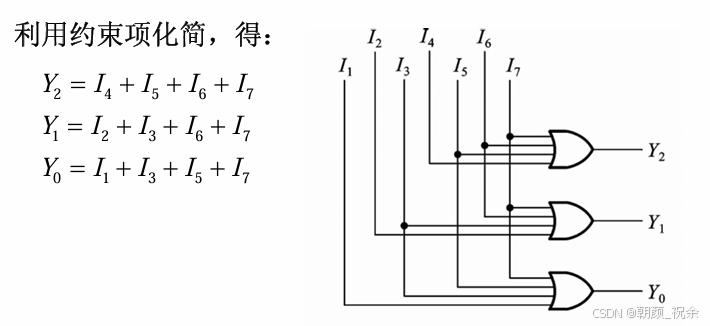

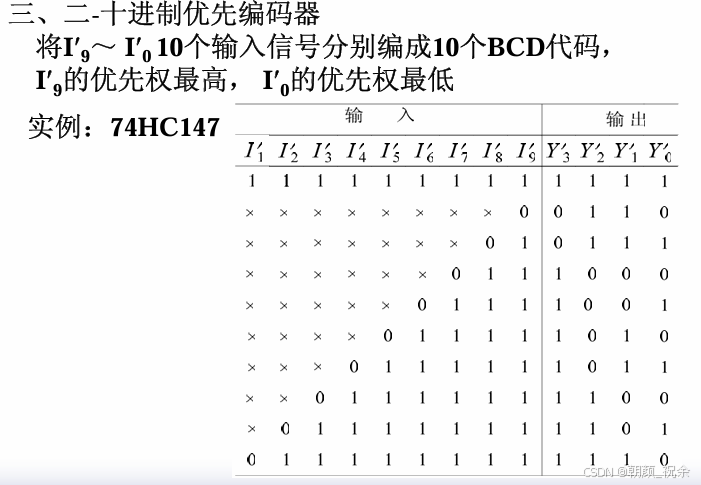

编码器

编码:将输入的每一个高、低电平信号编程一个对应的二进制代码。

编码器:具有编码功能的逻辑电路。

编码器从逻辑功能特点可分为普通编码器和优先编码器。根据进制可分为二进制编码器和二-十进制编码器。

因为n位二进制数码有2^n种状态,所以它可代表2^n组信息。人们在编码过程中一般是采用编码矩阵和编码表,编码矩阵就是在卡诺图上指定每一方格代表某一自然数,把这些自然数填入相应的方格。

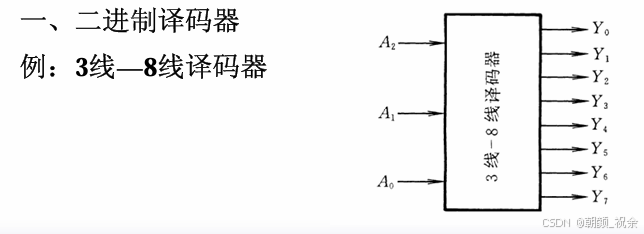

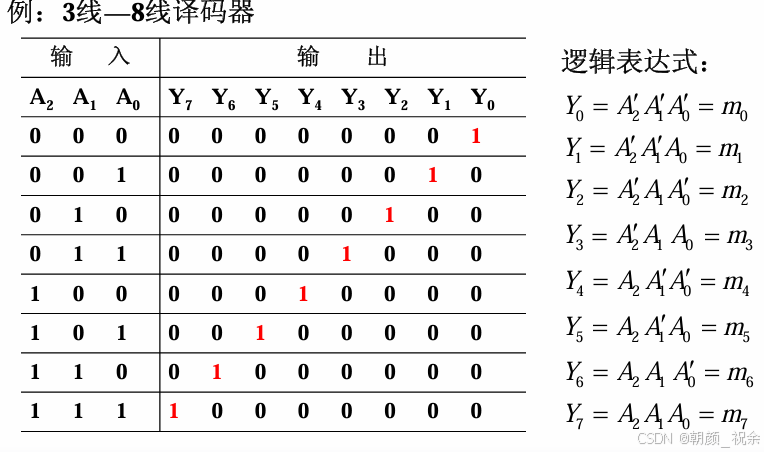

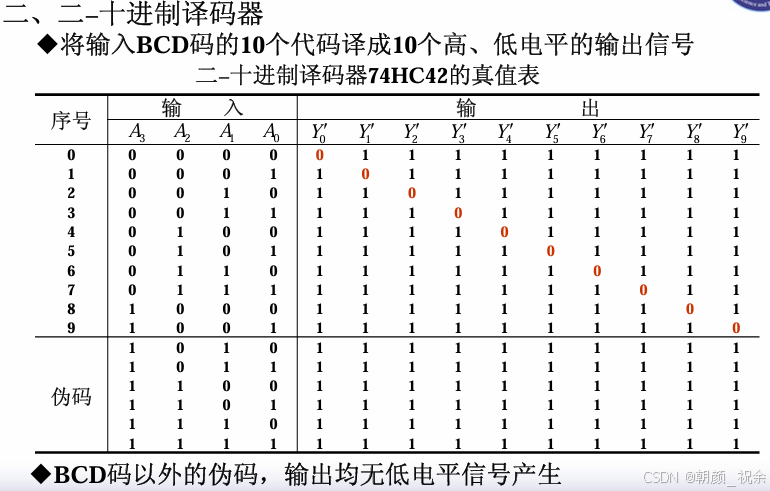

译码器

译码:将每个输入的二进制代码译成对应的输出高、低电平信号。

译码器:具有译码功能的逻辑电路。

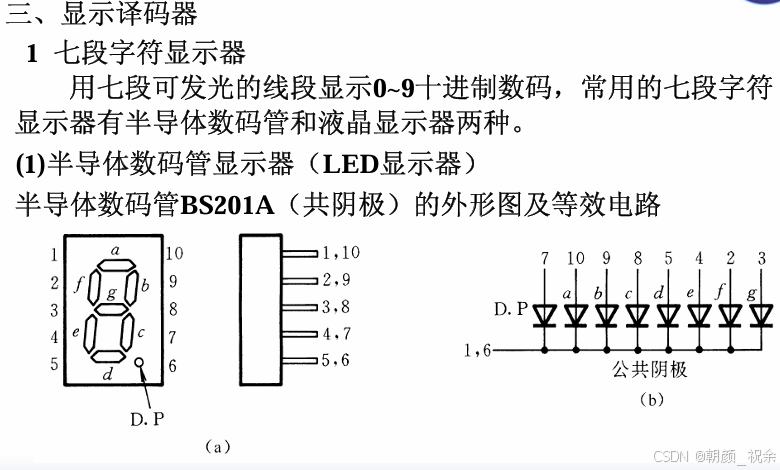

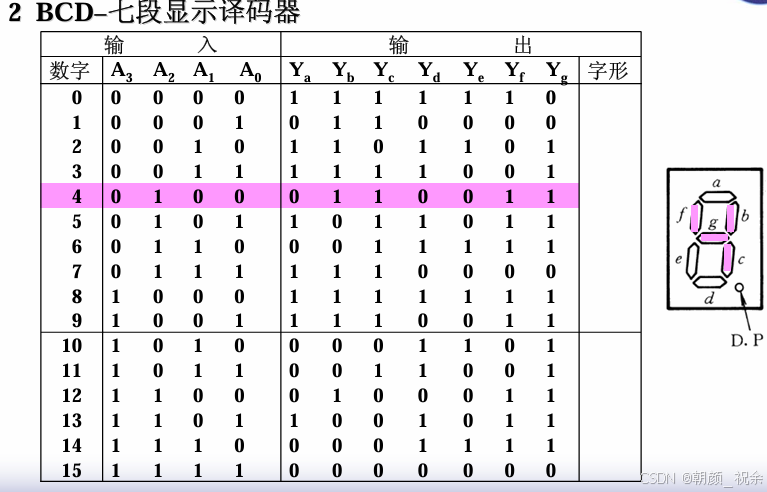

常用的译码器:二进制译码器,二-十进制译码器,显示译码器等

数据分配器

数据分配:将公共数据线上的数据送到相应的输出端。

数据分配器:实现数据分配功能的逻辑电路。带控制输入端的译码器可看成数据分配器。

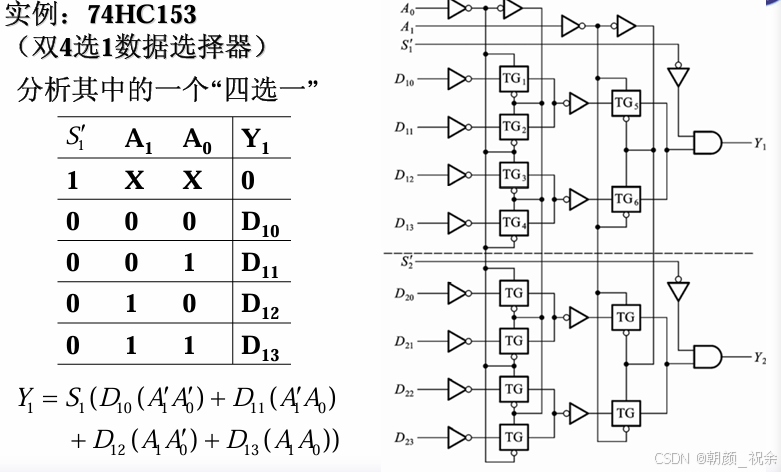

数据选择器

数据选择:在数字信号的传输过程中,从一组数据中选出某 一个送到输出端。

数据选择器:实现数据选择的逻辑电路,也叫多路开关。

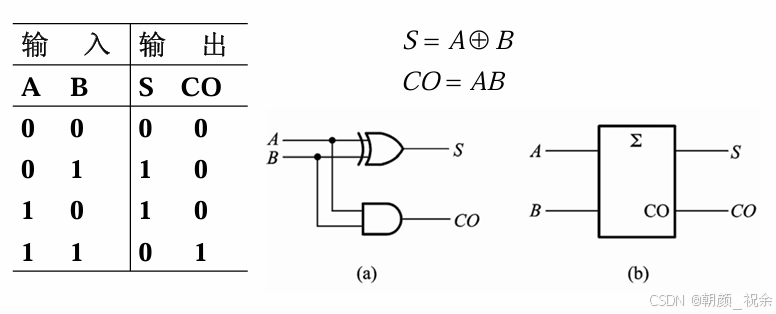

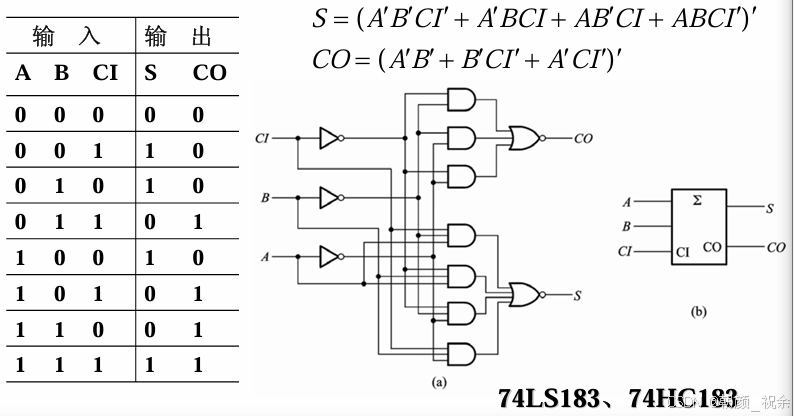

加法器

半加器:不考虑来自低位的进位,将两个1位的二进制相加。

全加器:将两个1位二进制数及来自低位的进位相加

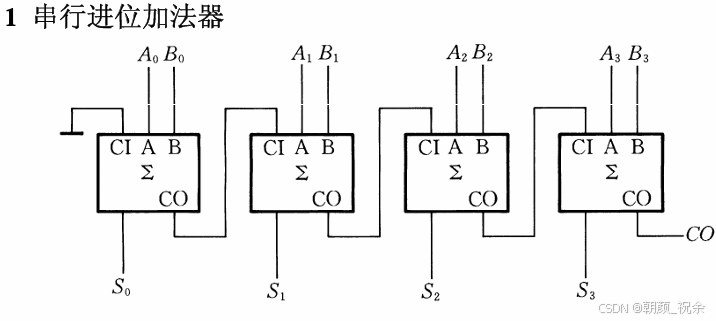

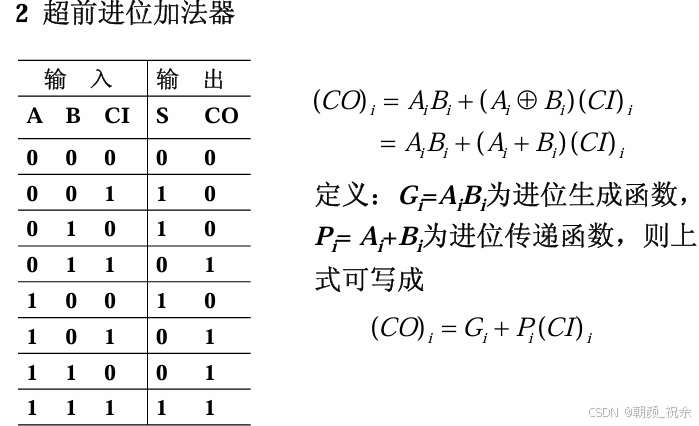

多位加法器

- 乘法器与除法器:用于执行二进制乘法和除法。

- 多路选择器(MUX):根据选择信号,选出多个输入中的一个输出。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?