1.布局流程

①模块布局

②整体布局

③叠层与阻抗

④规则设置

⑤模块扇出

⑥布局评审

2.模块布局

将功能模块定义成Group,便于整体快速移动、旋转等操作。

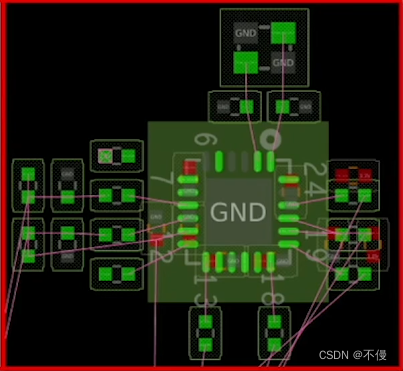

- ①以模块内主芯片为核心,以原理图为基础,按照信号连接,采取顺藤摸瓜的方式,把相关阻容等分立器件放在该芯片周围,内部器件摆放整齐、均匀。

- ②时钟电路放置:晶体和晶振与相关的IC器件靠近放置,距离≤100OMil。无源晶振必须靠近管脚,有源晶振可稍远。无源晶振时钟线可从自己底下过,有源晶振时钟线不可从自己底下过。

- ③电源电路放置:优先处理开关电源模块布局,并按期间资料要求设计。

- ④电容防止:滤波电容靠近管脚放置。

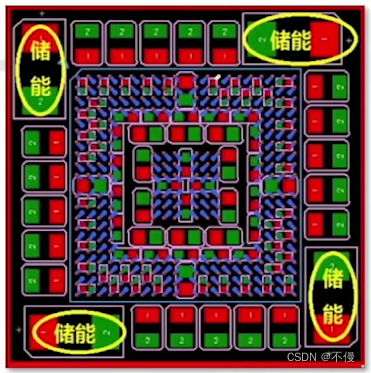

- ⑤储能电容放在芯片周围,兼顾电源管脚。

- ⑥由R\L\C组成的L型/Π型滤波电路,靠近电源管脚放置。

- ⑦串联电阻靠近源端放置,直线距离一般不超过300Mil;并联匹配电阻靠近接收端放置

直线距离一般不超过300Mil;AC电容优先放置在接收端,直线距离小于50OMil。

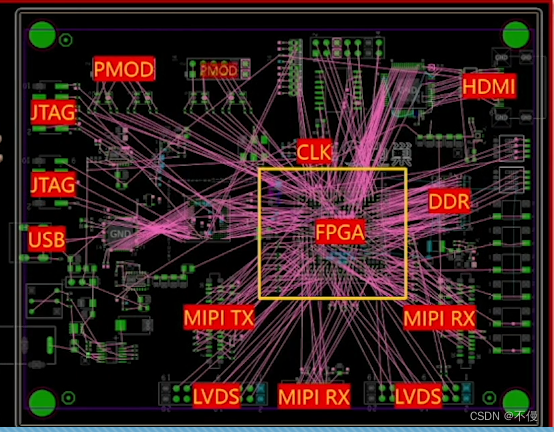

3.整体布局

- ①接口模块摆放:

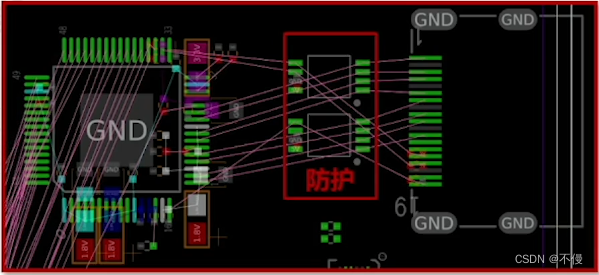

采用“先防护后滤波”的思路摆放接口处的保护器件;

按照信号流向将各接口模块电路靠近其所对应接口摆放,使对外的信号走线尽量短。

- ②核心芯片模块摆放:

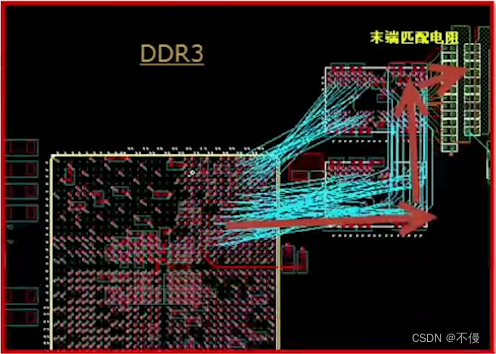

DDR1/2一般按照T型拓扑摆放,匹配电阻放在T点处;最好正反贴,同层线太长最好仿真。

DDR3/4按照Fly-By方式摆放,末端匹配电阻根据出线的方向,靠近摆放在末端存储芯片周围,匹配电阻与未端存储芯片布线长度≤50OMil。

DDR3芯片若不支持读写平衡(DDR4都支持),且时钟线与数据线布线长度误差不能控制在合理范围内,则不建议用Fly-By。DDR芯片较多,如4颗、8颗基本均使用Fly-By拓扑。

- ③电源模块摆放:

远离易受干扰的电路,如ADC,DAC,RF,时钟等电路模块,发热量大的电源模块,需要拉大与其它电路的距离,与其他模块的器件保持3mm以上的距离。

不同模块的专用电源,靠近负载模块摆放,负载为整版电源供电的模块优先摆放在总电源输入端。 - ④其它器件摆放

JTAG接口及外部接口芯片靠近板边摆放,便于插拔,有特殊指定位置除外。

测温电路靠近发热量大的电源模块或功耗最高的芯片摆放,摆放时确定正反面。

光耦、继电器、隔离变压器、共模电感等隔离器件的输入输出模块分开摆放,隔离间距40Mil以上。

热敏感元件(电解电容、晶振)远离大功率的功能模块、散热器、风道末端,器件丝印边沿距离>400Mil。 - ⑤布局优化:

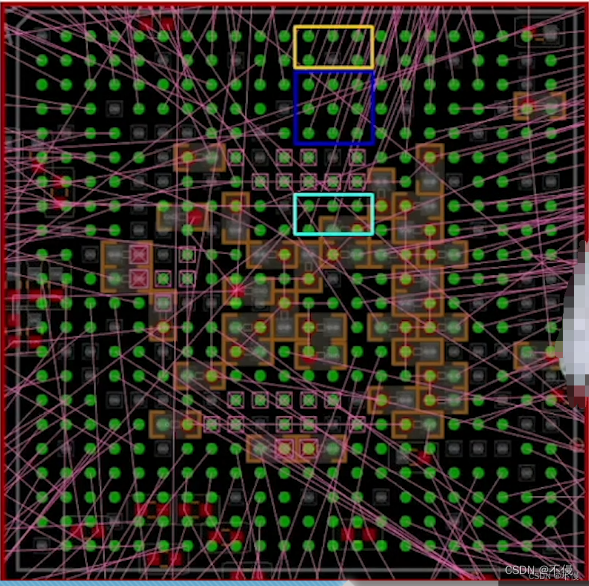

通过飞线显示连接关系,根据信号流向图调整核心芯片的方向,优先保证关键信号(时钟线和高速线,模拟/射频)顺畅、最短。

信号交叉解决:(1)打孔、换线序;(2)芯片换层。

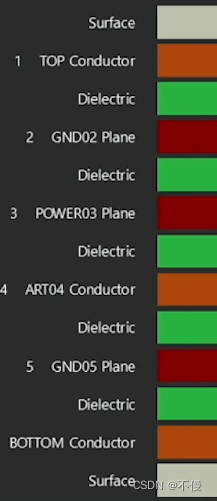

4.叠层与阻抗

4.1设计参数确认

- 审阅《PCB Layout资料及要求》;

- 确认填写信息完整、正确;

- 板厚与要求一致,注意PCl或PCIE板厚1.6mm等特殊板卡板厚要求

- 设计要求无法满足时,需和工艺、SI等及时沟通

4.2叠层评估

评估走线层数:

以设计文件中飞线最密集的区域为主要参考,评估走线层数,一般为BGA封装的器件或者排数较多的接插件。

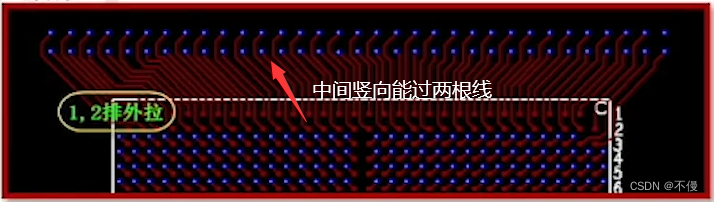

以信号管脚为6排的1.0mm BGA*在top层,BGA内两孔间只能走一根信号线为例,最少布线层数的评估可以参考以下几点:

(1)外围及次外围信号需换层布线的过孔可以延伸至BGA外(一般在BGA本体外扩5mm的禁布区范围内),此类过孔要摆成两孔间穿两根信号线的方式。

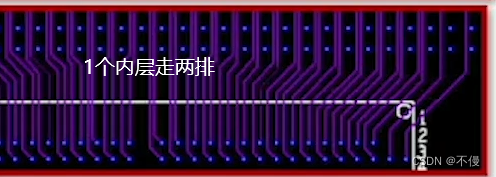

(2)往里的第3、4排可共用1个内层出线。

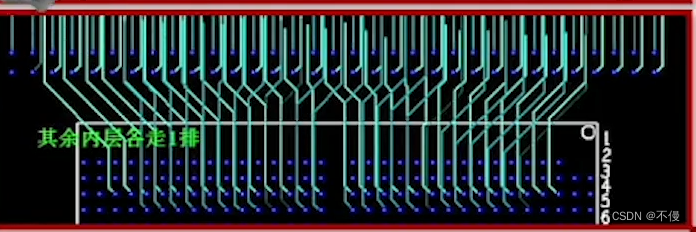

(3)再往里的第5、6排则需要2个内层出线。

(4)然后根据电源和地的分布情况,结合Bottom层走线,最多可以减少1个内层。

(5)结合以上4点,最少要用2个内走线层完成出线。

这个1.0mm Pitch FPGA最少需要多少个布线层(含表底层)?

选用钻孔直径10mil、焊盘直径18mil的过孔

过孔边缘间距=39.37-18=21.37mil

如果线宽、间距用4mil的话

21.37/4~5,即两个过孔之间可以过2根线

评估电源平面层数:

- 分析单板电源总数与分布情况,优先关注分布范围大,及电流大于1A以上的电源。

- 通常情况下:如果板内无BGA封装的芯片,一般可以用一个电源层处理所有的电源;如果有BGA封装的芯片,主要以BGA封装芯片为评估对象,如果BGA内的电源种类<3种,用一个电源平面,如果>3种,则使用2个电源平面,如果>6则使用3个电源平面,以此类推.

- 对于电流<1A的电源可以采用走线层铺铜的方式处理。

- 对于电流较大且分布较集中或者空间充足的情况下采用信号层铺铜的方式处理。

地平面层数的评估:

在确定布线层数和电源层数的基础上,满足以下叠层原则: - 叠层对称性

- 阻抗连续性

- 主元件面相邻层为地层

- 电源和地平面紧耦合

结合评估出的走线层数和平面层数,高速线优先靠近地层的原则进行层叠排布。

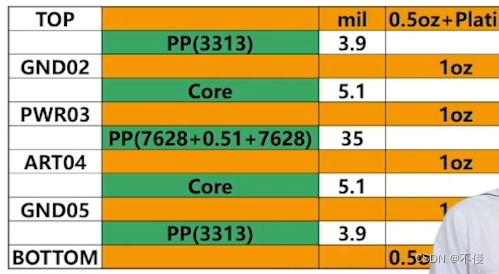

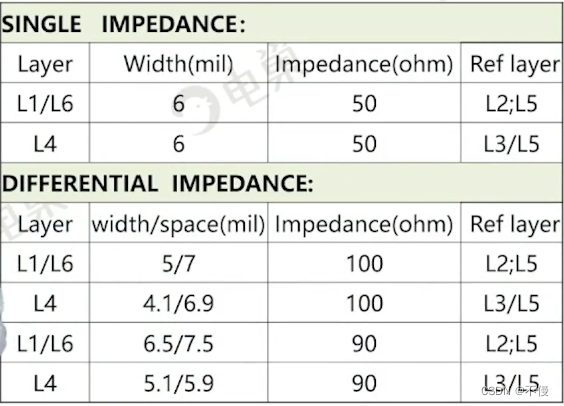

4.3阻抗计算

- 确认阻抗类型:

常规阻抗:单端50欧姆,差分100欧姆。

特殊阻抗:USB接口差分90欧姆。 - 按照《PCB Layout资料及要求》中的工艺要求、层叠排布方案和阻抗要求,确定层厚与阻抗线宽。

参考以下设计原则:

信号层夹在电源层和地层之间时,信号层靠近地层。

差分线间距≤2倍线宽。

相邻信号层间距拉大。

不同线宽、间距和阻抗值的走线需分别描述,且差分线与单线的线宽要有所区别。

- 阻抗计算:Polar SI9000

- 叠层设计:Polar Speedstack Stack Up Builder(可以将叠层导出为IPC2581数据格式,allegro支持该格式的导入)

- 将工艺参数、叠层参数和阻抗线宽等数据填写在《PCB加工工艺要求说明书》中

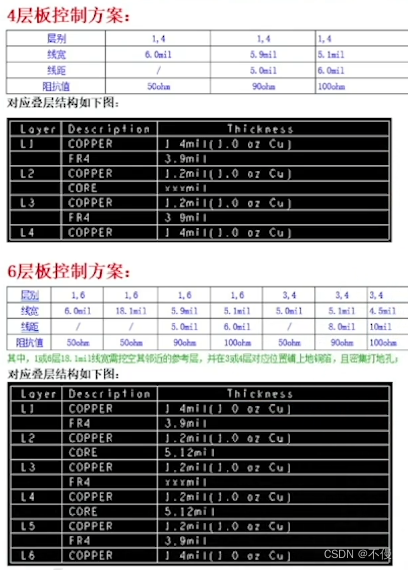

常用模板举例:

5.总结

- 布局思路

满足DFx等生产要求

关注SI/PI/EMC、、、等电气要求

先整体、后局部、再回归整体的策略 - 布局实战

模块内短平快

用好复用,省时省力、整齐美观

模块间相对独立,做好通道规划

参考资料来自电巢,侵删。

本文详细介绍了PCB设计中的布局流程,包括模块布局、整体布局、叠层与阻抗计算等内容。强调了信号线的合理规划与电源管理的重要性,提供了布局优化的方法与技巧。

本文详细介绍了PCB设计中的布局流程,包括模块布局、整体布局、叠层与阻抗计算等内容。强调了信号线的合理规划与电源管理的重要性,提供了布局优化的方法与技巧。

1655

1655