对于辐射噪声,其噪声基本来源于周围环境或板上的某些数字信号走线。所以我们减少辐射噪声的主要考虑角度是尽量避免板上信号的耦合。在 PCB板上,基本上有三类容易接受辐射的噪声:第一是单端高阻输入端;第二是环状走线;第三就是长走线。

a. 环状走线的影响

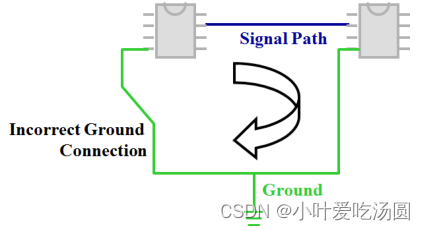

如下图所示为一个典型的地线构成了一个环路。我们看到环路上有一些电子器件,是否这样就不再构成一个环路了呢?其实不然,这些元器件也可以看成是一个个环路。PCB上环状走线的影响相当于电感,它产生电磁噪声,同时也接收电磁噪声。

b. 长走线的影响

长走线造成辐射噪声的原因很好理解:在 PCB上的长走线可以看做一个天线。同样的,没有连接的空走线同样可以看做天线。这个原理在现实生活中也会感受到,例如现在的手机,在用作收音机时会利用长长耳机线作为接收天线。我们在进行电路设计时,为避免该类影响,无论是模拟还是数字信号线应尽可能地短。电路受到多大的影响主要由周围环境决定,而短导线可以将板上所接收到的影响,也就是实际表现出来的噪声减少到最小。通过合理的布局布线,板上信号的耦合实际上是可以避免的。特别需要注意的是在一些放大器或者 ADC的输入端,由于输入阻抗往往较大,这些位置对耦合噪声更加敏感。

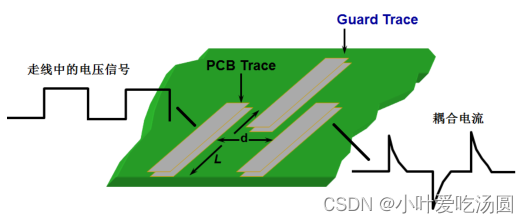

此外,还需要特别注意的是板上信号线之间信号的耦合和影响。尤其是当相邻走线为迅速变换的电压信号,例如数字信号或时钟信号。如下图所示,我们可以看到,当一根走线为快速变化的电压信号时,相邻的平行走线中会耦合出电流噪声,这种耦合电流噪声在数字走线中可能不会产生较大的影响,毕竟噪声大小有限,不会越过数字信号 0/1的门限;但是在一些模拟走线上,当这些噪声电流流入高阻抗结点时,就会产生可观的噪声(和输入的小信号做比较),例如运放器件的输入端,会对精密电路产生较大的影响。

在这种情况下,耦合的电流可以通过下列公式计算得到:![]()

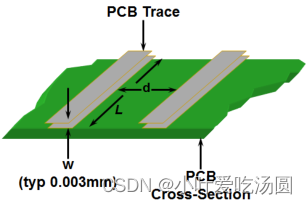

其中,C为两个相邻导线之间构成的等效电容大小,如下图所示,长度为 L的导线和与其相邻d的导线之间构成的电容大小为:![]() 。其中,w为 PCB走线的厚度;L为 PCB走线的长度;d为两条 PCB走线之间的距离;eo为空气的介质常数;er为 PCB面板材料的相对介质常数。

。其中,w为 PCB走线的厚度;L为 PCB走线的长度;d为两条 PCB走线之间的距离;eo为空气的介质常数;er为 PCB面板材料的相对介质常数。

由上面两个公式可以看出,减小耦合电流最直接的方法是减小平行走线构成的等效电容,而该电容的大小主要由两条平行走线的长度和之间的距离决定,因而可以通过避免数字信号与模拟信号平行走线,缩短平行走线长度,同时增加平行走线间的距离的方法来减小耦合的电流。另外对于相邻走线间的耦合,第三张图供了另一种减少噪声的方法:在两条走线之间增加一个对地保护走线,这样避免了两条走线间信号的直接耦合。

通过器件的重新选择,即选择小阻值的电阻同时选择较小 1/f噪声的运放来减少器件噪声;此外,在 PCB布线上,采取去除多余走线,以及环状走线,减少数字电路和模拟电路间的耦合,使用更短的走线等方法来抑制辐射噪声,下图所示。

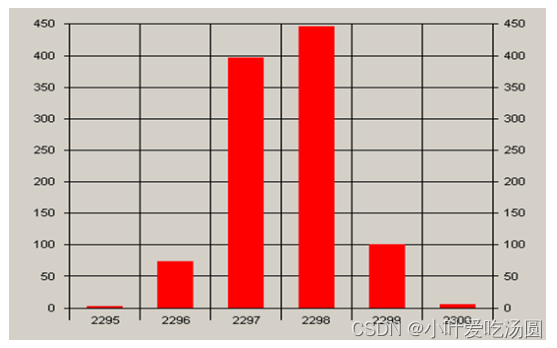

这时,我们发现 AD采样的结果较最初发生了很大的改善:同样采样 1024个点,仅得到 6个不同的数据点。同理,ADC的有效位数为 12bit-log2(6)=12-2.6=9.4bit。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?