2.1 RV32I的程序员模型

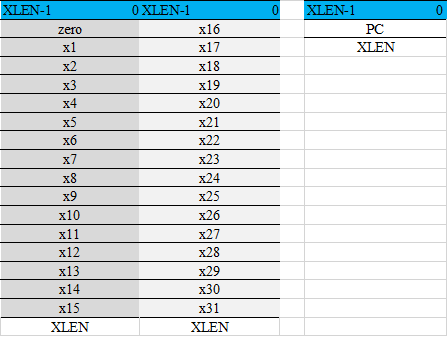

下图显示了RV32I的非特权级寄存器。

共32个寄存器,每个位宽为32bit,即XLEN=32bit。

寄存器0是硬件连线的,所有位都是零。

寄存器1~31存储的值被各种指令解释为布尔值集合、二进制补码表示的有符号二进制整数、或无符号二进制整数。

还有一个额外的非特权寄存器PC,用于保存当前指令的存储地址。

在RV32I中,没有专用的堆栈指针寄存器SP或者返回地址链接寄存器LR。指令编码允许任何寄存器用于此目的。

然而,**标准软件调用约定使用X1作为LR,使用X2作为SP,使用X5作为备用LR。**硬件可能会使用X1或X5来加速函数调用和返回,见JAL和JALR指令描述。

16比特压缩指令倾向固定使用X1作为LR,X2作为SP。使用其他寄存器的软件也可以正常运行,但可能需要更大的代码尺寸。

可用的架构寄存器数量对代码大小、性能和能耗有很大影响。虽然16个寄存器对于编译代码的整数ISA来说足够了,但是16位的16个寄存器不能编码一个完整的ISA,不支持3地址格式的指令,虽然2地址格式的是可以的,但是它会增加指令数量并降低效率。我们希望避免使用中间指令大小(例如Xtensa的24位指令)来简化基础硬件实现。更多整数寄存器也有助于提高高性能代码的性能,可以广泛使用循环展开,软件流水线和缓存平铺等。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?