1、开发环境

(1)KeilMDK:V5.38.0.0

(2)STM32CubeMX:V6.8.1

(3)MCU:STM32F407ZGT6

2、无源蜂鸣器简介

无源蜂鸣器内部没有振荡源,需要采用一定频率的方波才能驱动发声。详情参开以下文章。

3、实验目的&原理图

3.1、实验目的

(1)使蜂鸣器发出人耳可听到的声音。

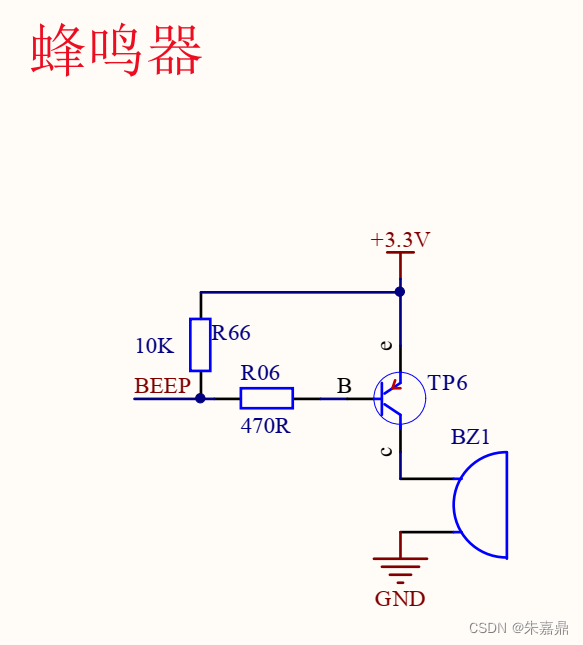

3.2、原理图

(1)BEEP接PF8。

(2)三极管的作用是因为单片机引脚驱动能力不够,通过BEEP引脚控制三级管的开关。

4、STM32CubeMX创建工程及配置

4.1、新建工程

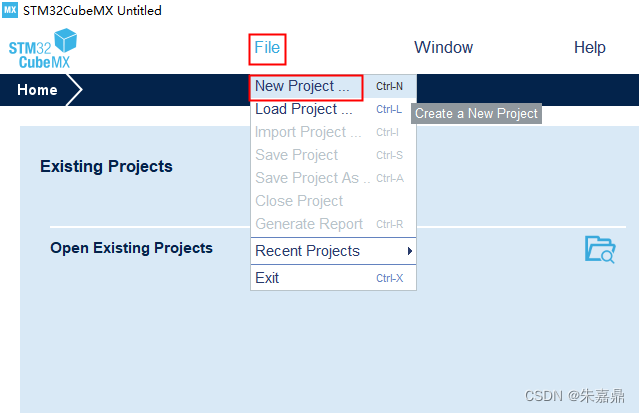

(1)打开STM32CubeMX软件。

(2)点击File→NewProject。

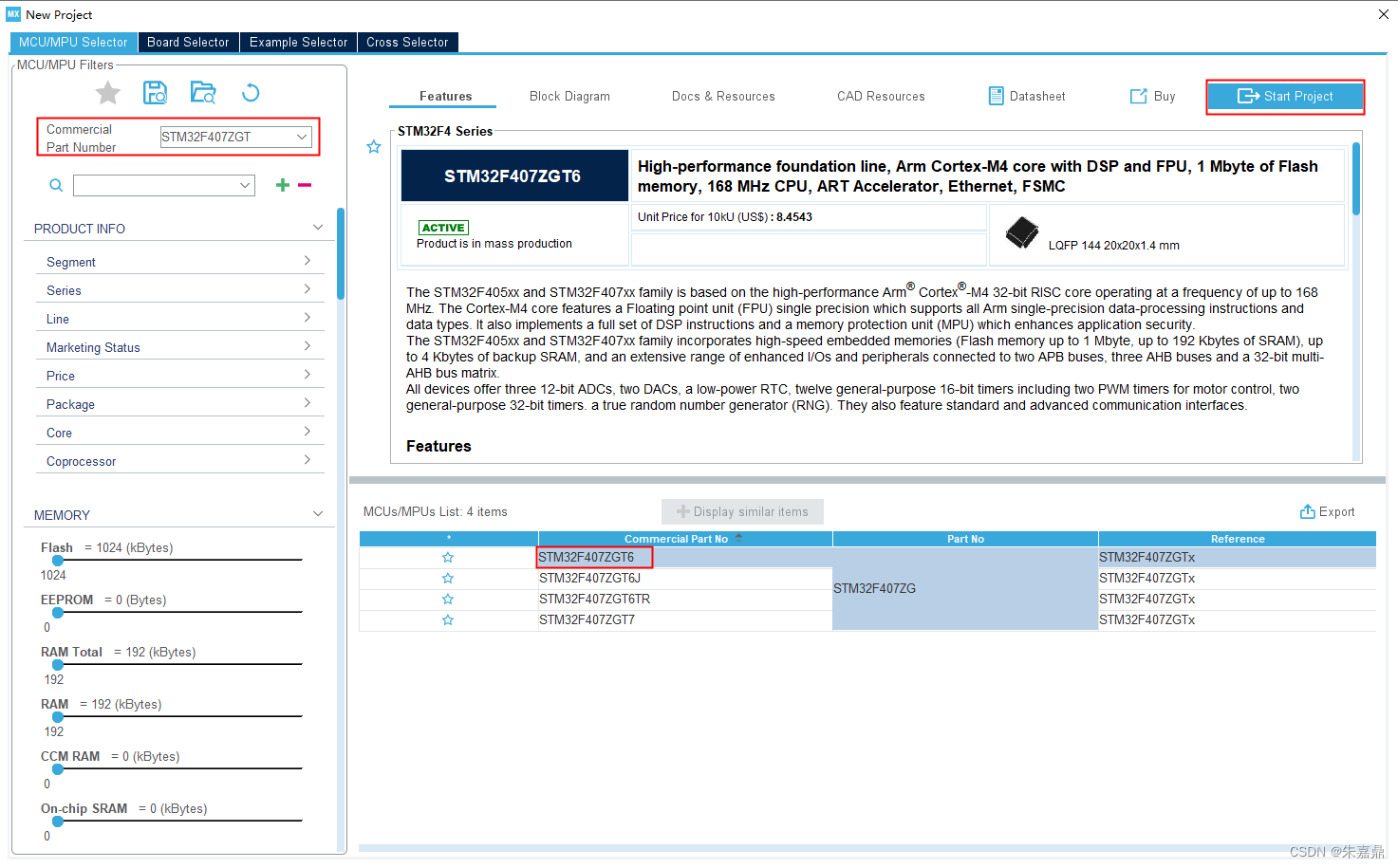

(3)Commercial Part Number(商用部件号)处输入MCU型号,然后选择正确的单片机型号,点击Start Project(开始项目)。

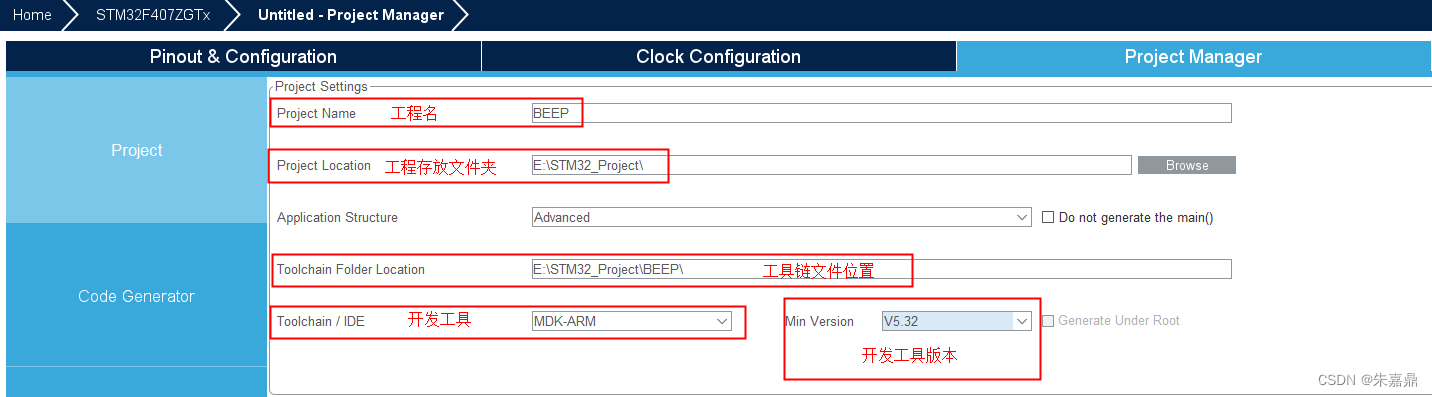

(4)配置工程名、工程存放文件等。

点击Project Manager(项目经理)进行如下配置。

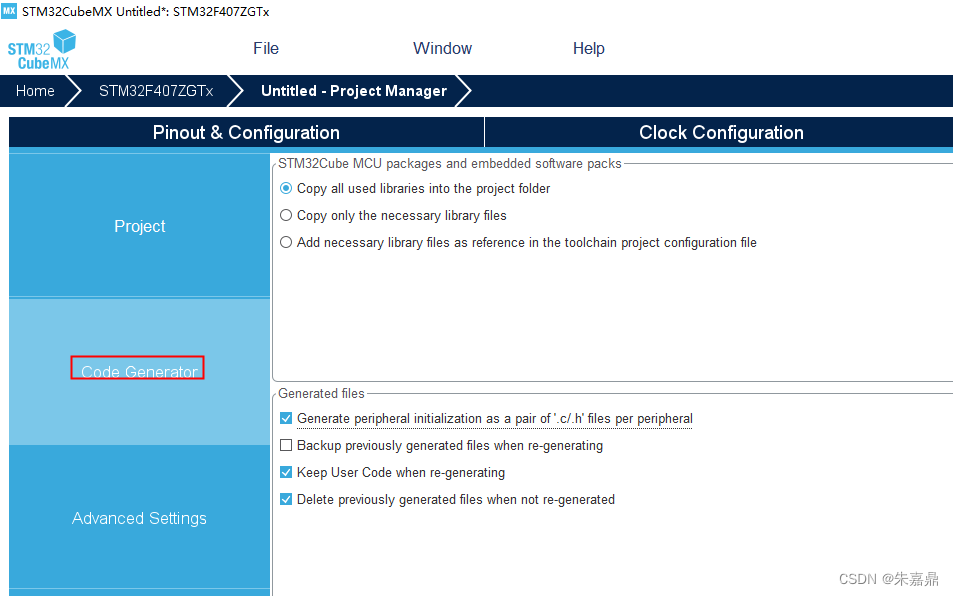

点击Code Generator(代码生成器)进行如下配置。

(5)点击GENERATE CODE生成KeilMDK工程。

4.2、配置时钟和GPIO

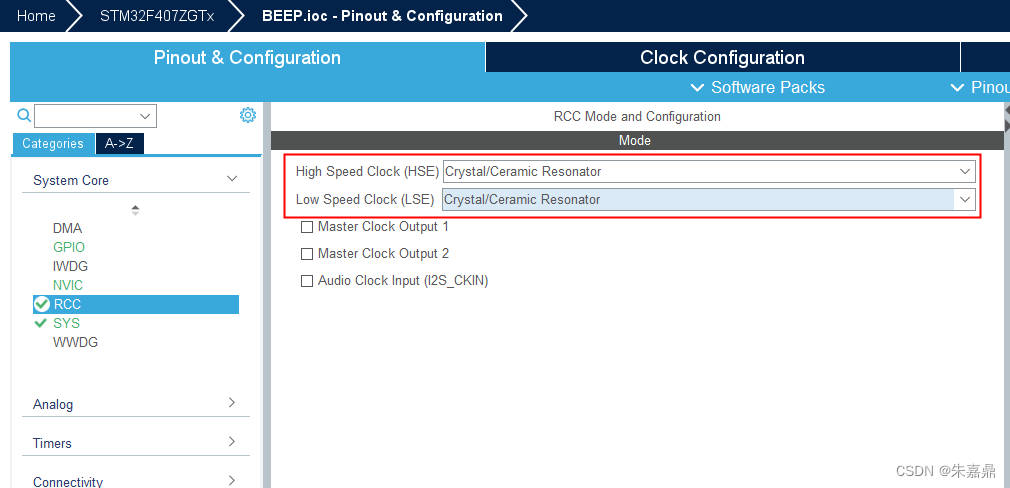

(1)HSE、LSE时钟源选择

- HSE:高速外部时钟源

- LSE:低速外部时钟源

- Disable:禁用

- BYPASS Clock Source:旁路时钟源

- Crystal/Ceramic Resonator :水晶/陶瓷共振器

- 一般选择水晶陶瓷共振器

- 旁路时钟源就是由外部给定一个时钟信号,一般用于作为同步时钟。

- 水晶/陶瓷共振器:指外接晶振,经过内部振荡电路产生时钟。

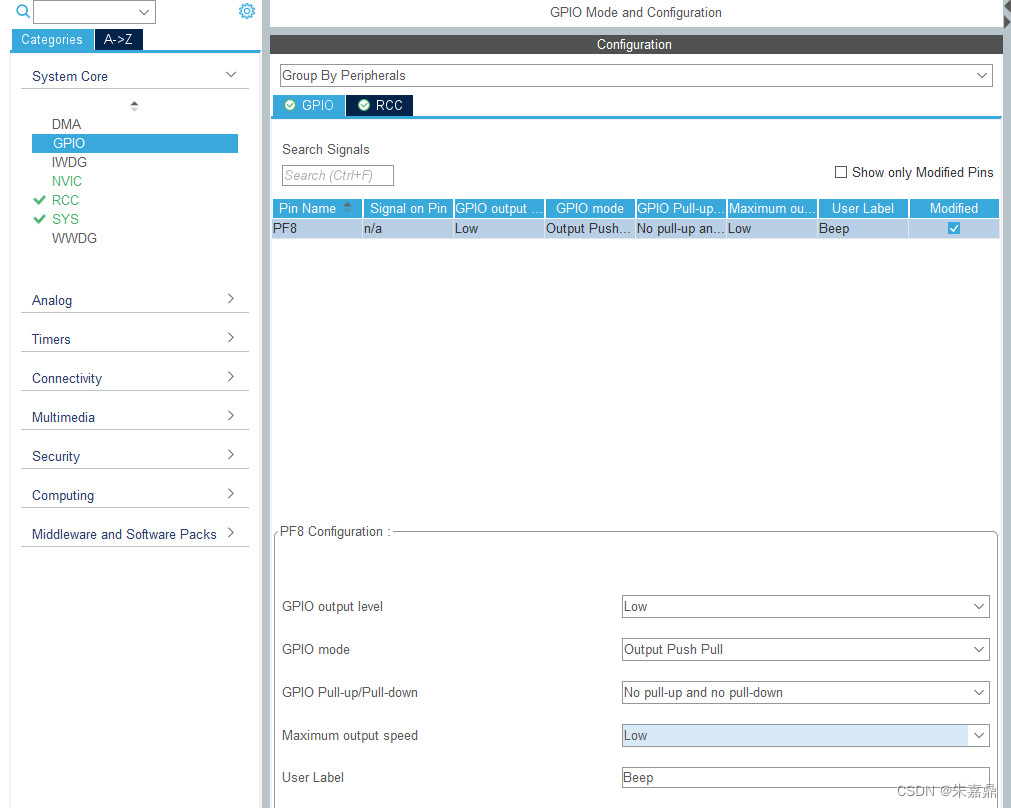

(2)GPIO配置如下

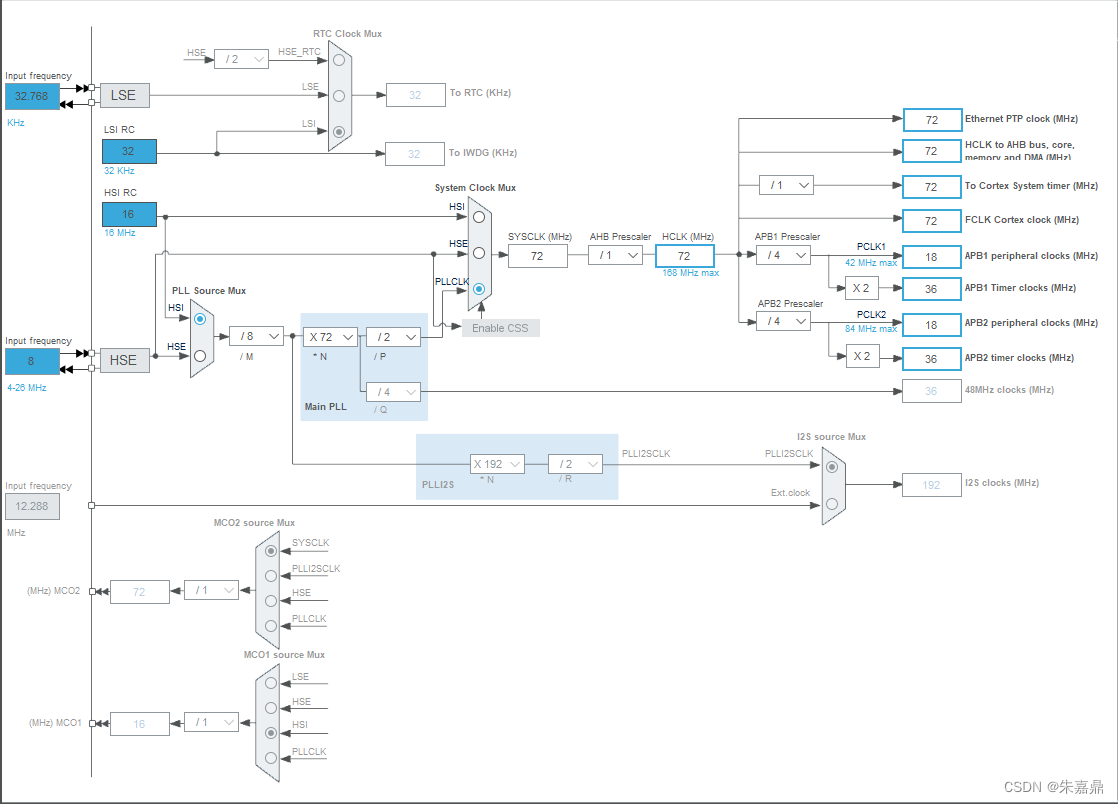

(3)时钟树配置

(4)配置完需要重新点击GENERATE CODE更新KeilMDK代码。

(4)配置完需要重新点击GENERATE CODE更新KeilMDK代码。

5、KeilMDK软件编写部分

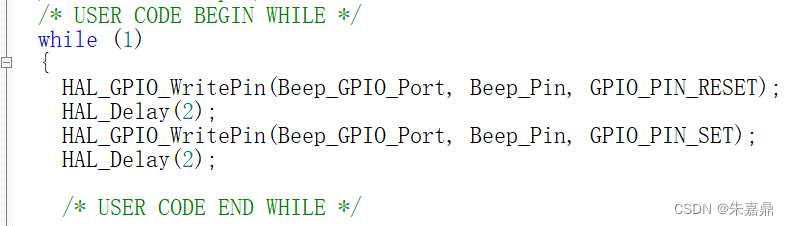

5.1、程序编写

HAL_GPIO_WritePin(Beep_GPIO_Port, Beep_Pin, GPIO_PIN_RESET);

HAL_Delay(2);

HAL_GPIO_WritePin(Beep_GPIO_Port, Beep_Pin, GPIO_PIN_SET);

HAL_Delay(2);

5.2、完整工程下载地址

(1)完整工程存储在码云。

(2)STM32_优快云: 优快云中STM32专栏的所有示例代码

该文介绍了如何使用KeilMDKV5.38.0.0和STM32CubeMXV6.8.1配置STM32F407ZGT6微控制器来驱动无源蜂鸣器。通过STM32CubeMX设置时钟和GPIO,以及编写HAL_GPIO_WritePin函数实现蜂鸣器的启停控制。实验目的是使蜂鸣器发出声音,三极管用于增强驱动能力。

该文介绍了如何使用KeilMDKV5.38.0.0和STM32CubeMXV6.8.1配置STM32F407ZGT6微控制器来驱动无源蜂鸣器。通过STM32CubeMX设置时钟和GPIO,以及编写HAL_GPIO_WritePin函数实现蜂鸣器的启停控制。实验目的是使蜂鸣器发出声音,三极管用于增强驱动能力。

1468

1468

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?