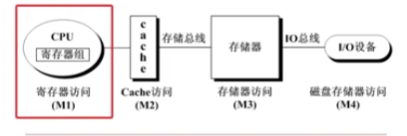

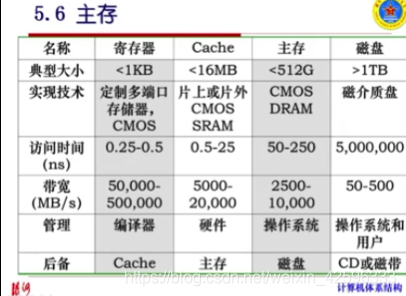

存储层次的性价比特征

速度越快,每位价格就越高

容量越大,每位价格就越低

容量越大,速度越慢

主存的主要性能指标:延迟和带宽

以往:Cache主要关心延迟,I/O主要关心带宽

现在:Cache关心两者

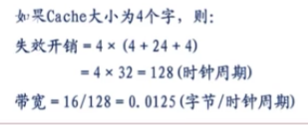

本节讨论几种提高主存性能的存储器组织技术,在下面的讨论中,以处理Cache失效为开销例来说明各种存储器组织结构的好处。

为了减少失效开销Tm,应该:

减少主存延迟

提高主存带宽

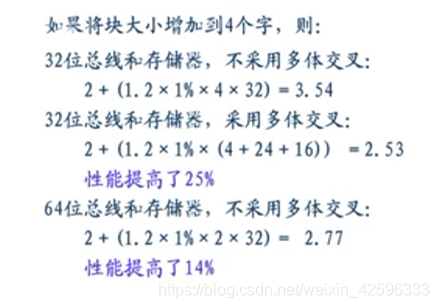

增加Cache块大小能利用主存带宽增加所带来的好处。

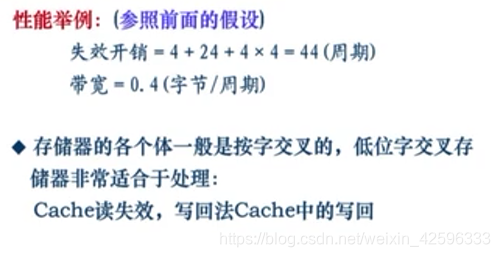

假设基本存储器结构的性能为:

送地址需4个时钟周期

每个字的访问时间为24个时钟周期

传送一个字的数据需4个时钟周期

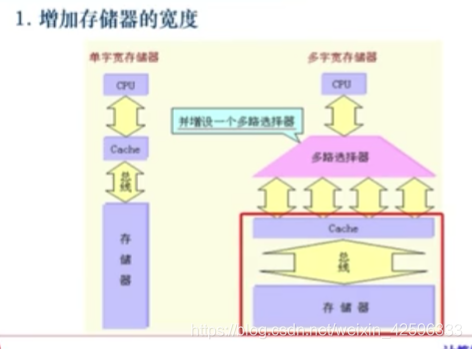

怎么提升存储器的性能呢?

存储器组织技术

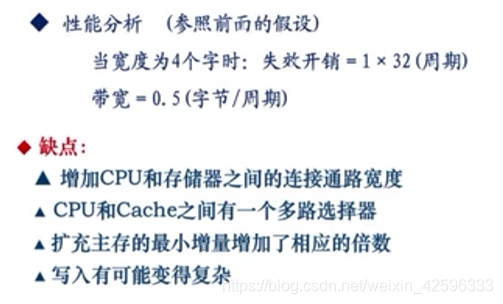

1.增加存储器的宽度

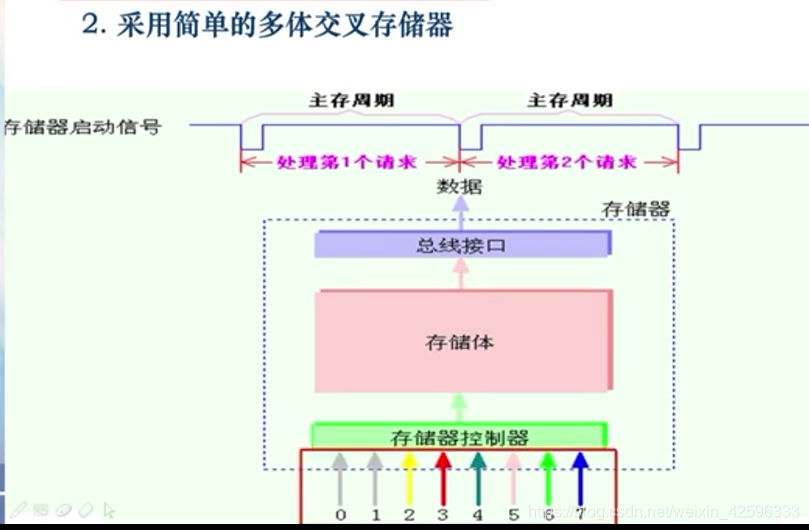

2.采用简单的多体交叉存储器

不采用多体交叉的情况:(传统)

采用多体交叉:

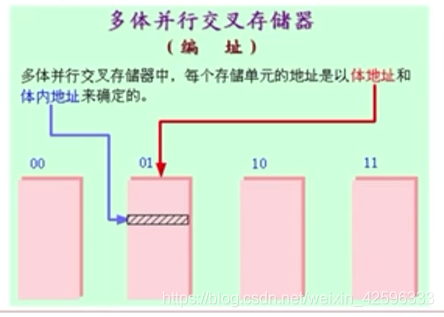

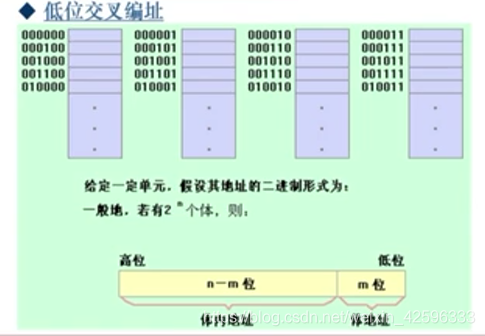

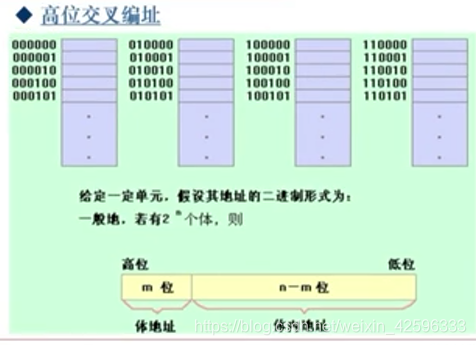

高位交叉与低位交叉编址

低位交叉编址能很好的发挥并行性。

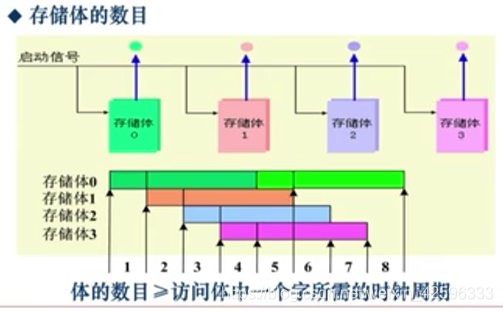

怎么很好的发挥低位编址的并行性呢?

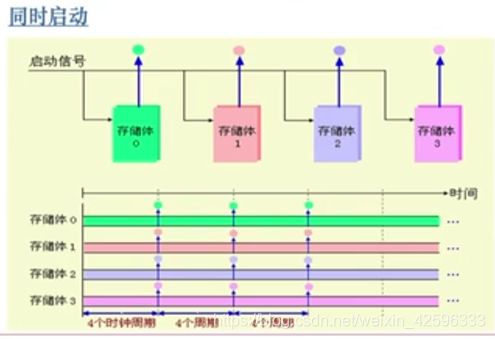

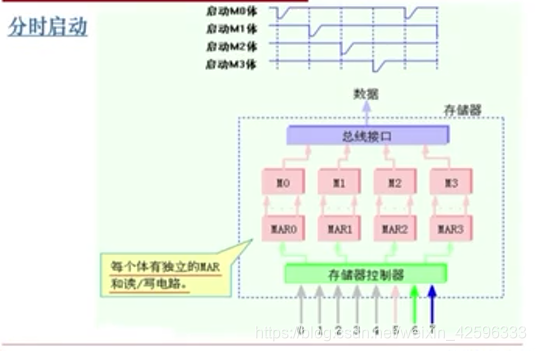

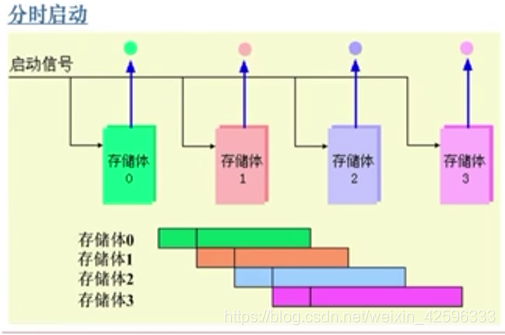

同时启动 和 分时启动

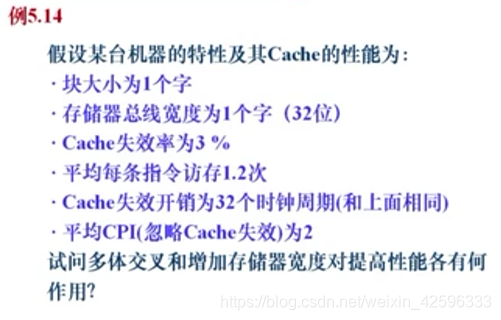

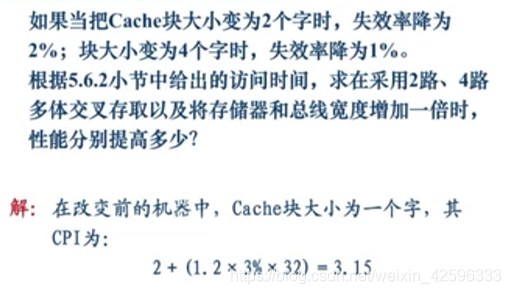

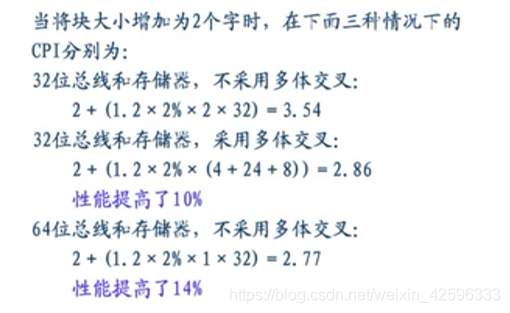

例题分析

存储体的数目方面

3.独立存储体

采用交叉存储器,一次只能发送一个地址。

独立存储体:设置多个存储控制器,使多个体能独立操作,以便能进行多个独立的访存

(1)每个体有独立的地址线

(2)非阻塞Cache与多体结构

Cache失效时仍允许CPU进行其它的访存。这样的设计对于独立多体结构才有意义

IO访存

(3)体和超体

超体:独立存储体里面还有存储体

存储器芯片技术

1.DRAM和SRAM

容量:4~8:1

存储周期:8~16:1

价格:1:8~16

一般来说,主存:DRAM Cache:SRAM

Amdahl经验规则:

为了保持系统平衡,存储容量应随CPU速度的提高而线性增加(4/3y)

2.DRAM芯片优化技术

芯片内部优化技术是提高主存系统性能的一个重要方面。

快页模式:内部缓冲一行的数据以便进行列访问。

SDRAM : Synchronous DRAM: DRAM接口增加一个时钟信号可使DRAM能针对一个请求连续同步的传输多个数据而不需同步开销。

DDR(double data rate ): 在DRAM时钟的上沿和下沿都进行数据传输,可把数据传输率提高一倍。

总结:

DDR技术规定的标准电压为2.5V,DDR2技术的电压将为1.8V,工作频率范围为266MHz~400MHz,DDR3的电压将为1.5V,最大工作频率为800MHz.

存储器优化技术都是通过增加少量逻辑来开发DRAM内部潜在的高带宽,这种优化代价很小,却能使带宽显著提高。

2648

2648

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?