正文:客户反馈SPI波形不对,因此需要结合示波器分析SPI波形对应模式是否存在异常

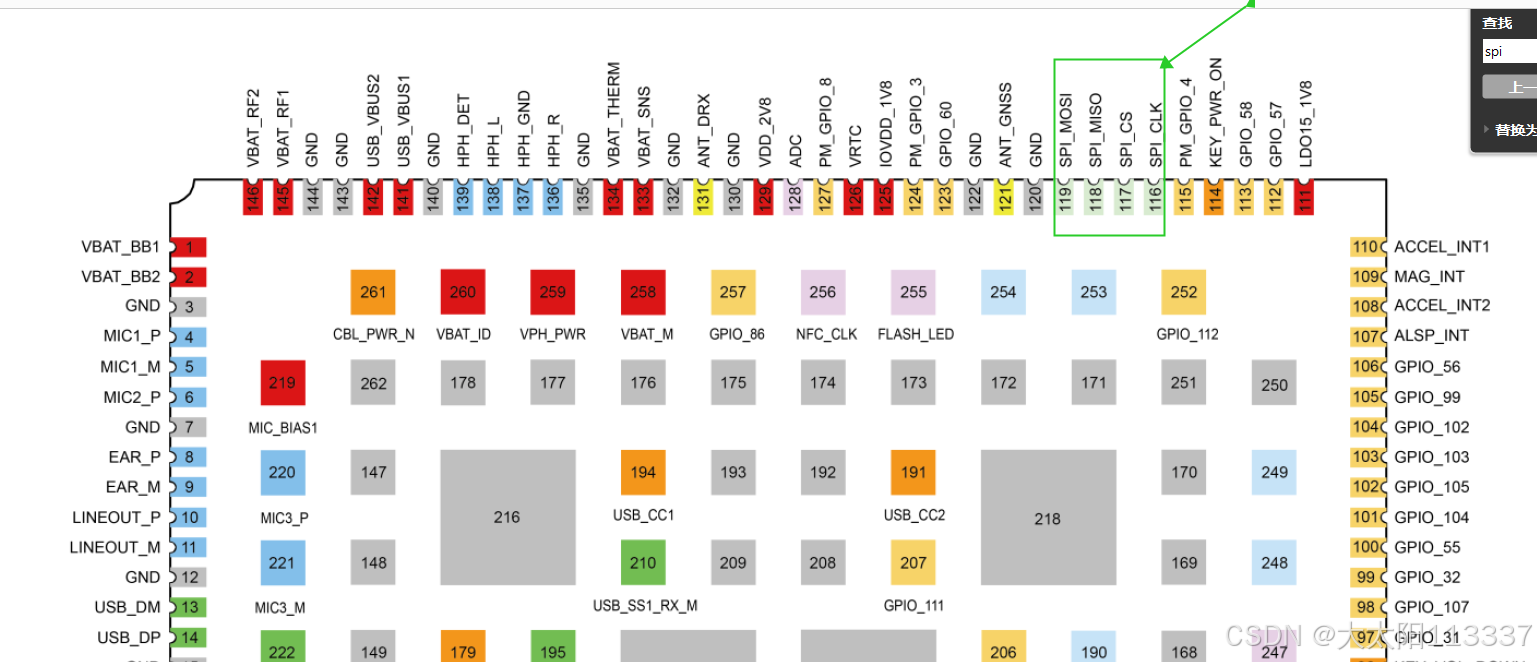

1:使用自己ADP板实测其硬件连接如下

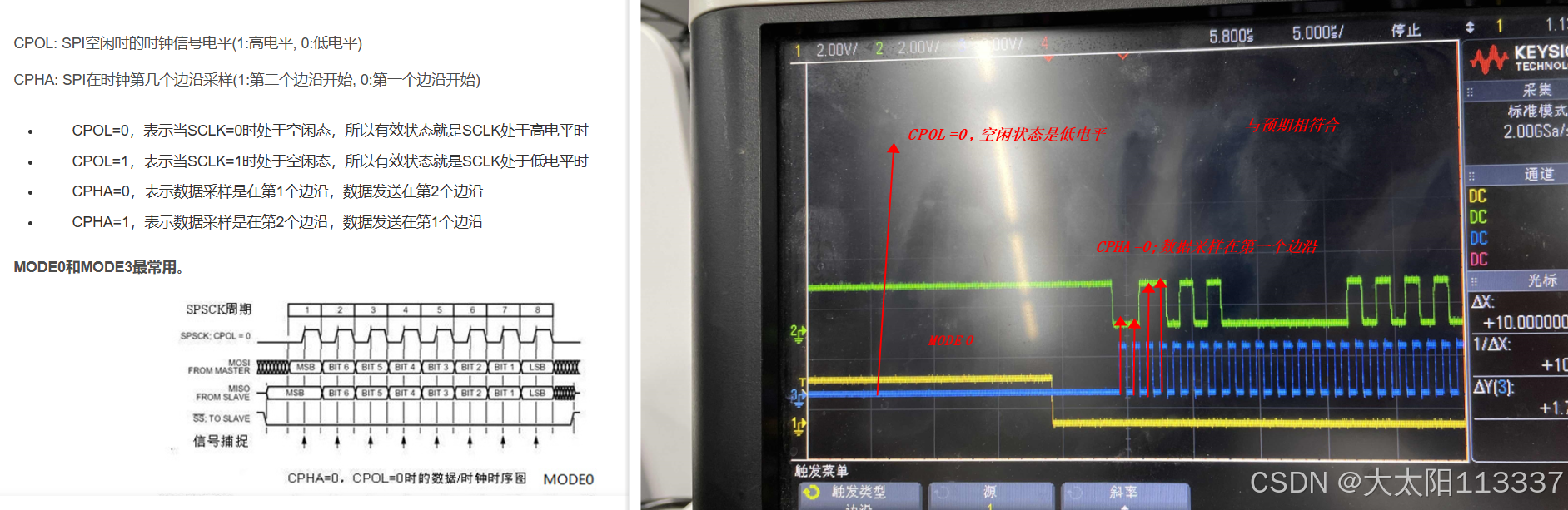

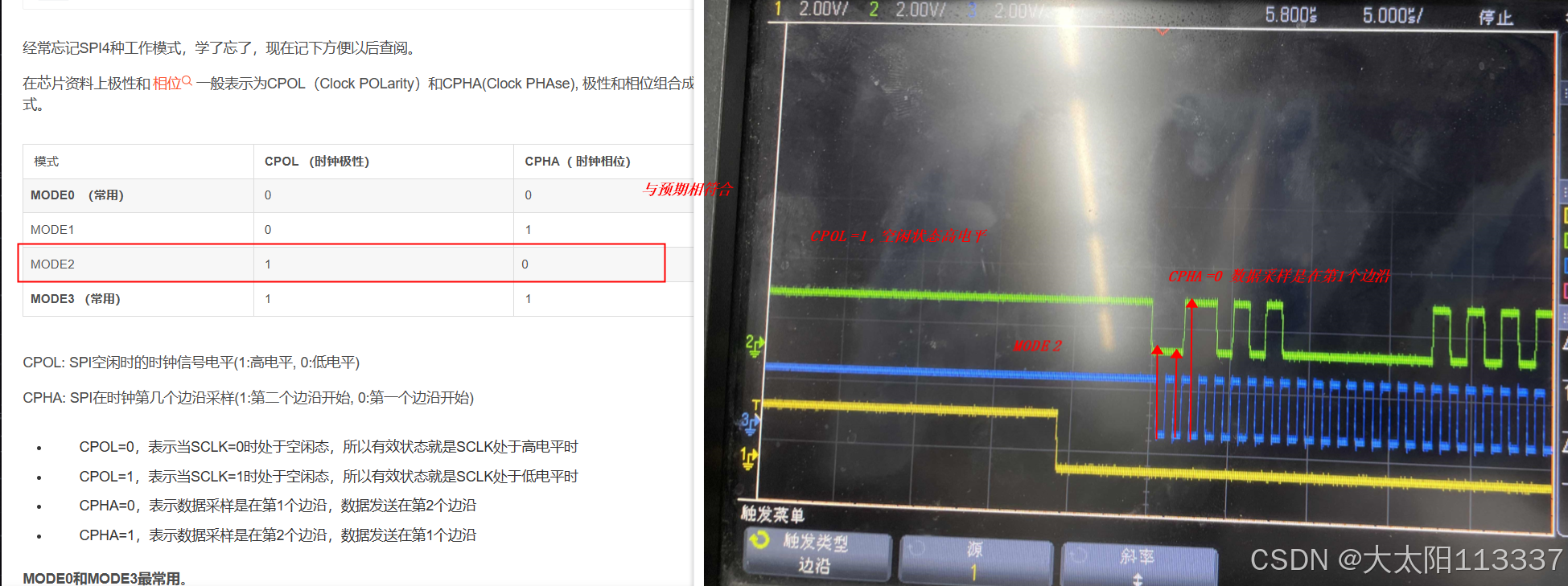

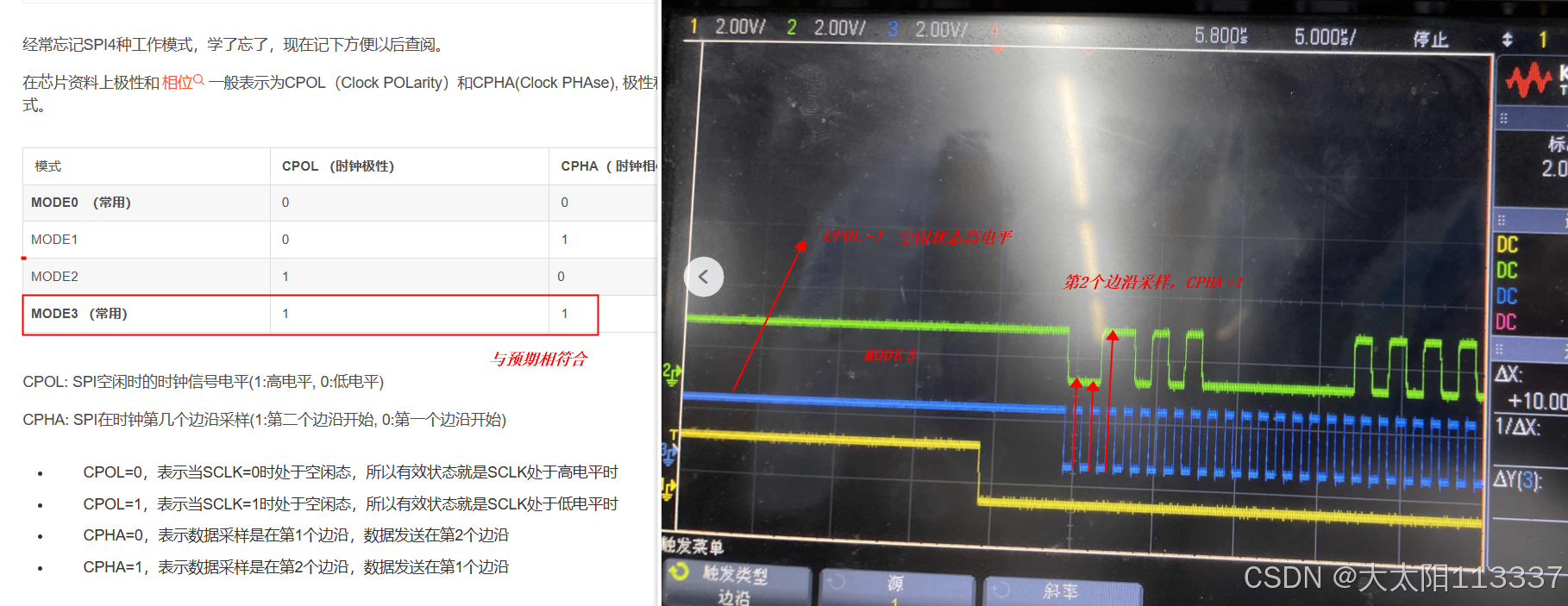

2 结合示波器测量我们ADP板子的SPI波形进行SPI模式分析

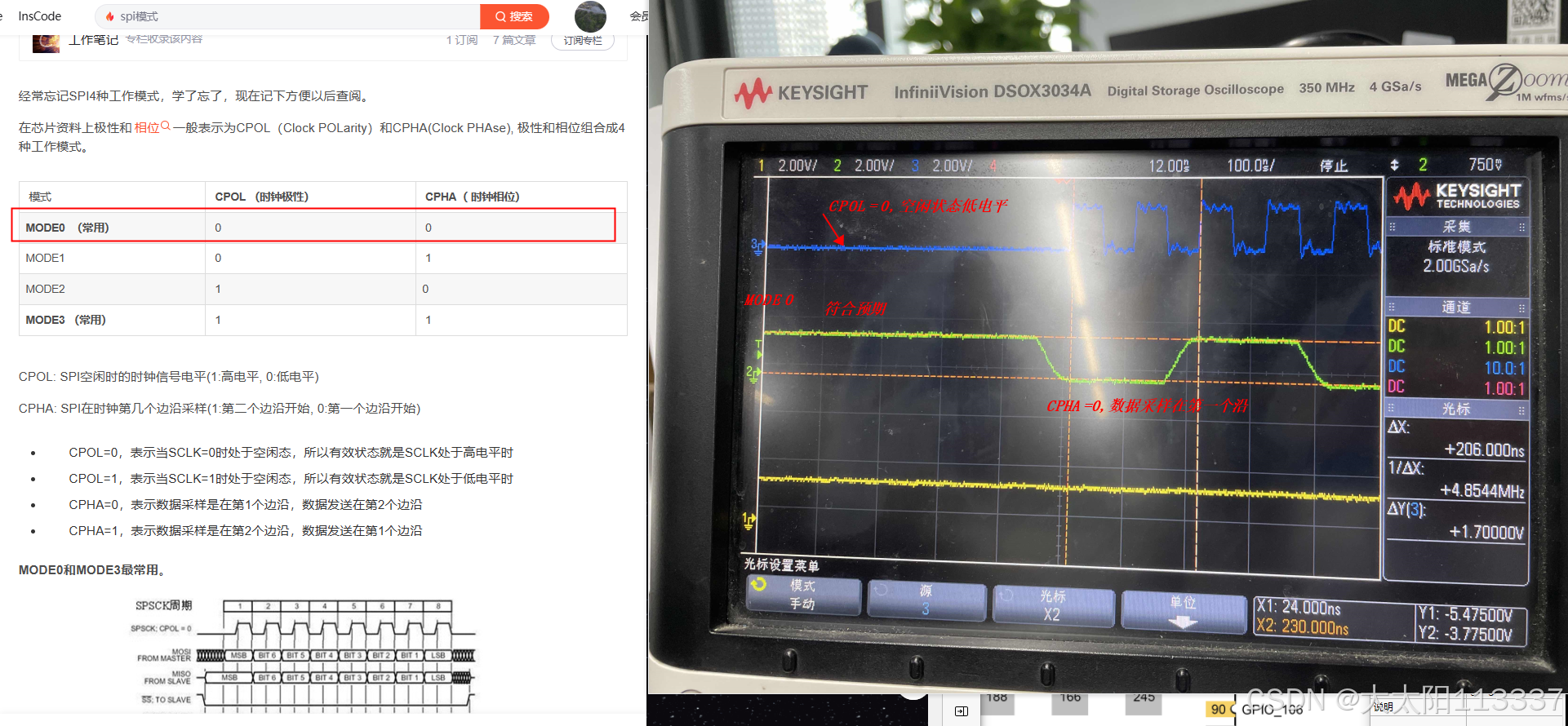

2.1 实测mode0符合预期

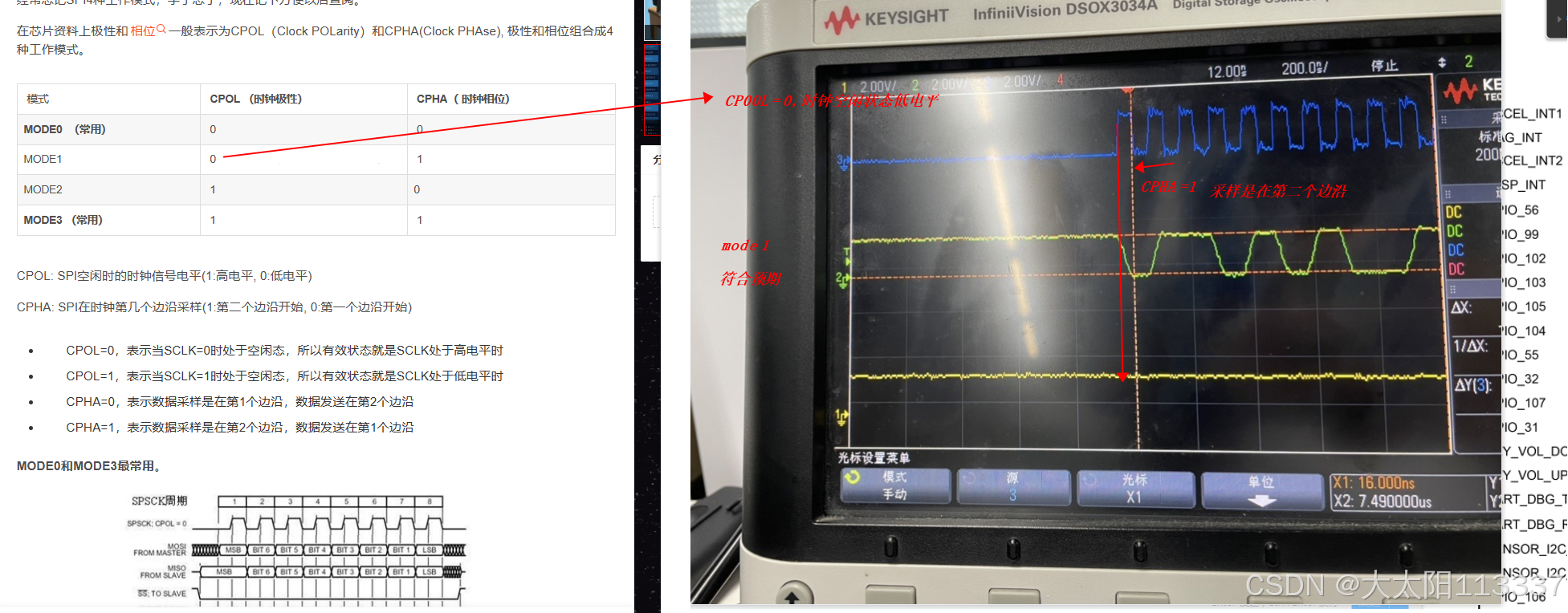

2.2 实测mode1符合预期

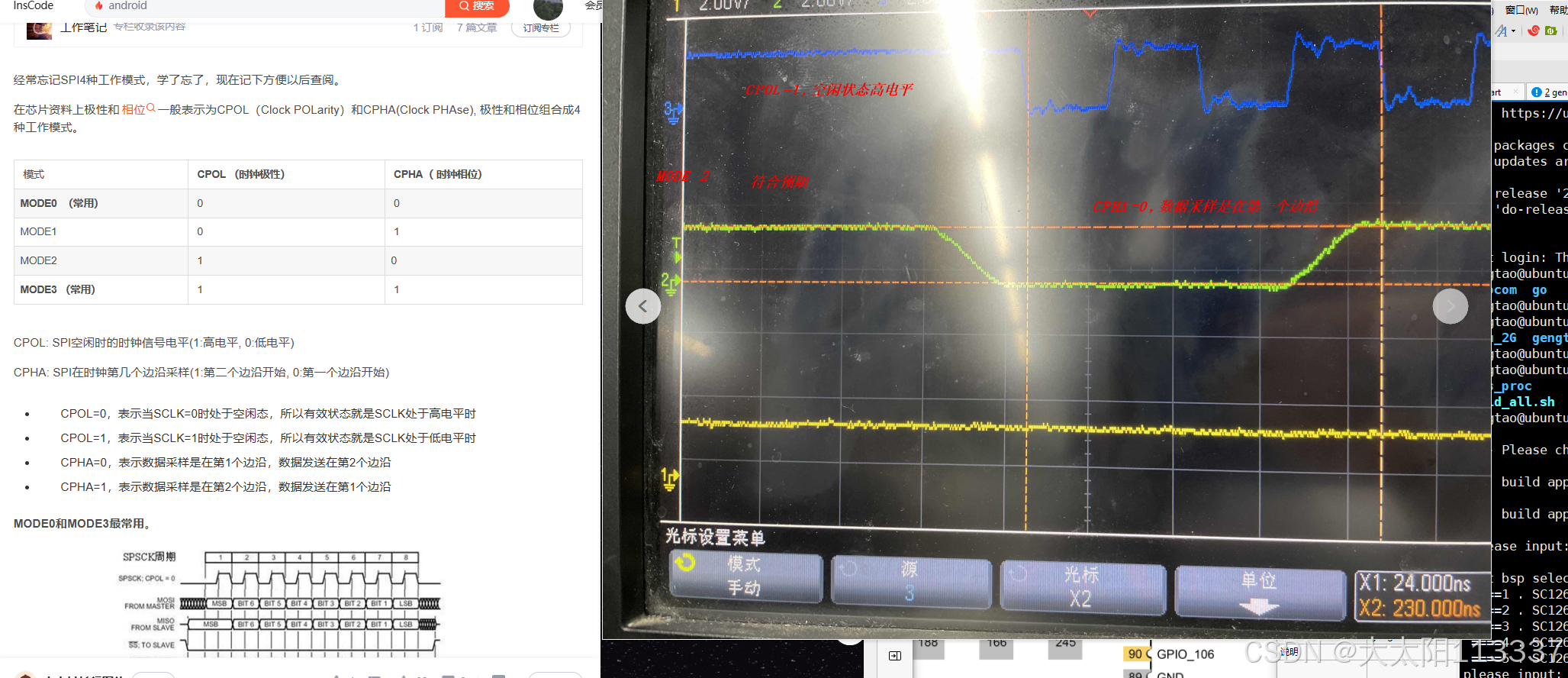

2.3 实测mode2符合预期

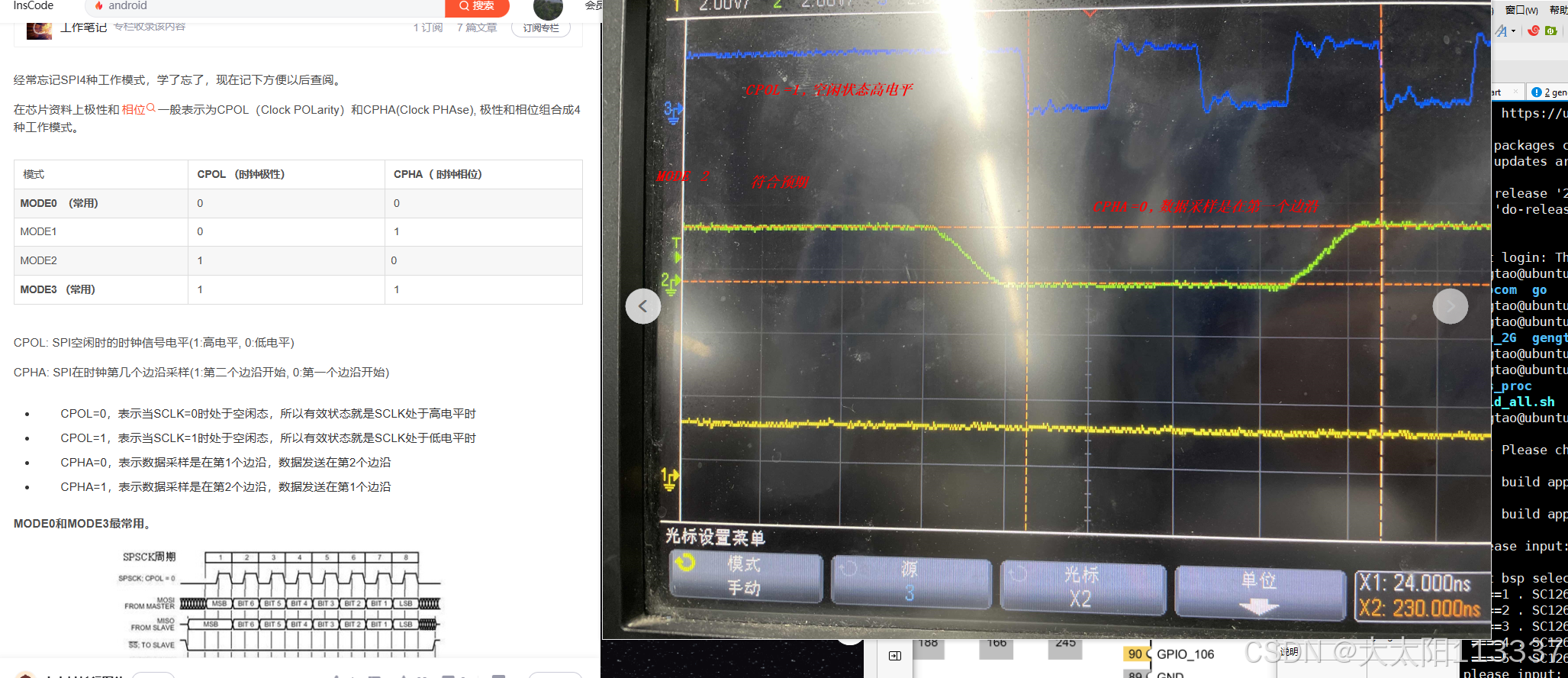

2.4 实测mode3符合预期

3:结合示波器测量客户板子的SPI波形进行SPI模式分析

2.1实测mode 0 符合预期

2.2 实测mode1符合预期

2.3 实测mode2符合预期

2.4 实测mode3符合预期

总结:

3:如何判断CPOL和CPHA

总结:如果起始的SCLK的电平是0,那么CPOL=0,如果是1,那么CPOL=1,然后看数据采样时刻,即时序图数据线上的数据稳定时,对应到上面SCLK时钟的位置,对应着是第一个边沿或是第二个边沿,即CPHA是0或1。(对应的是上升沿还是还是下降沿,要根据对应的CPOL的值,才能确定)。

- 如何判断CPOL:SCLK的空闲时候的电压,是0还是1,决定了CPOL是0还是1;

- 如何判断CPHA:而数据采样时刻对应着的SCLK的电平,是第一个边沿还是第二个边沿,对应着CPHA为0还是1。

2368

2368

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?