本次使用的软件为vivado2021.1

网上有很多写的很好的关于fir ip核的设计指导,但是在我的实际操作中,因为对于数字信号基础知识的掌握不牢固,对软件参数设置理解不深刻,还是会出现很多的错误。现在对于几个操作注意事项进行整理,权当做笔记了。

一、coe文件的产生

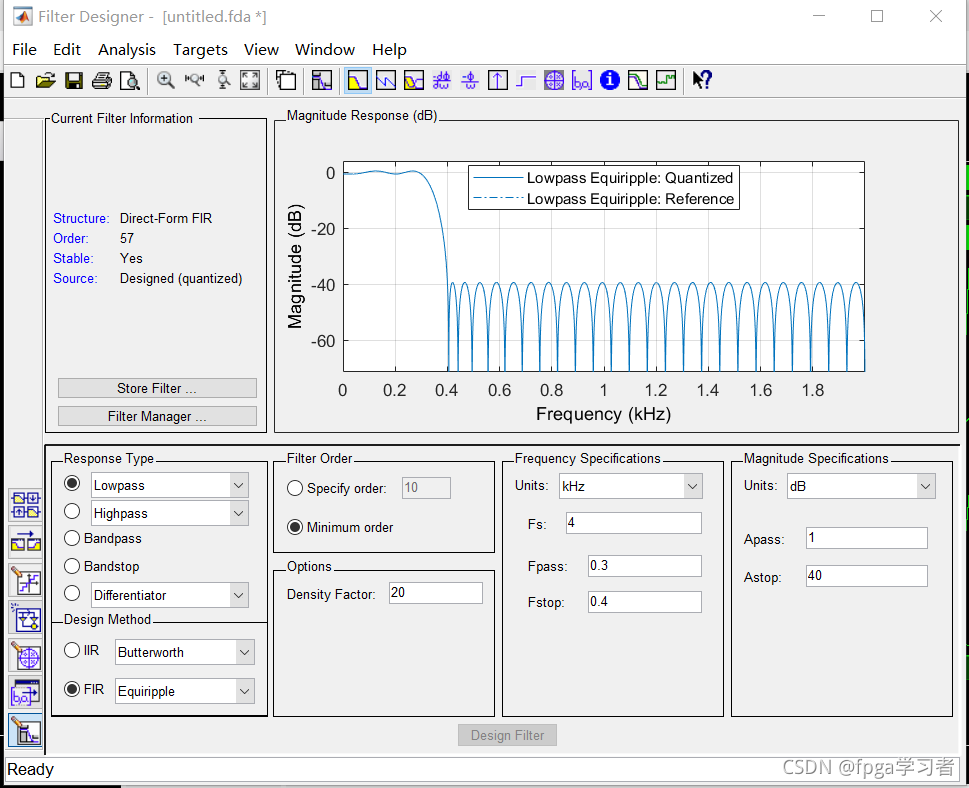

vivado在设计滤波器过程中,没有自动生成抽头系数的功能,最方便快捷的办法就是用matalb的‘“fdatool”工具进行设置,设置页面也比较直观,低通,高通,带通等等都可以设计。以低通滤波器为例,关键参数就是“fpass”和“fstop”,还有采样频率“fs”。前两者根据需求设置,fs需要注意满足采样定理,需要大于被采样信号频率的两倍,也不可以太高,否则滤波器阶数过大,后期运行起来占用资源较多。

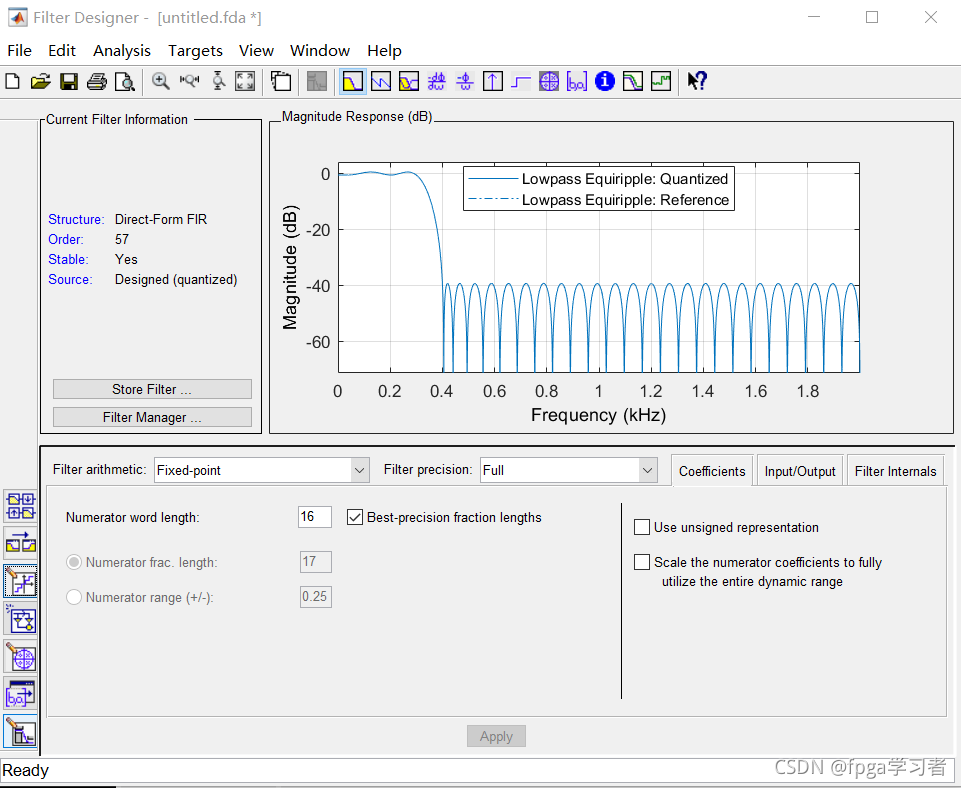

如果要生成coe文件,还需要进行量化,vivado的fir ip核不允许出现小数,点击左侧工具栏,上面第三个图标即可生成,根据需要选择有符号还是无符号的,这在后面滤波器ip核设计中都是要对应起来的。

这里的量化位宽选择了16位,这个数字对于后面的设计也是有用的,需要特别注意。

小结:

coe文件生成个人感觉没有什么太大的坑,就是别忘了量化(要是忘了,matlab也不让你生成的)csdn上有很多文章都讲的很详细,一步步跟着来就行。

二、ip核设计

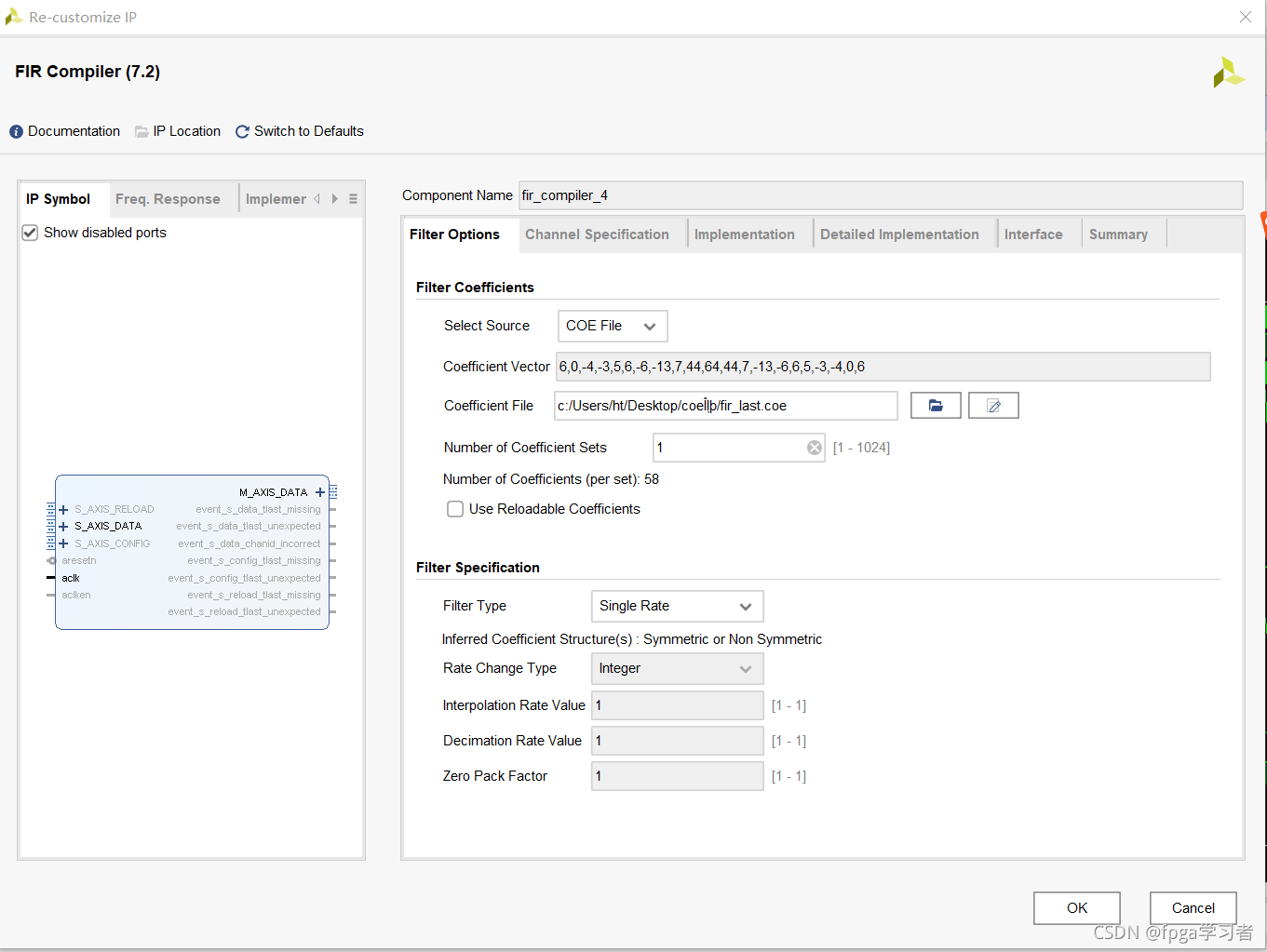

首先就是导入 coe文件,下面还可以选择滤波器类型,默认即可,此页面只需要注意导入文件就行。

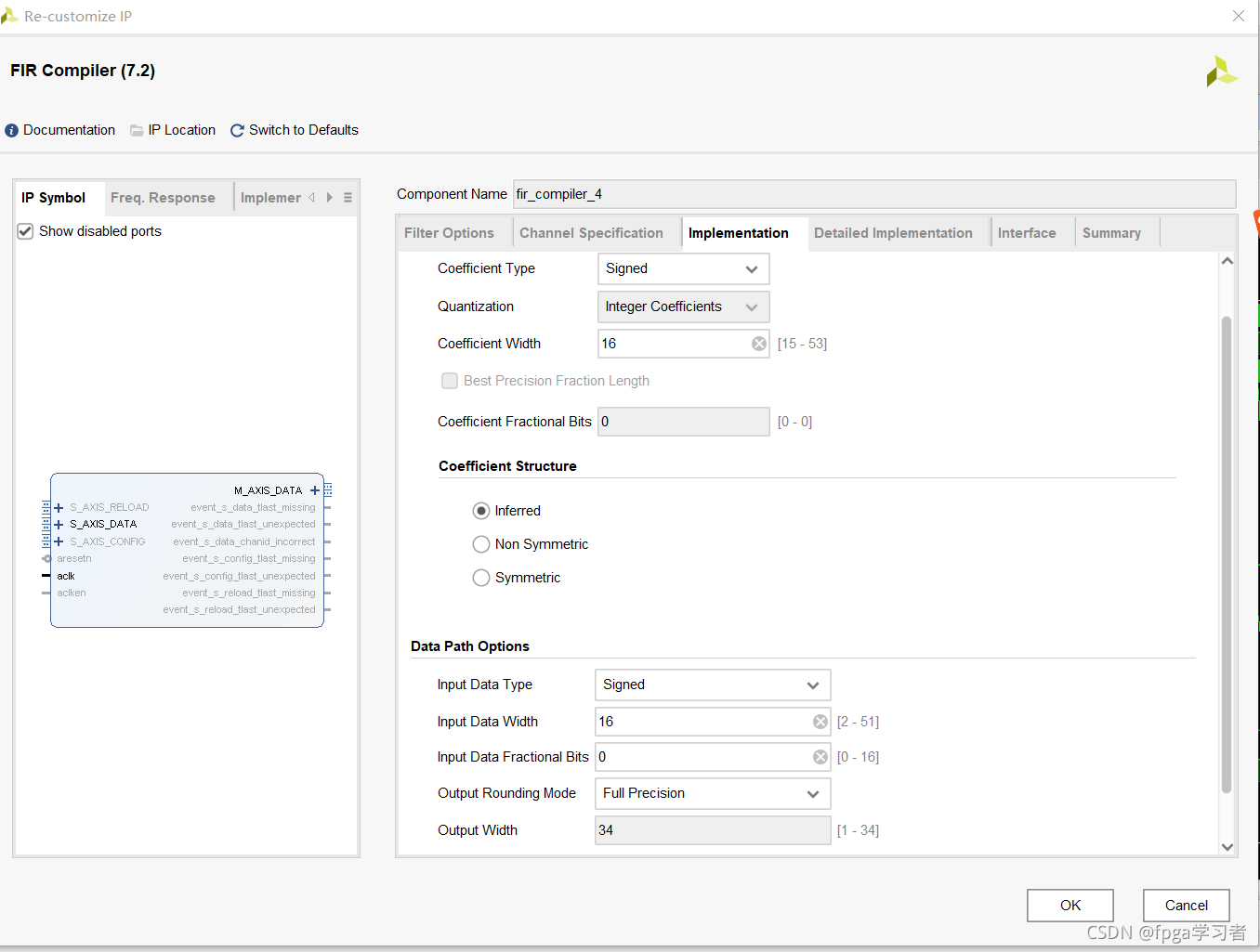

这个页面需要确认你的量化位宽为16(之前在matlab中已经设置过了),量化类型(有符号数还是无符号数要和滤波器设计相对应),输入数据位宽(根据输入信号判断),输入信号类型(根据输入信号自己设置)

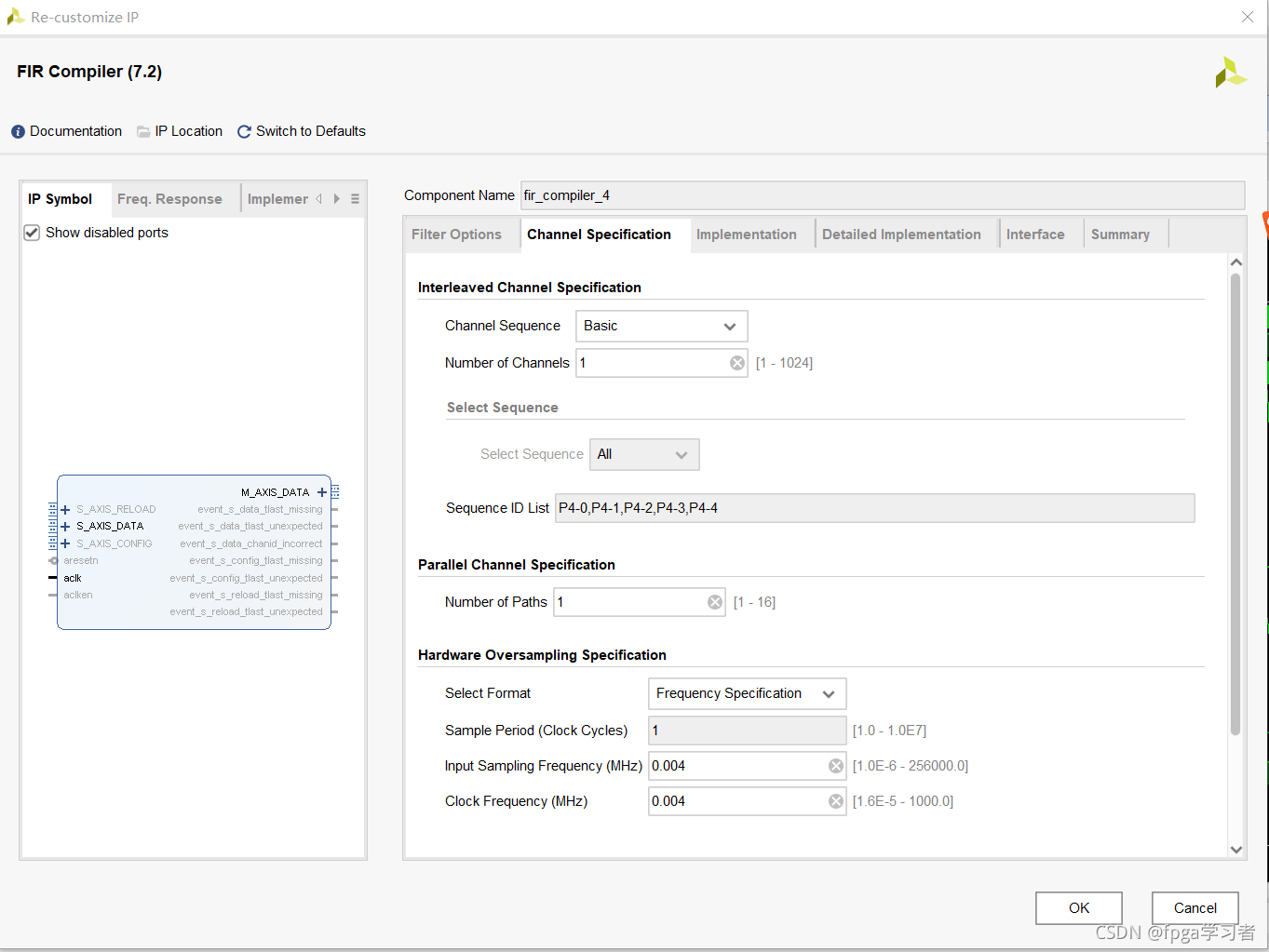

!!!!到关键了

我就是在这跳沟里了

这个界面,底下设置输入采样频率,input samping frequency 要和matlab中设计的采样频率对应,最后有个fir滤波器时钟设置,在其他博主文章中,指定为和采样频率一样。我一开始理解为就是板子上的时钟频率,根据自己需要随便设,我自己用的板子有个200mhz的时钟,我就填上200mhz了。结果出现了两个问题:

1、仿真速度极慢,1ms的波形跑十分钟

2、最后没有滤除4k赫兹,输入什么信号,还是给我出来什么信号。

这个时钟是有讲究的,首先必须和采样频率时钟保持一致,其次在例化ip核的时候,需要通过分频,让fir的输入时钟为设定的这个值,不可以用原来的频率。

也就是必须保持采样频率/时钟频率=1。

之所以仿真慢,是因为用200mhz跑,一个波形就得上百万个点。

之所以没滤除4k,是因为虽然你设计通带是300hz,但是这是在采样频率为4khz条件下,时钟扩大为原来的几倍,通带也就扩大为原来的几倍,把整个滤波器拉宽了,所以4k赫兹大摇大摆的通过了你的滤波器。归一化频率,可以去了解下这个概念。

就是这个地方,因为我自身的数字信号基础知识不扎实,掉进了沟。

三、例化

这个csdn上很多博主写的都很好,包括ip核下面的template文件,每个变量后面都作了解释,我也不再赘述,就是一定注意位数,位数,位数!不要让数据溢出,多点其实没事,除了有点浪费资源。。

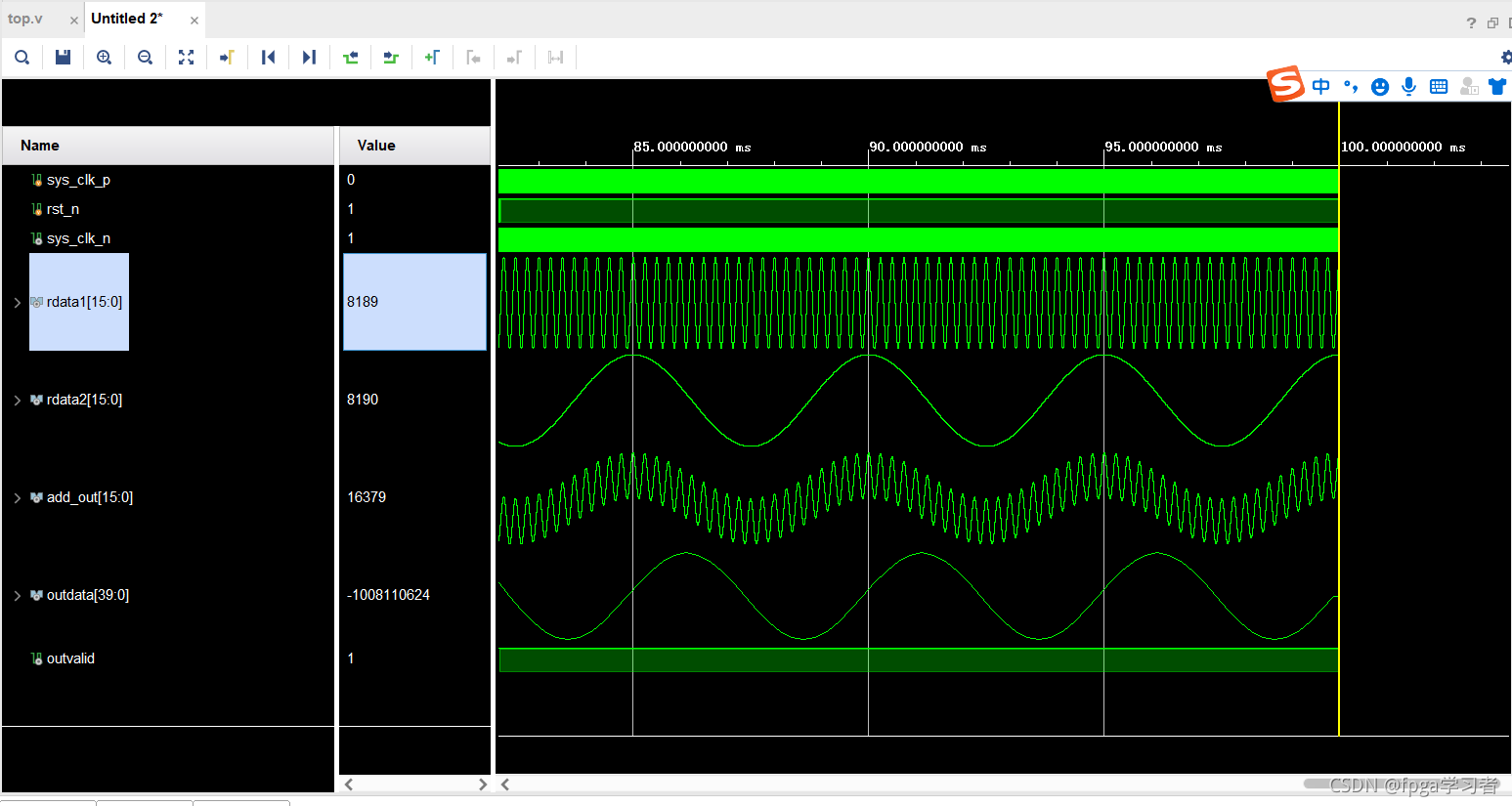

四、仿真

选择波形analog,选择有符号数signed或者无符号数unsigned,在对应栏目右键直接操作就好。包括激励文件的编写,其他博主说的真的很明白了。

每个人都有自己的问题,都有自己的薄弱点,需要通过实操去找自己的问题,一个小小时钟牵绊了我一天,还好最后解决了。ip核理解好很难,但是用起来真爽!

7909

7909

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?