快速链接:

.

👉👉👉 个人博客笔记导读目录(全部) 👈👈👈

思考:在页表的Descriptors中的Lower attributes中有一组shareable属性位, 在页表的TCR_EL1寄存器中有一组shareable属性位,在mair_el1寄存器属性编码中,也有Inner和Outer相关的设置,这三者有啥区别呢?

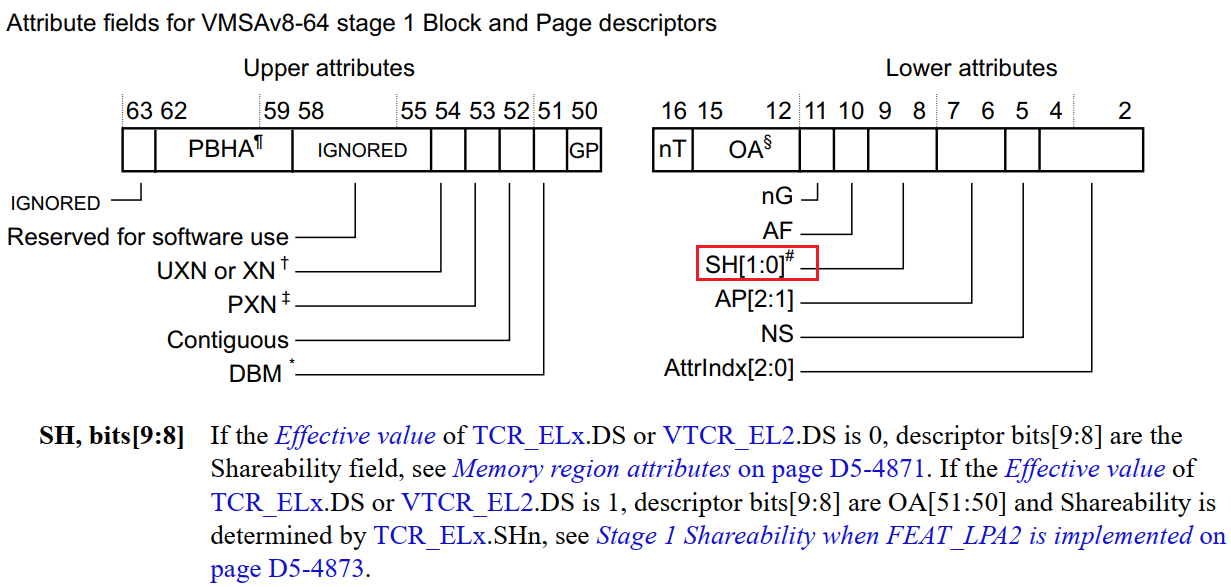

在页表的Descriptors中的Lower attributes中有一个SH属性位

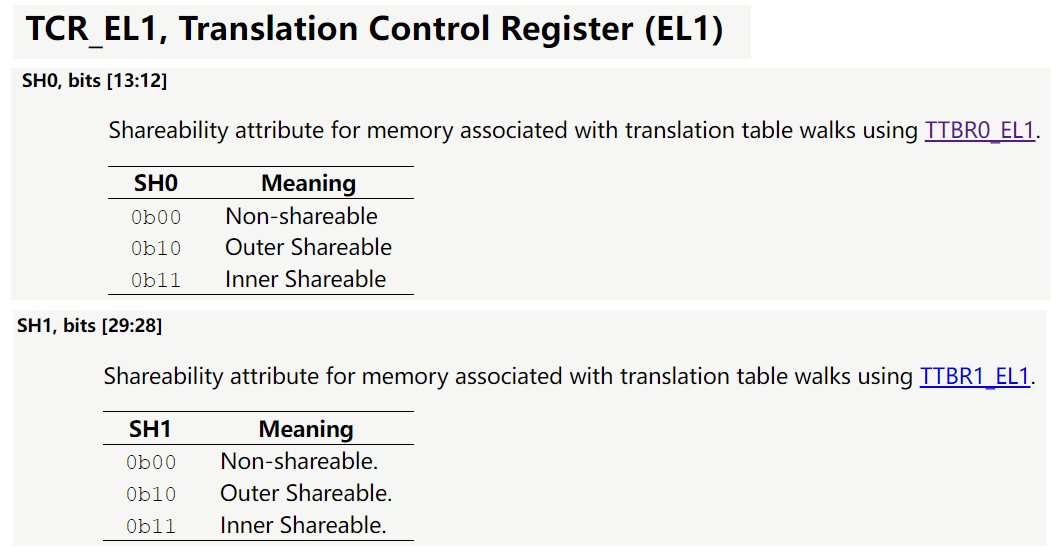

在页表的TCR_EL1寄存器中有一个SH属性位

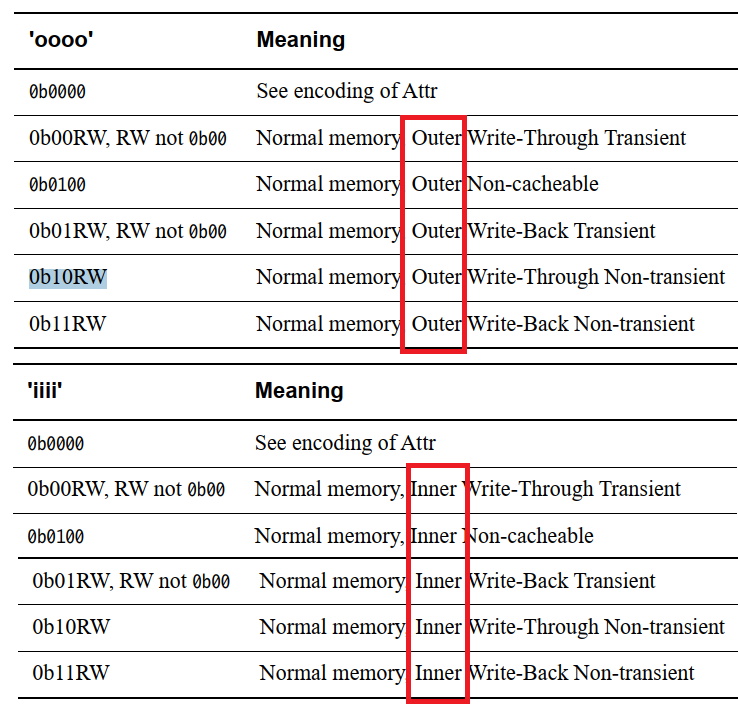

在mair_el1寄存器属性编码中,也有Inner和Outer相关的设置

以上三个域段有啥区别呢? 总结如下:

Mair_elx属性位的编码表示,Inner表示配置inner范围内cache的缓存策略,Outer表示配置outer范围内的缓存策略。

如果TCR_EL1.DS = 0, 那么shareable属性使用页表中的SH属性值,如果TCR_EL1.DS = 1,则shareable属性使用TCR_EL1寄存器中的SH属性值。

使用页表项中的属性值,颗粒度更小一些,使用TCR_EL1中的属性值,简直没啥颗粒度。大多数操作系统中还是使用的前者,即使TCR_EL1.DS = 0

最后

如果您已经订阅此付费专栏,请务必加我微信(coding_the_world),备注"姓名+职业方向+ARM专栏",我拉您如ARMv8/ARMv9讨论群。

也可以从下述链接找到群号扫码进入:

https://www.processon.com/view/link/641321133524617475ff9b8a

637

637

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?