最近在学习DSP28335 的ADC采样模块,针对其里面的各种名词概念,现整理一下。

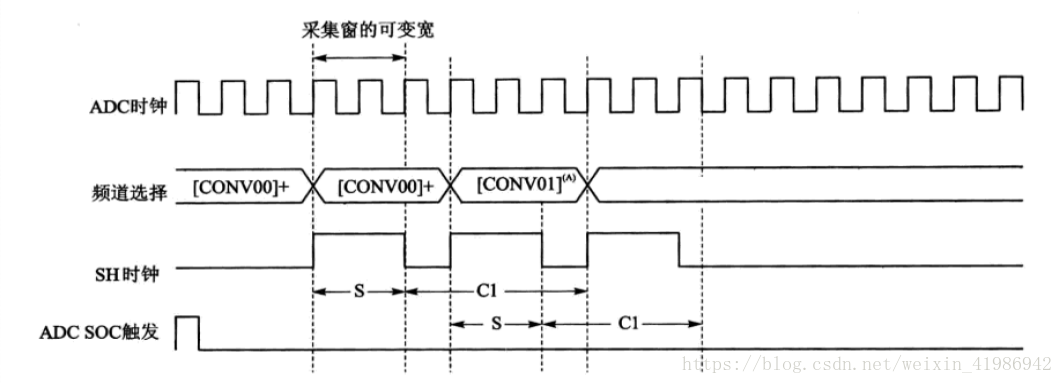

- 采样频率,也被称为采样速率。大家想想ADC的采样是需要由软件or外部引脚or ePWMx SOCA or ePWMxSOCB 触发的。只有当触发信号产生时,SEQ排序器才开始工作。那么两个触发信号之间的间隔就是采样时间,也即采样频率的倒数。

- 时钟频率,也即为ADCCLK。这是ADC模块工作的时钟。由HSPCLK经过ADCCLKPS 内核时钟分频器和CPS 内核时钟预分频位得到ADCCLK。注意:ADCCLK的最高频率不能超过25MHZ

- 采样窗口,这个是当你对某个管脚采样时,采样电容的电压才能累积到采样电压。所以这里需要给一个足够大的时间窗口。一般不能小于7个ADCCLK

- 转换时间,一个序列转换完成的时间。这与转换原理:1.积分型A/D的转换 2.逐次比较型A/D转换 3.全并行/串并行A/D 有关。转换的时间不能大于采样时间,才能正确采样。

本文深入解析DSP28335的ADC采样模块,涵盖采样频率、时钟频率、采样窗口及转换时间等关键概念。阐述了触发信号、内核时钟分频对ADCCLK的影响,以及确保正确采样的条件。

本文深入解析DSP28335的ADC采样模块,涵盖采样频率、时钟频率、采样窗口及转换时间等关键概念。阐述了触发信号、内核时钟分频对ADCCLK的影响,以及确保正确采样的条件。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?