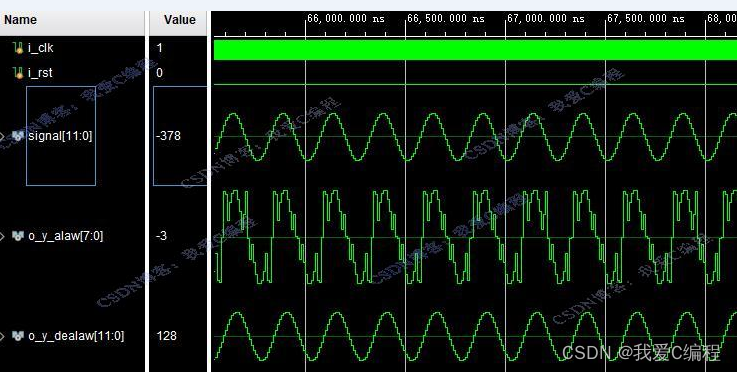

1.算法仿真效果

VIVADO2019.2仿真结果如下(完整代码运行后无水印):

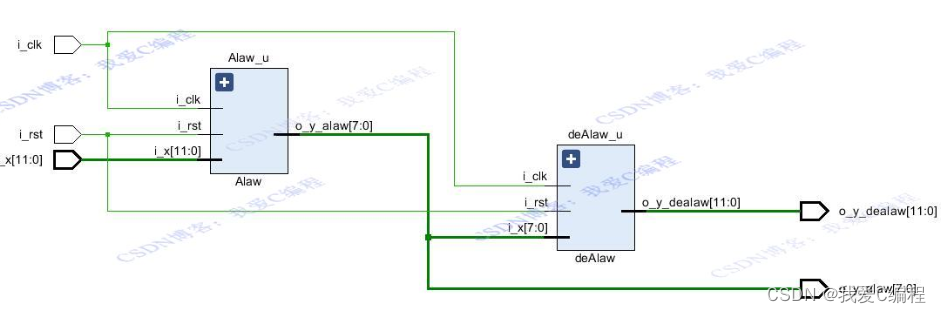

RTL图如下所示:

2.算法涉及理论知识概要

A律压缩是一种广泛应用于语音编码的非均匀量化技术,尤其在G.711标准中被欧洲和中国等国家采纳。该技术的核心目的是在有限的带宽下高效传输语音信号,同时保持较高的语音质量。在基于现场可编程门阵列(Field-Programmable Gate Array, FPGA)的实现中,A律压缩解压缩算法的高效硬件实现成为可能,这对于实时通信系统尤为重要。

FPGA实现要点

信号预处理:首先,模拟信号需经过采样和量化变为数字信号,这一过程通常在FPGA的模数转换器(ADC)部分完成。

非线性变换:接下来,通过查找表(LUT)或多项式近似实现上述非线性变换。FPGA的LUT资源丰富,适合存储折线近似所需的查找表值。例如,对于13折线近似,可以预先计算每个区间的输出值,存储在LUT中,输入信号根据其所在区间直接查表得到量化输出。

量化与编码:量化后的信号需要进一步编码为二进制数据进行传输。编码过程往往涉及将连续的量化值映射到固定的比特序列,这可以通过简单的逻辑门电路或者状态机在FPGA上实现。

同步与控制:FPGA实现中,还需要考虑时钟管理和状态控制逻辑,确保整个压缩流程按时序正确执行,同时处理好数据的流动和存储问题。

3.Verilog核心程序

1191

1191

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?