目录

1. PLL仿真时,clk_locked_flag无法正常输出。

3. FIFO仿真时IP核无法正常输出信号dout以及空、满标志信号

1. PLL仿真时,clk_locked_flag无法正常输出。

属于TD仿真库的BUG,需要在代码中生成专门用于PLL例化所需的复位信号,与其他模块的复位信号不同。如下:

//produce reset

(*keep*) wire pseudo_reset = 0;

reg [7:0] por_cnt;

reg reset;

always@(posedge sys_clk or posedge pseudo_reset)

if (pseudo_reset) begin

por_cnt <= 0;

reset <= 1;

end

else if (por_cnt != 8'haa) begin

por_cnt <= por_cnt + 1;

reset <= 1;

end

else begin

por_cnt <= por_cnt;

reset <= 0;

end 只有在仿真时会出现如上问题,在实际使用中用正常的复位信号即可。

2. DRAM IP生成后会出现如下问题

1)地址和信号线可能会有不同位数的高阻态,查看RTL试图,可以看出是软件编译自动优化的结果,需要在代码中将相应信号取消优化。添加//synthesis keep。

2)IP核operating mode选择No change模式,读和写分开,按照仿真的代码执行,如果选择write fiest会在写入后立即读出到输出端口。

3)状态转换或者写入过程需规划好每一个时钟对应的写和读,否则可能会出现读取的数据乱。

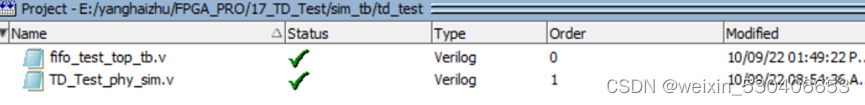

3. FIFO仿真时IP核无法正常输出信号dout以及空、满标志信号

modelsim使用的仿真文件,rtl_sim或者phy_sim,但是rtl_sim有时候无法仿真一些IP核。因此修改为phy_sim重试。

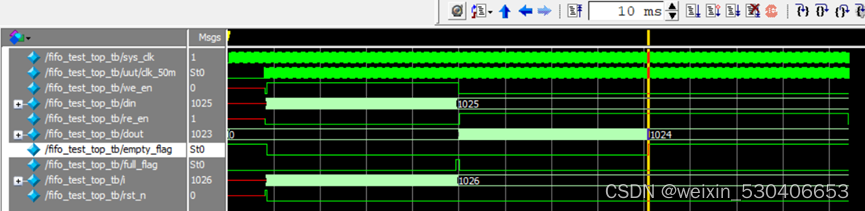

仿真结果如下:

结果表明:

结果表明:

1)empty_flag信号:在写入第一个数据后的下个时钟上升沿从1变成0,在读出最后一个数据的同时从0变成1;

2)full_flag信号:在写入最后一个数据的同时从0变成1,在读出第一个数据的下一个时钟上升沿从1变成0.

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?