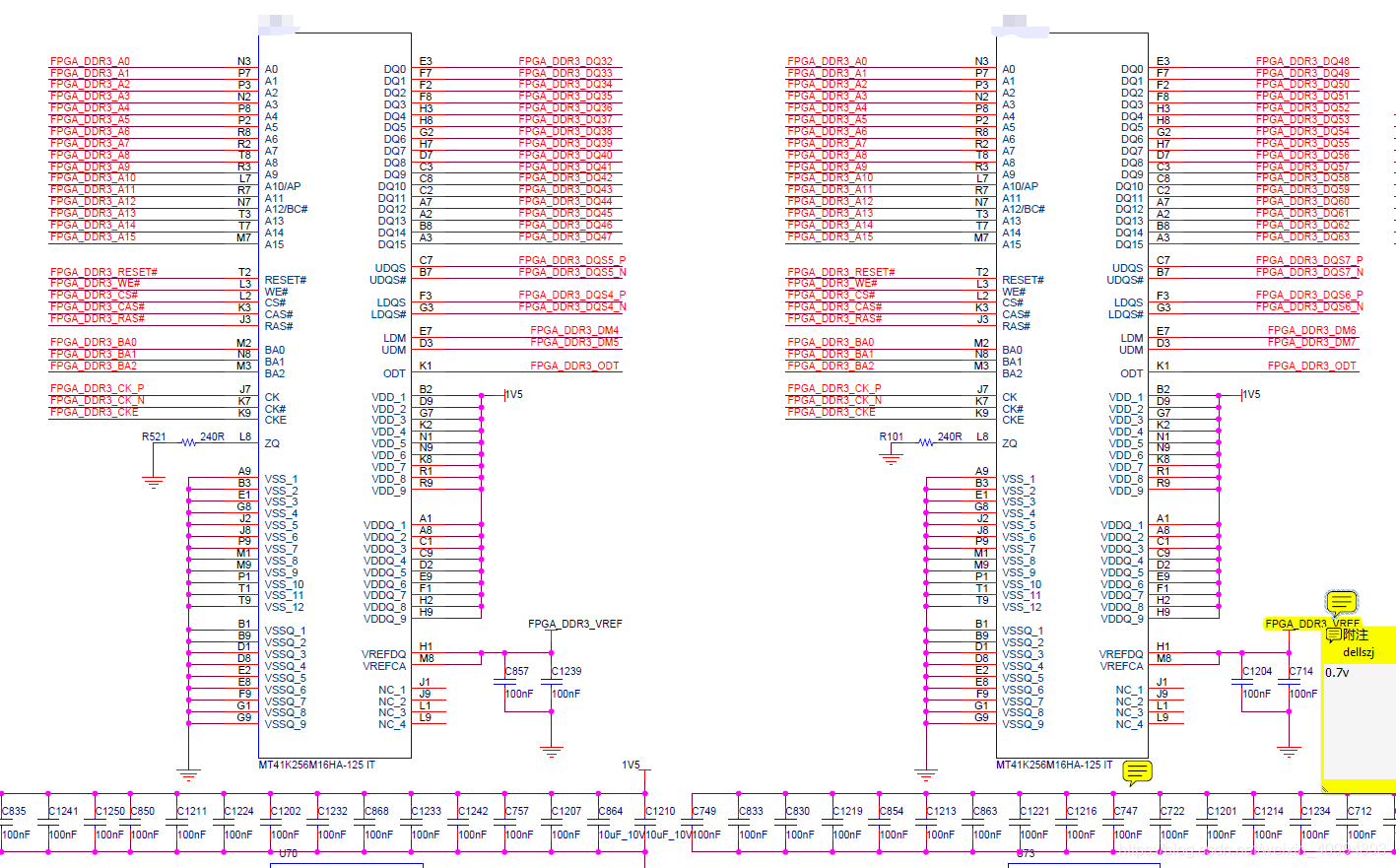

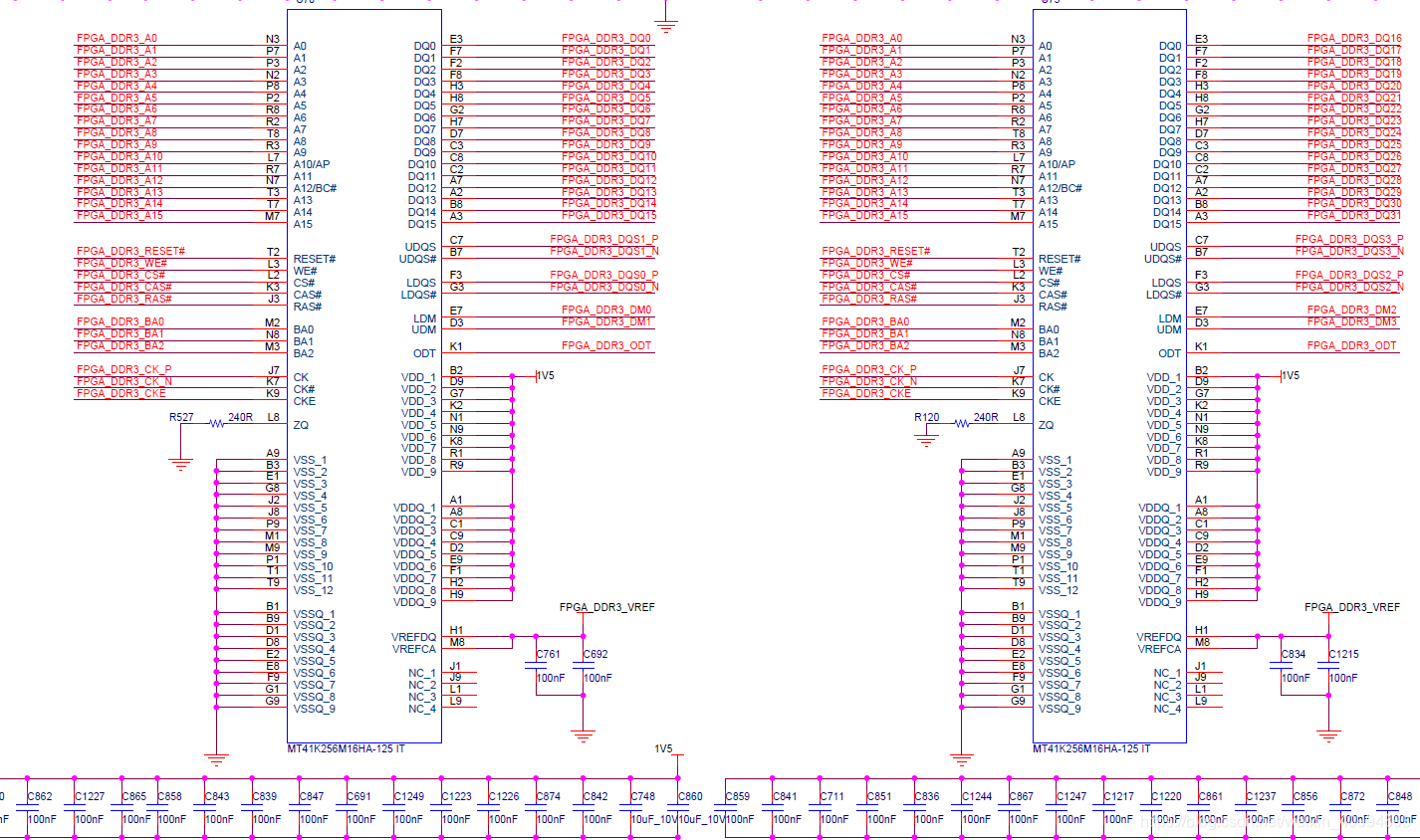

原理图展示

(1) 在XC7Vx690ffg1927使用了4颗MT41K256M16HA-125 IT,每个容量4Gb。4个DDR芯片组成了64位宽与FPGA相连接。

(2)在设计PCB的时候,注意高速信号数据传输的可靠性,注意走线等长及阻抗匹配问题。

MIG设计教程

2.1 MIG控制器的使用与配置

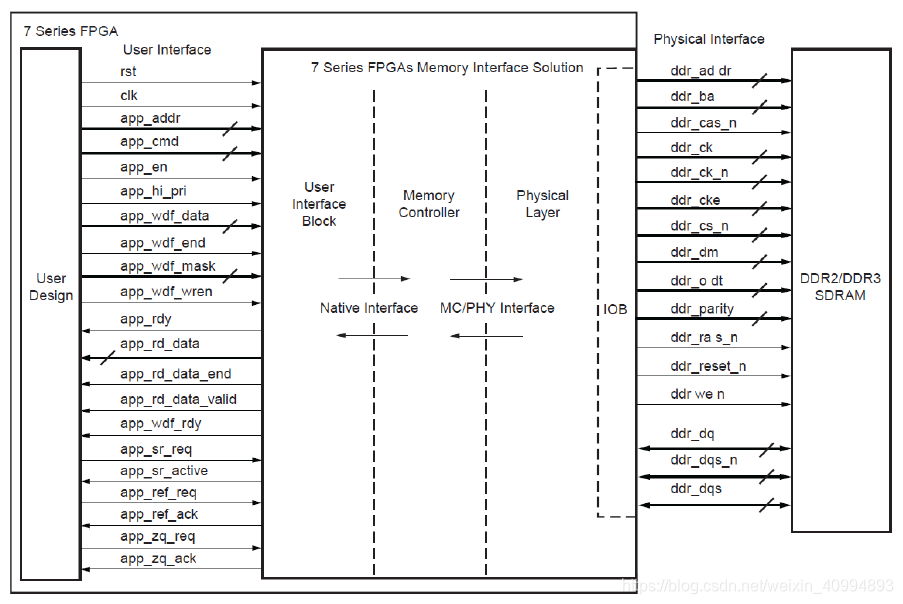

MIG由xilinx提供的一个免费的DDR控制器。关于7系列的解决方案如下图所示

DDR3控制器包含3部分:用户接口模块(User interface Block), 存储器控制模块(Memory Controller)和DDR3的物理接口(Physical Layer)。开发人员只需要开发用户的逻辑设计跟DDR 控制器的用户接口对接来读写DDR3的数据。参考文档UG586 December 5, 2018

DDR3控制器包含3部分:用户接口模块(User interface Block), 存储器控制模块(Memory Controller)和DDR3的物理接口(Physical Layer)。开发人员只需要开发用户的逻辑设计跟DDR 控制器的用户接口对接来读写DDR3的数据。参考文档UG586 December 5, 2018

本文介绍了在XC7Vx690tffg1927 FPGA中使用MIG设计DDR3内存控制器的详细过程,包括原理图展示、MIG控制器配置、DDR3时钟设计和测试仿真。通过行为级仿真验证了DDR3读写功能的成功实现。

本文介绍了在XC7Vx690tffg1927 FPGA中使用MIG设计DDR3内存控制器的详细过程,包括原理图展示、MIG控制器配置、DDR3时钟设计和测试仿真。通过行为级仿真验证了DDR3读写功能的成功实现。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?