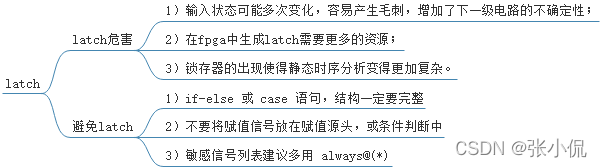

在做项目的项目的时候遇到了一个很有意思的问题,功能仿真没有问题,可是在FPGA上面上板调试就是不对,最后通过检查综合后的电路发现有一处生成了latch,在实际电路中latch容易产生毛刺,导致下一级电路可能出现错误状态,如果书写不规范,仿真是发现不了这个问题的,平时书上经常看到一定要避免latch这样的字眼,自己感觉懂了,直到这次真的遇到问题时,调试好久才发现,所以就把不规范的代码都在vivado上面跑了一下综合,给自己长长记性。(由于笔者比较菜,有不对的地方,欢迎大家批评指正)

一个变量声明为寄存器时,它既可以被综合成触发器,也可能被综合成 Latch,甚至是 wire 型变量。

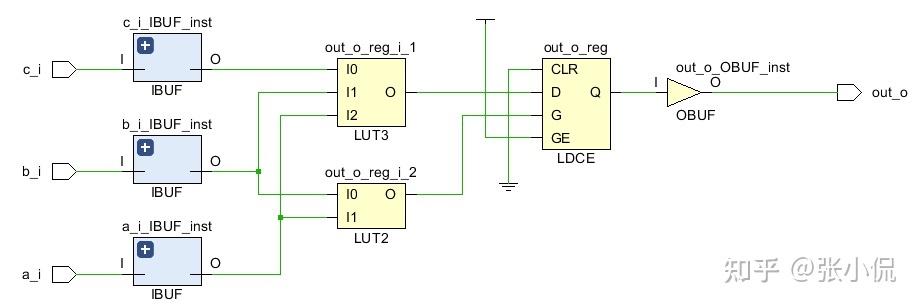

第一种:组合逻辑中,不完整的 if - else 结构会综合成latch,这种是最为常见的,因为平时多用时序逻辑电路, if - else不完整并不会综合成latch,可能由于习惯,组合逻辑中有时候也会忘记。

always@(*)

if(a_i)

out_o = c_i;

else if(b_i)

out_o = 1'b1;

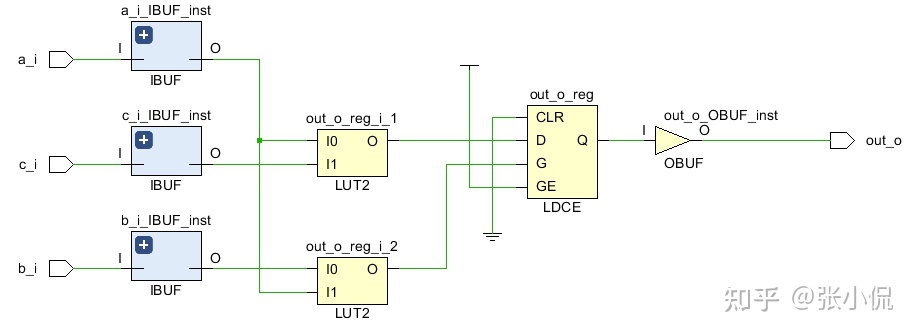

第二种:组合逻辑电路中将值赋值给自己

always@(*)

if(a_i)

out_o = c_i;

else if(b_i)

out_o = 1'b0;

else

out_o = out_o;

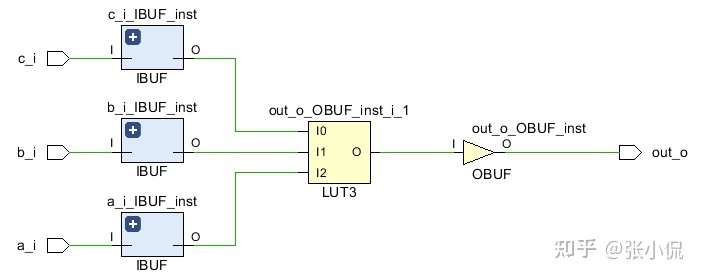

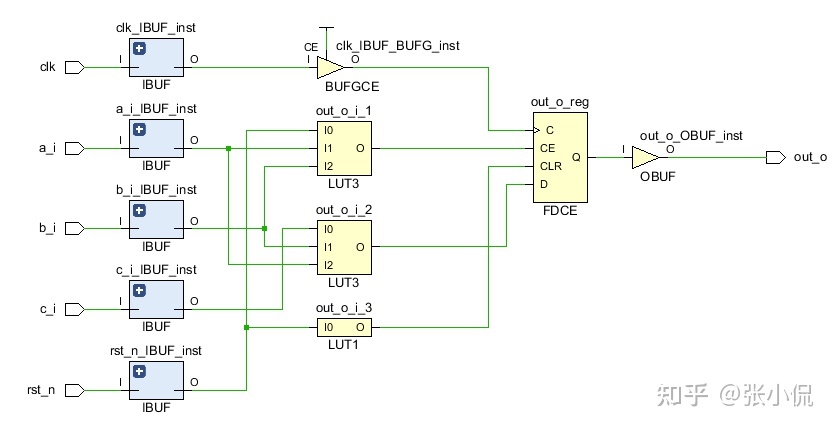

第三种、这种情况是正确的

always@(*)

if(a_i)

out_o = c_i;

else if(b_i)

out_o = 1'b1;

else

out_o = 1'b0;

这个是通过时序逻辑电路完成相同功能

always@(posedge clk or negedge rst_n)

if(~rst_n)

out_o <= 1'b0;

else if(a_i)

out_o = c_i;

else if(b_i)

out_o = 1'b1;

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?