单端输入指信号有一个参考端和一个信号端构成,参考端一般为地端,差分是将单端信号进行差分变换,输出两个信号,一个和原信号同相,一个和原信号反相。差分信号有较强的抗共模干扰能力,适合较长距离传输,单端信号则没有这个功能。信号传输到接收端后,可以再将差分信号转变为单端信号。很多情况下需要将单端信号转为差分信号,这就要求有一种可以将单端信号转换为差分信号的电路,即单端-差分转换器。

单端转差分信号电路详解

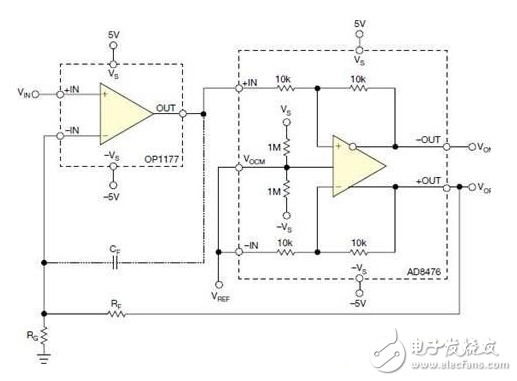

上图中电路是一种双放大器反馈结构,其中运放决定了电路的精度以及噪声性能,而差分放大器则扮演了单端-差分转换功能。这个反馈结构抑制了AD8476的误差,包括噪声、失真、偏移、漂移,它用运放的大开环增益替代了AD8476内部的运放反馈回路。本质上,这个结构是采用运放针对输入端的开环增益,衰减了AD8476的误差。

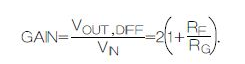

图中的外接电阻RF和RG设定单端-差分放大器的增益,即

将RF短路,RG开路,可以设定为最低增益2。

与任何反馈连接相同,必须非常注意确保系统的稳定。OP1177与AD8476的级联构成了一个组合式差分输出运放,其开环增益是OP1177开环增益与AD8476闭环增益的乘积。因此,AD8476的闭环带宽为OP1177的开环增益加了一极。为确保稳定性,AD8476的带宽应高于OP1177的单位增益频率。当电路的闭环增益大于2时,这个要求可以放松,因为电阻反馈

网络可有效地将OP1177的单位增益频率降低RG/(RG+RF)。AD8476的带宽为5MHz,而OP1177的单位增益频率为1MHz,因此电路在任何增益下都不会有稳定性问题。

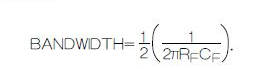

当使用单位增益频率远大于差分放大器带宽的运放时,可以插用一个带宽限制电容CF,如图所示。电容CF与反馈电阻RF构成一个积分器,整个电路的带宽则为:

带宽方程1/2系数的原因是:电路的输出是按单端反馈,而不是差分式。因此,电路的反馈系数与带宽都要减半。

如果这个减少的带宽小于差分放大器的闭环带宽,则电路就会稳定。这种带宽限制技巧也可以将RG开路,从而获得2的增益。

原文地址:http://m.elecfans.com/article/615845.html

本文介绍了一种双放大器反馈结构的单端转差分信号转换电路,通过运放和差分放大器实现高精度信号转换,并详细解析了电路的工作原理及稳定性条件。

本文介绍了一种双放大器反馈结构的单端转差分信号转换电路,通过运放和差分放大器实现高精度信号转换,并详细解析了电路的工作原理及稳定性条件。

327

327

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?