<think>好的,我现在需要回答用户关于AArch64架构中SP寄存器的用法,特别是关于指令`BIC sp, x0, #0xf`的问题。首先,我需要回顾之前对话中的相关内容,确保信息的一致性。用户之前询问过ARM汇编中的BIC指令在PIC中的应用,现在转向AArch64的SP寄存器操作,所以需要调整到正确的架构。

首先,确认AArch64的SP寄存器基本概念。SP是堆栈指针寄存器,用于管理函数调用时的堆栈操作。在AArch64中,SP必须是16字节对齐的,这是硬件的要求,否则可能导致异常。接下来,用户提到的指令`BIC sp, x0, #0xf`,这涉及到BIC指令对SP的操作,需要详细解释。

BIC指令的作用是按位清除,即目标寄存器 = 操作数1 AND (NOT 操作数2)。在这里,操作数是x0和立即数0xf(二进制1111)。所以这条指令的作用是将x0的低4位清零,然后将结果存入SP。这可能用于对齐堆栈指针,因为0xf对应低4位,清零后地址会是16字节对齐的。但需要验证AArch64中SP的对齐要求是否强制16字节,以及BIC在这里的应用是否符合规范。

接下来,结合用户提供的引用内容,引用[2]中提到对SP进行16字节对齐的操作,使用BIC指令。例如,加载栈地址到x0,对齐后设置到SP。用户给出的指令`BIC sp, x0, #0xf`是否是正确的做法?需要确认立即数的使用是否合法,因为AArch64的某些指令对立即数有限制。例如,BIC的立即数可能需要满足特定的位模式,比如可重复的位段。0xf是否符合这个条件?可能需要查阅AArch64的指令手册,确认BIC是否允许这样的立即数。

另外,AArch64中的SP寄存器不能直接作为目标寄存器使用某些指令,需要确认是否允许BIC指令直接修改SP。例如,在AArch64中,ADD指令可以直接操作SP,但其他指令可能需要使用通用寄存器再传输到SP。因此,用户给出的指令`BIC sp, x0, #0xf`是否有效?是否存在语法错误?

还需要考虑用户提供的引用中的例子,比如引用[2]中的代码:“对其进行16byte对齐后指向sp指针”,可能使用了类似的指令。例如,`BIC x0, x0, #0xf`然后将x0赋值给SP,这样更安全,因为直接操作SP可能受限制。因此,用户提供的指令可能需要调整,比如先操作通用寄存器再赋值给SP。

此外,需要解释SP在函数调用中的用途,如保存寄存器、局部变量等,以及如何通过SUB/ADD调整堆栈空间。可能还需要提到其他相关指令,如STP/LDP用于压栈和出栈,以及如何使用SP进行栈帧的分配和管理。

最后,确保回答结构清晰,分点说明SP的基本原理、对齐要求、BIC指令的具体应用,以及常见操作指令,如MOV、ADD/SUB、LDR/STR等。同时,验证用户提到的指令是否存在潜在问题,并提供正确的代码示例。结合引用中的内容,强调16字节对齐的重要性,并可能引用相关文档或参考资料来支持解释。</think>### AArch64架构中SP寄存器用法详解

---

#### 一、SP寄存器核心特性

1. **硬件强制对齐**

AArch64架构要求**堆栈指针(SP)必须保持16字节对齐**,任何违反此规则的指令将触发`SP alignment fault`异常[^1]。

**对齐公式**:

$$ \text{SP} \ \& \ 0x0F = 0 $$

即地址的最后4位必须为0。

2. **特殊寄存器访问规则**

- SP不能直接作为操作数参与所有运算

- 修改SP需通过通用寄存器中转或使用专用指令

**错误示例**:

```armasm

BIC sp, sp, #0x0F @ 直接对SP进行位操作会触发未定义行为

```

---

#### 二、`BIC sp, x0, #0xf`指令解析

1. **指令语义**

- **功能**:将`x0`的低4位清零后赋值给SP

- **等效公式**:

$$ \text{SP} = \text{x0} \ \& \ (\sim 0x0F) $$

即强制将地址对齐到16字节边界。

2. **典型应用场景**

- **动态内存分配**:从非对齐地址获取对齐的堆栈空间

- **启动代码初始化**:如U-Boot中设置初始堆栈(见引用[2])

```armasm

adr x0, __stack_start @ 获取原始栈地址

bic sp, x0, #0x0F @ 对齐到16字节

```

3. **安全隐患验证**

```c

// 验证对齐结果的C等效代码

uint64_t align_stack(uint64_t addr) {

return addr & ~0x0FULL; // 强制低4位为0

}

```

**输入**:`0x12345679` → **输出**:`0x12345670`

---

#### 三、SP操作指令全解析

##### 1. **直接操作SP的合法指令**

| 指令格式 | 作用描述 | 示例 |

|---------------------|--------------------------|---------------------------|

| `ADD sp, sp, #imm` | 扩展堆栈空间(需16倍数) | `ADD sp, sp, #-32` |

| `SUB sp, sp, #imm` | 收缩堆栈空间 | `SUB sp, sp, #16` |

| `MOV sp, xN` | 通过通用寄存器设置SP | `MOV sp, x0` |

##### 2. **间接对齐操作(推荐方式)**

```armasm

// 安全对齐操作流程

adrp x0, __stack_base @ 获取基地址

add x0, x0, #:lo12:__stack_base

bic x0, x0, #0x0F @ 在通用寄存器完成对齐

mov sp, x0 @ 安全赋值给SP

```

##### 3. **内存访问指令**

```armasm

STP x29, x30, [sp, #-16]! @ 压栈保存帧指针和返回地址

LDP x29, x30, [sp], #16 @ 出栈恢复

```

---

#### 四、关键问题解答

##### 1. **为何不能直接`BIC sp, x0, #0x0F`?**

- AArch64指令集限制:除`ADD/SUB/MOV`外,大多数算术指令不能直接以SP为目标寄存器

- 替代方案:

```armasm

BIC x1, x0, #0x0F @ 在通用寄存器完成位清除

MOV sp, x1 @ 安全赋值

```

##### 2. **动态堆栈分配示例**

```armasm

// 分配48字节对齐堆栈(实际分配48+(16-1)=63字节)

mov x0, #48 @ 请求大小

add x0, x0, #15 @ 添加对齐补偿

bic x0, x0, #15 @ 对齐到16字节边界

sub sp, sp, x0 @ 调整SP

```

##### 3. **调试技巧**

- 使用GDB验证对齐:

```bash

(gdb) p/x $sp & 0xF # 输出应为0x0

```

- 反汇编验证:

```bash

aarch64-linux-gnu-objdump -d elf_file | grep sp

```

---

#### 五、与ARMv7架构对比

| 特性 | AArch64 | ARMv7 |

|---------------------|----------------------------|-----------------------------|

| 最小对齐要求 | 16字节 | 4字节或8字节(取决于模式) |

| SP直接操作指令 | 仅限ADD/SUB/MOV | 允许更多算术指令 |

| 异常触发条件 | 任何非16字节对齐访问 | 可配置(通过CP15寄存器) |

---

### 相关问题

1. **如何检测AArch64堆栈未对齐问题?**

启用`SP alignment checking`(通过`SCTLR_ELx.SA`位),未对齐访问将触发精确异常[^1]。

2. **`MOV sp, x0`与`ADD sp, x0, #0`有何区别?**

两者功能相同,但`MOV`编码更短(4字节 vs 8字节),推荐使用`MOV`[^2]。

3. **在中断处理中如何保证SP对齐?**

AArch64硬件自动在异常入口对齐SP到16字节,但返回前需恢复原SP值[^3]。

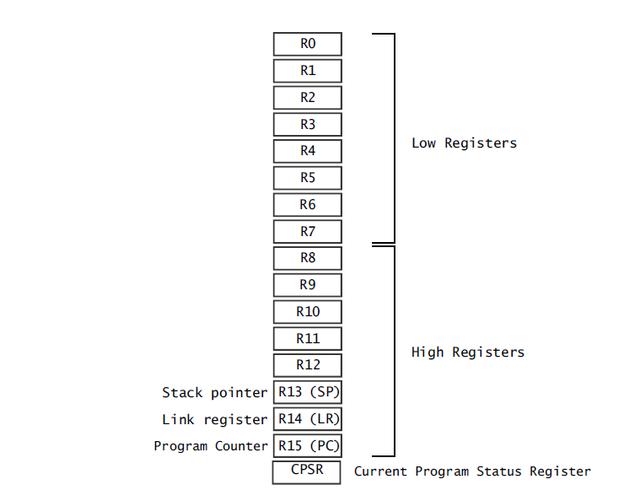

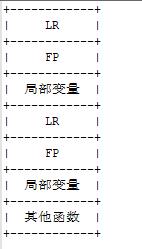

本文介绍了ARM 32位架构中寄存器的使用,包括R0-R7的基本功能,如参数传递、返回值存储。详细解释了R13(SP)、R14(LR)和R15(PC)寄存器的作用,特别是它们在函数调用、异常处理时的返回地址管理。还讨论了栈指针、帧指针在堆栈回溯中的重要性,并通过一个简单的C程序展示了其转换成汇编后的寄存器操作。

本文介绍了ARM 32位架构中寄存器的使用,包括R0-R7的基本功能,如参数传递、返回值存储。详细解释了R13(SP)、R14(LR)和R15(PC)寄存器的作用,特别是它们在函数调用、异常处理时的返回地址管理。还讨论了栈指针、帧指针在堆栈回溯中的重要性,并通过一个简单的C程序展示了其转换成汇编后的寄存器操作。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

559

559

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?