1, Assign 语法

Assign is only for wire type varity;

1.1 define

module main(

input clkIn, //50M, 20ns

input spi_clk,

input spi_mosi,

input spi_cs,

input reset_FPGA,

output wire out_LD_PULS_trig_Out // LD trig out

)

1.2

assign out_LD_PULS_trig_Out = 1;

2. 逻辑语法 or assign

//组合逻辑格式如下:

always@(*) begin

//代码语句

end

//或者可以直接使用assign

3. 时序逻辑格式

always@(posedge clk or negedgerst_n) begin

if (rst_n==1’b0)begin

//代码语句

end

else begin

//代码语句

end

end

/*

时序逻辑中,敏感列表一定是clk的上升沿和复位的下降沿、最开始

必须判断复位。

*/

-

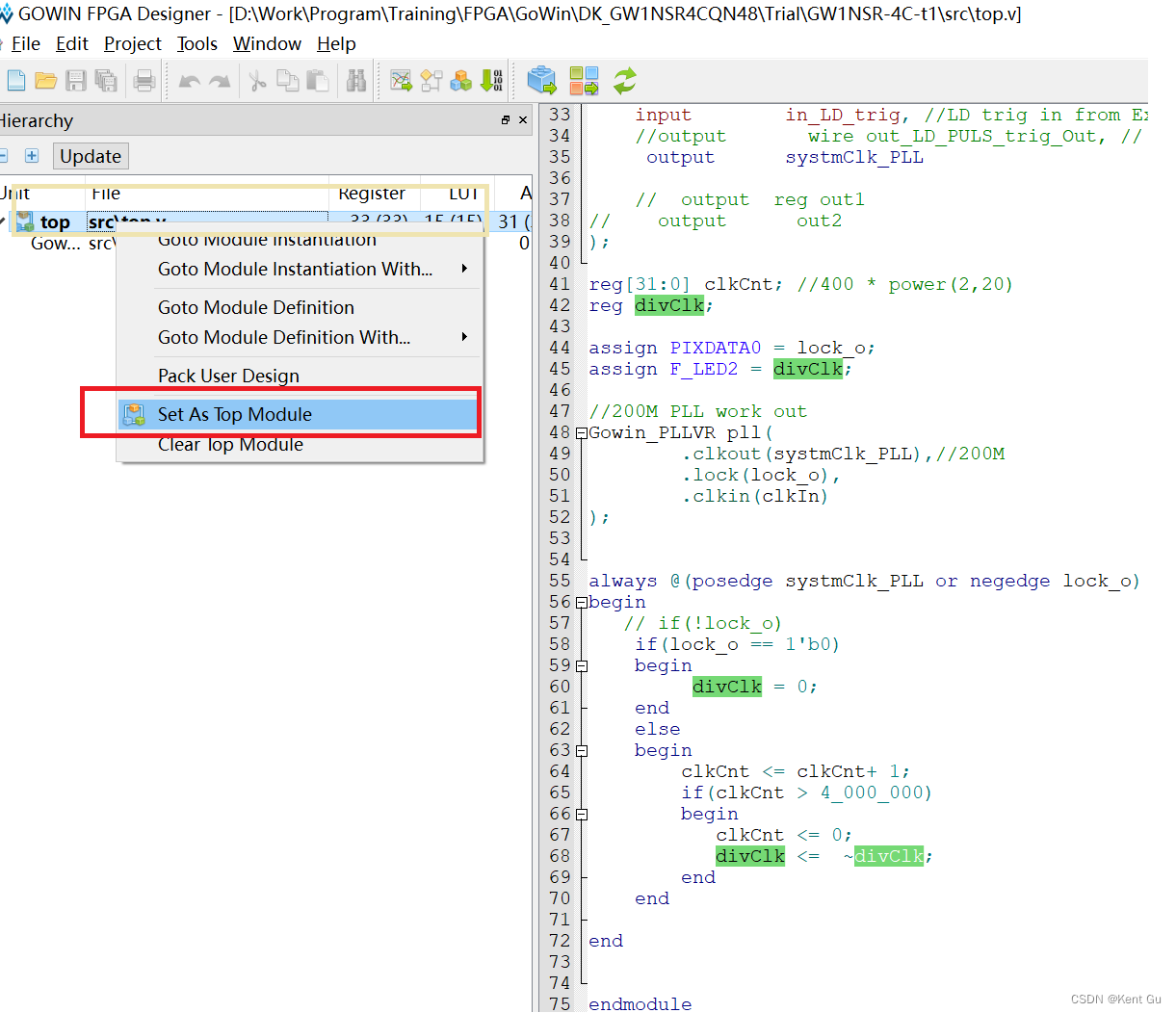

模块简介

模块(module)是Verilog的基本描述单位,是用于描述某个设计的功能或结构,是与其他模块通信的外部端口。

模块在概念上可以等同于一个期间,如通用器件(与门,三态门等)或通用宏单元(计数器,ALU,CPU等)。因此一个模块可以在另一个模块中调用,一个电路设计可有多个模块组合而成。在进行大型数字电路的设计时,可以将其分割成大小不一的小模块,每个小模块实现特定的功能,最后通过顶层模块调用子模块的方式来实现整体功能。(可类比于C语言,main()函数为顶层模块,自己些的函数就相当于一个个的功能模块)

-

模块结构

模块有五个主要部分:端口定义,参数定义(Optional), IO说明,内部信号声明,功能定义。

模块总是以关键词module开始,以关键词endmodule结尾,模块的一般语法结构如下所示:

//端口定义:

module module_name(

clk, // 端口1,时钟

rst_n, // 端口2,复位

dout // 其他信号,如dout

);

//参数定义:(可选,不必须)

parameter DATA_W = 8;

// I/O说明:

input clk; // 输入信号定义

input rst_n; // 输入信号定义

output [DATA_W-1:0] dout; // 输出信号定义

//信号说明:运用reg/wire定义

reg [DATA_W-1:0] dout; //信号类型

reg signal1; //信号类型

//…以下为描述功能部分…

//功能定义:

//1.组合逻辑写法:

always@(*) begin

//代码语句

end

//2.时序逻辑写法:

always@(posedge clk or negedgerst_n) begin

if (rst_n==1’b0)begin

//代码语句

end

else begin

//代码语句

end

end

//结束

endmodule

4141

4141

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?