模块设计

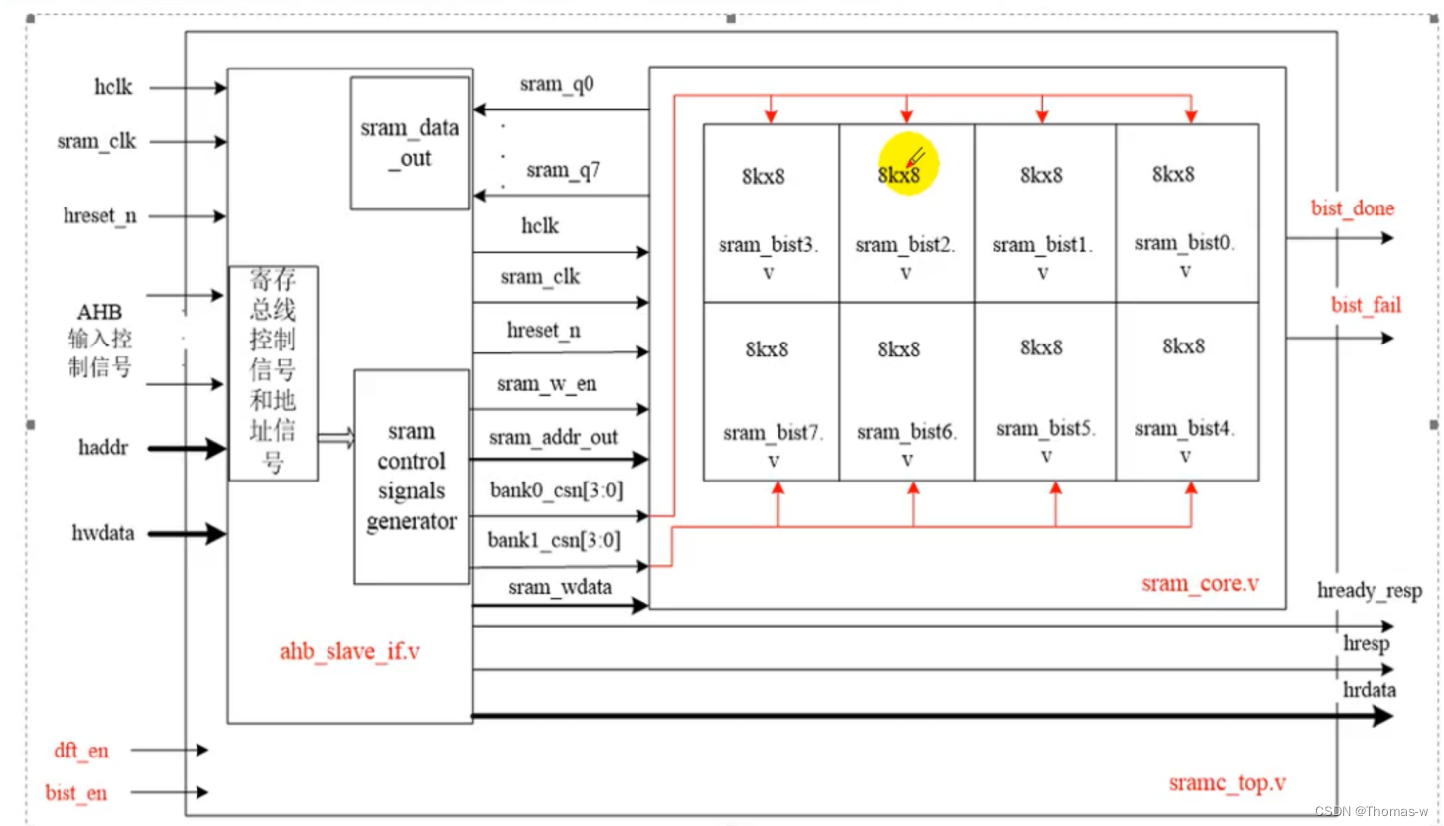

设计架构

功能点

1.支持8bit、16bit、32bit的SRAM数据读写操作

2.支持SRAM的单周期读写

3.支持低功耗工作(8bit/16bit):在多块SRAM组成的存储器中,根据不同的地址,系统选择一块或者多块SRAM,未被选中的SRAM片处于low-power standby模式;

4.支持bist/dft功能

接口信号

设计架构图中已经罗列出来,各个接口的方向、作用在此处就不在细说。可以参考之前AHB、APB部分文章。

AHB_SRAMC验证计划

验证目标

1.RTL VS specification

2.Code coverage:line、interface toggle、(FSM、Expression 、Path)

3.Function coverage

4.完备性、正确性、协议符合性、容错处理

验证语言

Systemveriog

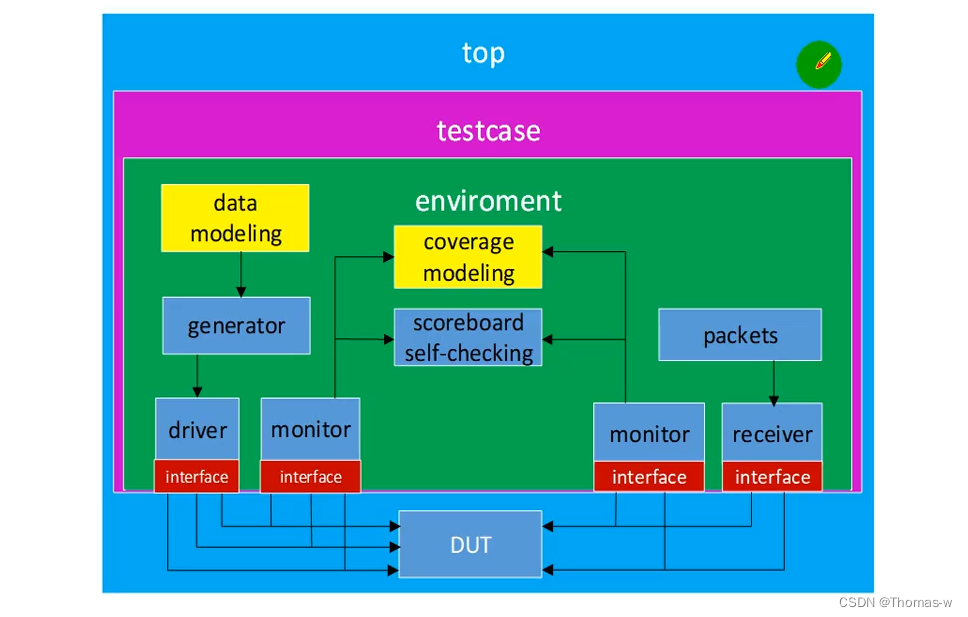

AHB_SRAMC验证平台架构图

验证工具

Questasim、VCS

验证策略

覆盖率驱动的验证策略

白盒验证策略

定向测试

带约束的随机化验证策略

基于断言的验证策略

本文详细介绍了SRAM控制器的模块设计,包括对8bit、16bit、32bit SRAM的数据读写支持,单周期操作,低功耗特性以及内置的BIST/DFT功能。验证计划涵盖了RTL规范、代码覆盖率、功能覆盖及协议一致性等方面,使用Systemverilog作为验证语言,并计划通过Questasim和VCS进行验证。验证策略涉及覆盖率驱动、白盒验证、定向测试和基于断言的方法。

本文详细介绍了SRAM控制器的模块设计,包括对8bit、16bit、32bit SRAM的数据读写支持,单周期操作,低功耗特性以及内置的BIST/DFT功能。验证计划涵盖了RTL规范、代码覆盖率、功能覆盖及协议一致性等方面,使用Systemverilog作为验证语言,并计划通过Questasim和VCS进行验证。验证策略涉及覆盖率驱动、白盒验证、定向测试和基于断言的方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2010

2010

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?