本文目录:

- 一、总线基本概念

- 二、总线定时方式

- 1.同步定时方式

- 2.异步定时方式

- 三、总线的性能指标

- 四、总线标准

- 五、总线仲裁

- 1.集中仲裁方式

- 2.分布仲裁方式

- 六、系统总线的结构

- 1.单总线结构

- 2.双总线结构

- 3.三总线结构

- 附:王道课后选择题笔记

一、总线基本概念

总线是一组能为多个部件分时共享的公共信息传送线路。

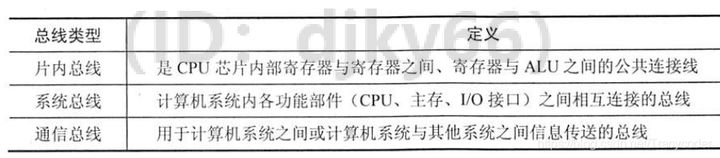

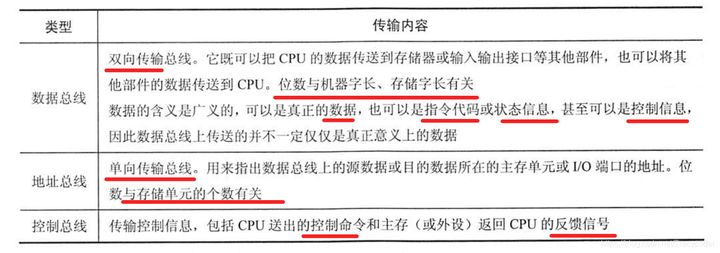

- 系统总线又分为以下几种:

- 总线传输的四个阶段:

①申请分配阶段:分配下一周期的总线使用权,包括传输请求、总线仲裁。

②寻址阶段:取得主模块要访问的从模块的地址和命令。

③传输阶段:主模块和从模块进行数据交换,单向或双向。

④结束阶段:信息从总线撤除,让出总线使用权。

- 总线设备

主设备:获得总线控制权的设备。

从设备:指被主设备访问的设备,它只能响应从主设备发来的各种总线命令。

- 猝发传输方式:在一个总线周期内传输存储地址连续的多个数据字,也就是说一次传输一个地址和一批地址连续的数据。

本文详细介绍了计算机组成原理中的总线概念,包括总线的基本概念、定时方式(同步与异步)、性能指标、标准、仲裁机制以及系统总线的结构,特别强调了总线猝发传输方式及其优势。

本文详细介绍了计算机组成原理中的总线概念,包括总线的基本概念、定时方式(同步与异步)、性能指标、标准、仲裁机制以及系统总线的结构,特别强调了总线猝发传输方式及其优势。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3169

3169

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?