差分对的约束设置

第一步,差分对的设置

差分对的设置有很多方法,下面介绍两种最常用的方法。

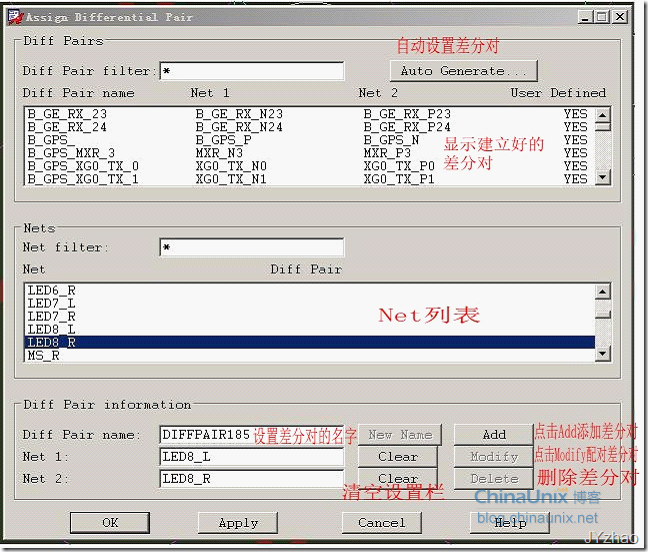

1. 点击菜单Logic→Assign Differential Pair... 弹出以下对话框。

点击你想要创建差分对的Net1和Net2,填入差分的名字,点击Add后就成功创建了差分对。

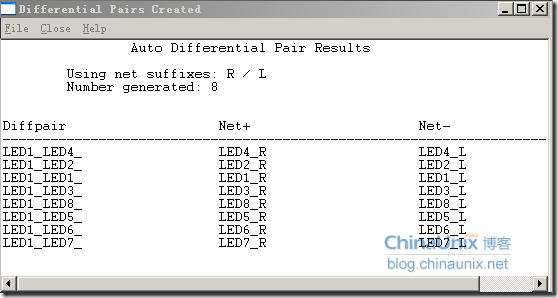

点击Auto Generate按钮后,弹出以下对话框:

在第一个输入框填入Net的主要名字后,在下面的框中填入差分线的标志如N,P。点击Generate即可自动产生差分对。

2.在约束管理器中设置差分对。

在DSN上点击右键,在菜单中选择Create→Differential Pair。即可弹出下面的对话框。

和上一种方法的设置差不多,这里就不再叙述了。

第二步 差分对约束规则的设置

差分对各项约束可以在约束管理器中的Electric→Net→routing→Differential Pair中直接在各差分对上填入各项约束数值就可生效,但更好的方法是创建约束规则后赋给各个差分对。

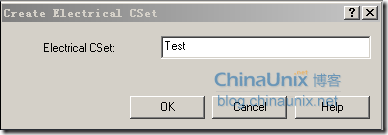

在DSN上点击右键,在菜单中选择Create→Electrical CSet后,弹出下面的对话框;

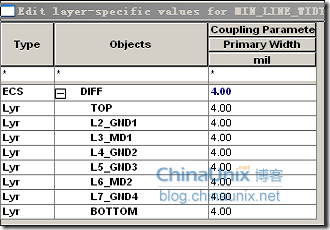

输入规则名后点Ok,在Electric→constraimt set→outing→Differential Pair中可以看到新规则。

在表格中输入各项数值即可完成新规则的设置。如图所示

差分对约束参数主要有以下几个:

1coupling paramaters 主要包括了

Primary Gap 差分对最优先线间距(边到边间距)。

Primary Width 差分对最优先线宽。

Neck Gap 差分对Neck模式下的线间距(边到边间距),用于差分对走线在布线密集区域时切换到Neck值。

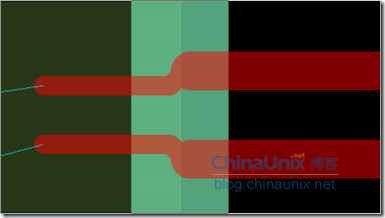

Neck Width差分对Neck模式下的线宽,用于差分对走线在布线密集区域时切换到Neck值。如图所示

设置数值时在表格中右键菜单中选择change,会出现以下各层数值表格,可以在每一层上设置不同的数值。

需要注意的是在物理(physical)约束中同样可以设置差分规则,但是电气规则约束在布线时更优先,同时电气规则可以设置更多的约束,推荐在电气规则中设置差分走线的约束。

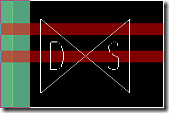

2 Min Line Specing 差分对最小间距,一定要小于或等于"Primary gap"与(-)tolerance的数值,并且也要小于或等于"Neck gap"与(-)tolerance的数值。对于不符合约束的差分对,会显示“DS”的DRC错误提示。

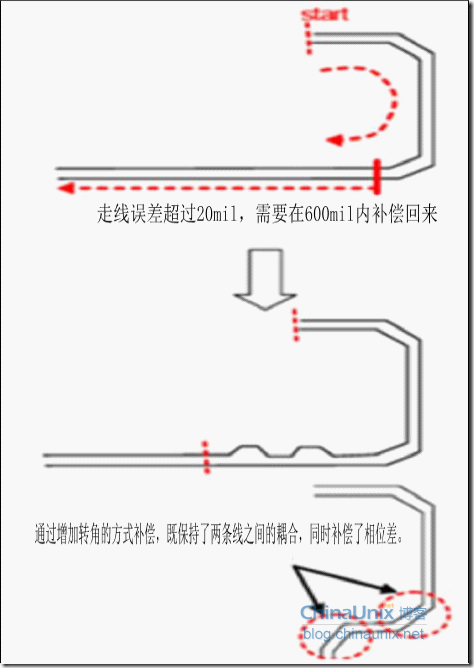

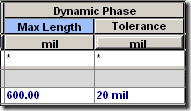

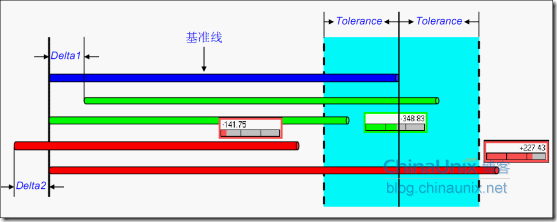

3 Dynamic Phase:动态相位检查,在16.3版本新加入的功能。对差分对路径中每个转角之间造成的路径差异进行检查。如在整个差分对网络中,正向与反向之间的走线差距不能超过“x mils”。如果整个路径中的某一个位置,发生了两个信号之间相位偏移超过了规定的“x mils”,这个误差必须在“y mils”范围内补偿回来。如下图x=20,y=600.设定约束时tolerance填入x值,max length填入y值。

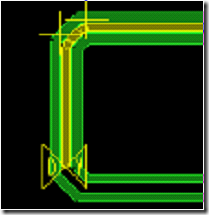

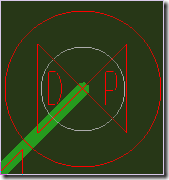

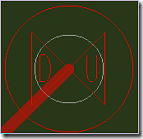

对于不符合约束的走线的路径会以高亮显现,并且显示DY错误。

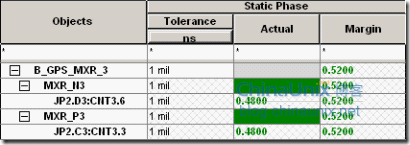

4 Static Phase Tolerance 这个约束设置了两根差分线之间的差值,单位是mil或ns。

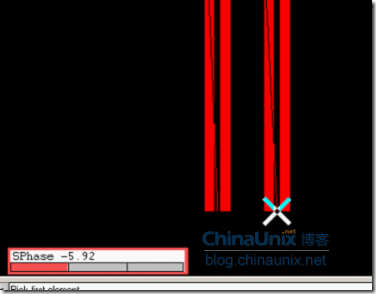

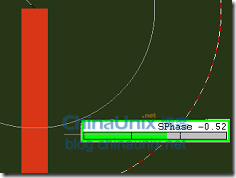

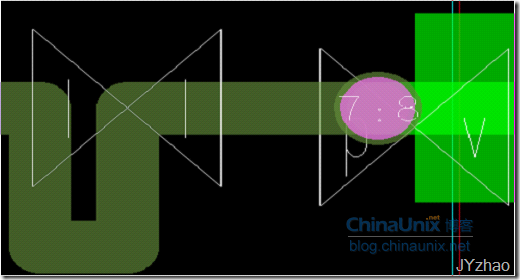

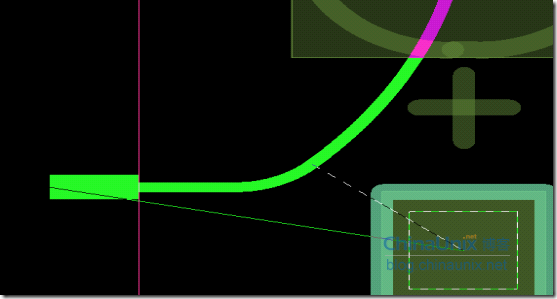

设置了此项后,在走线时会实时的显示走线差,在绿灯时符合约束。如图

在Net→routing→Differential Pair中也可以看到实际的值。

需要注意的是布线时“SPhase”显示的是裕量值(Margin),而并非实际值(Actual)。

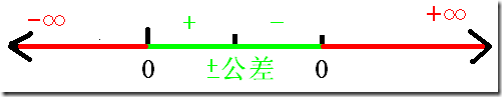

裕量值的范围

如图所示在-∞到+-公差区间内,实际线长比目标线长要短,裕量值为实际值—目标值+公差。绿灯0意为实际值比目标值少公差值长,+裕量值越大意为实际线长越接近目标线长。

在+∞到+-公差区间内,实际线长比目标线长要长,裕量值为实际值—目标值—公差。

—裕量值越大意为实际线长越接近目标线长。

对于不符合约束的差分对会显示”DP”的DRC错误提示。

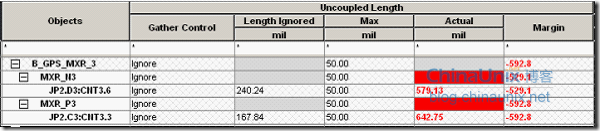

5 Uncoupled length:该约束限制了差分对的一对网络之间的不匹配长度。差分对刚刚从芯片出来的走线通常是不耦合的,“gather contrlo”可以设置为“ignore(忽略)”和“include(包括)”,意思为在计算不匹配长度时是否包含差分对刚从芯片出来的这段不耦合的线长。在在Net→routing→Differential Pair可以查看具体的数值。

间距约束规则设置

间距约束设置有两种方法;1,直接在spacing→net→all layer中填入各项数值。

2,创建约束规则,赋给各net。这种方法管理方便,在 Physical 和 Spacing 设置中用后者比较好。

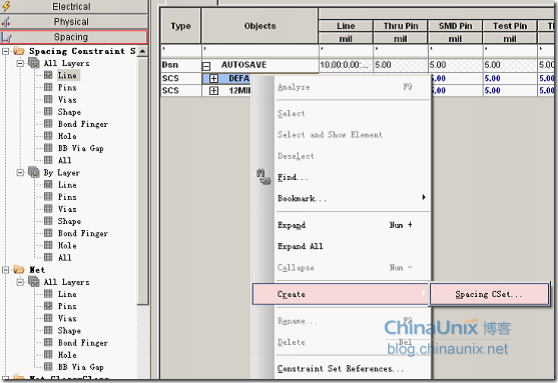

1, 创建规则

如图,点击右键后选择Create→Spacing Cset。

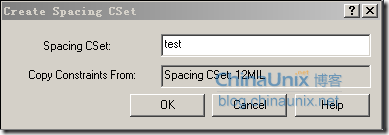

输入名字后点OK。

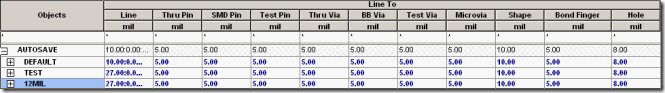

2.设计规则

图示中的为all layer-line中的内容,可以设置连线到各个要素的约束,在all layer中还有其他的内容的约束,和图示内容基本一样,可以分别设置。

设置好后可以在all layer-all中查看一下,这里包括了所有约束的内容。

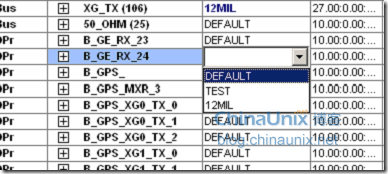

3.赋予规则

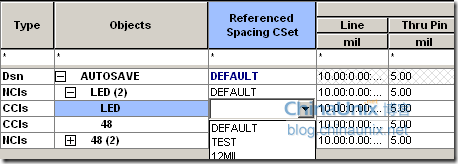

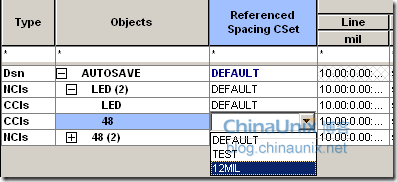

在net-all layer中,设置Referenced Spacing Cset栏即可选择不同的约束规则,如图所示。

Net class-class的间距设置

NCIs(NET CLASS)由众多nets或者buses、differential pairs、Xnet所组成的类,可对其赋予相似的约束。

NCC(Net Class-Class)也就是设置不同class组相遇后的间距设置。

首先建立class组。

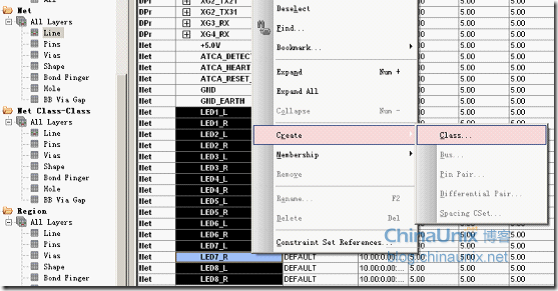

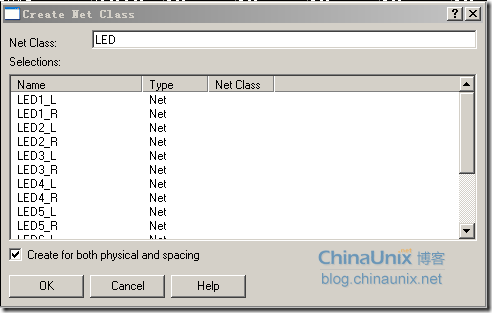

首先在net-all layer中复选多个对象,右键后选择Create-Class。

输入Class名后即可建立class。

设置class-class规则

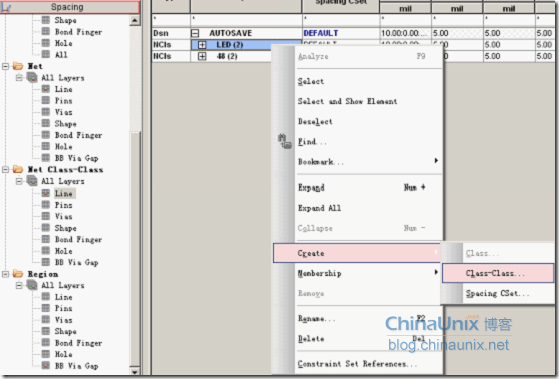

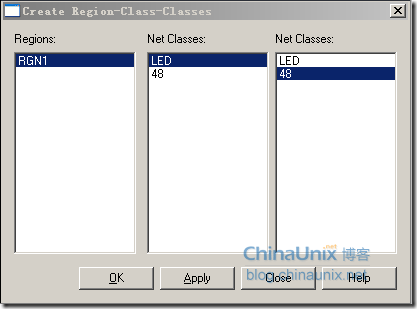

如图,在Net Class-Class – all layer中点击右键选择Creat- Class-Class,即可弹出以下对话框。

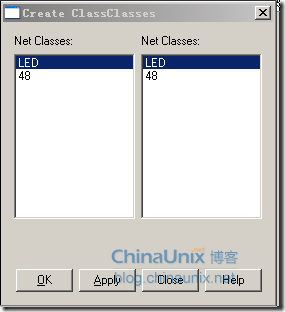

分别选择不同的class组后即可建立class-class对。

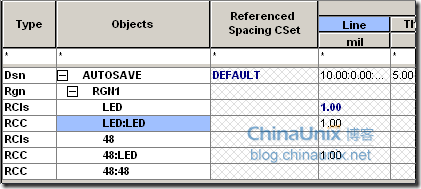

如图,CCls LED设置的是class组LED内部的间距规则。

CCls 48设置的是class组LED对class组48的间距规则。

same net spacing工作表

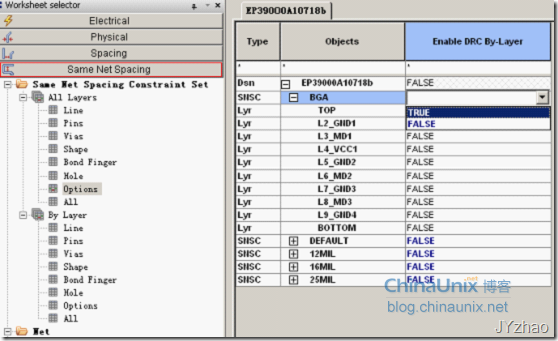

在Spacing工作表下还有same net spacing工作表,用于对同一网络上的不同元素进行间距约束。在16.2以前的版本中只能选择是否开启same net DRC检查,16.2后专门独立出一个工作表,可以设置详细的数值。

规则设置和Spacing规则设置没有多少差异,可以和Spacing规则设置的一样。

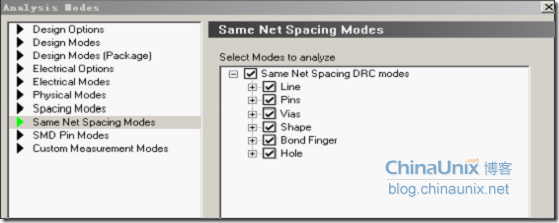

需要在Analysis – Analysis Modes -- same net spacing Modes中开启分析选项,如图。

并在same net spacing – Options中开启相应层的DRC选项,如图。

为了避免和Spacing DRC混淆,Same Net Spacing DRC显示为小写,如图。

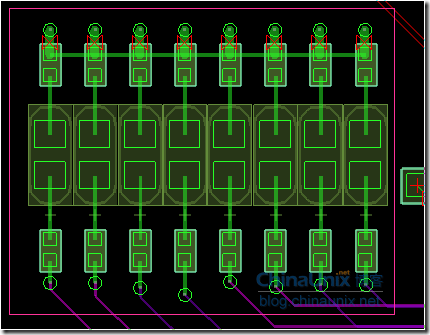

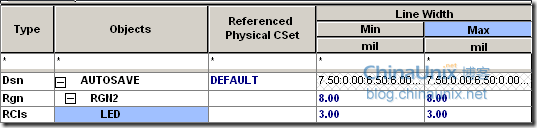

区域约束规则设置

region约束就是15.X 的 Area 约束。在pcb布线时有些区域比如bga封装区因为过孔密集需要特殊的线宽线距约束,此时设置region就可以满足要求

首先,创建region区域。

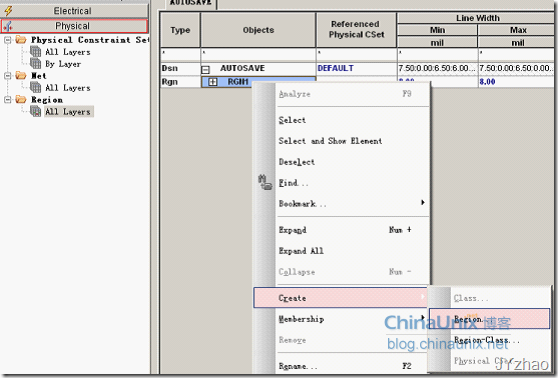

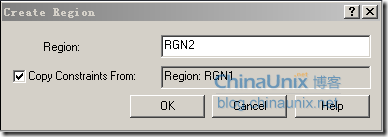

在physical或者 spacing工作表下新建一个区域(Region)约束。

输入名字。

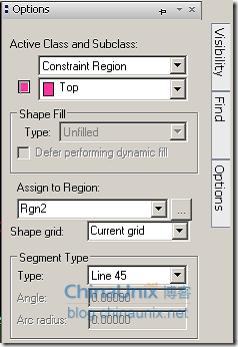

建立完成后,在pcb板上画出一个区域。选择 shape-regtanglar,注意在右边的options 窗口中,active class subclass 选择 constrait region,选定你需要约束的那一层,在 assign to region 里选择刚刚建好的好个区域规则(RGN2)将这个规则指定到这个区域中。

建好了region就可以赋予相应的规则了。

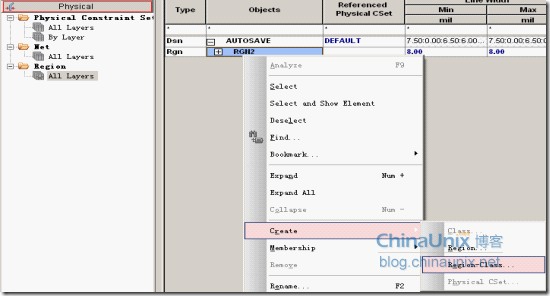

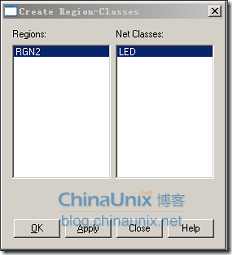

建立区域物理规则

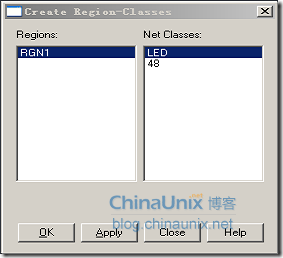

如图,在菜单中选择Create – region-class,弹出的对话框中选择需要约束的class组,就可以建立在该区域下class组的走线物理约束规则。

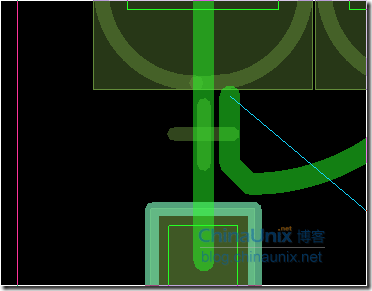

设定好约束后,在region区域就会按照特定的规则走,出了region后就按照一般的规则走。

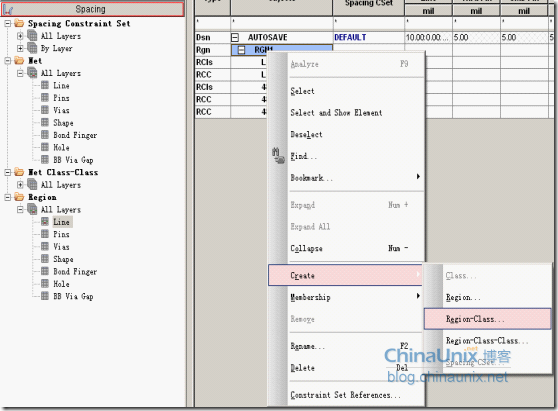

建立区域间距约束规则

创建region-class规则

如图,在菜单中选择Create – region-class,弹出的对话框中选择需要约束的class组,就可以建立在该区域下class组的走线间距约束规则。

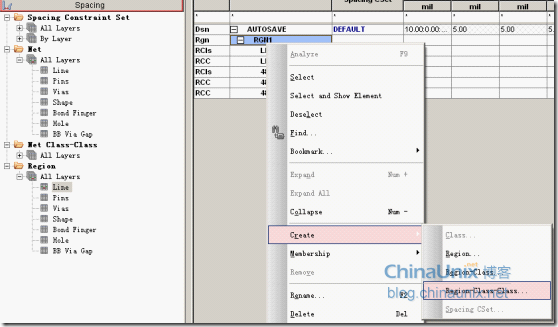

创建region-class-class规则、

如图,在菜单中选择Create – region-class-class,弹出的对话框中选择需要约束的两组class组,就可以建立在该区域下两组class组相遇时的走线间距约束规则。

如图所示,在区域内设置两线最小间距1mil,布线时间距不少于1mil就不会有DRC错误。

等长约束设置

首先设置管脚对(pin pair).

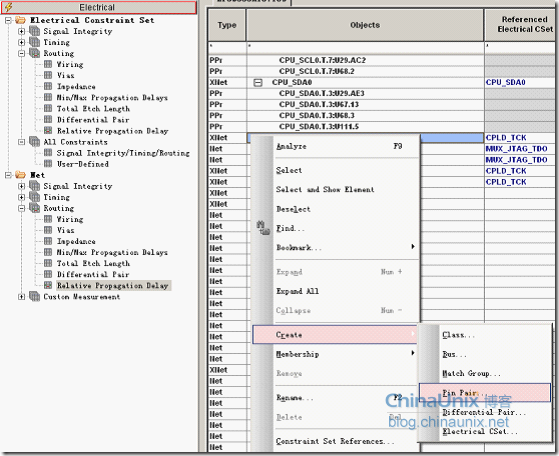

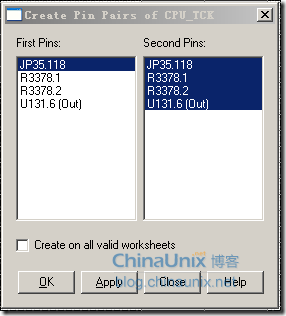

在Electrical-net-Relative Propagation Daley工作表中,选中要建立的网络名,右键选择Create-Pin Pair。

在弹出的对话框中选择管脚。

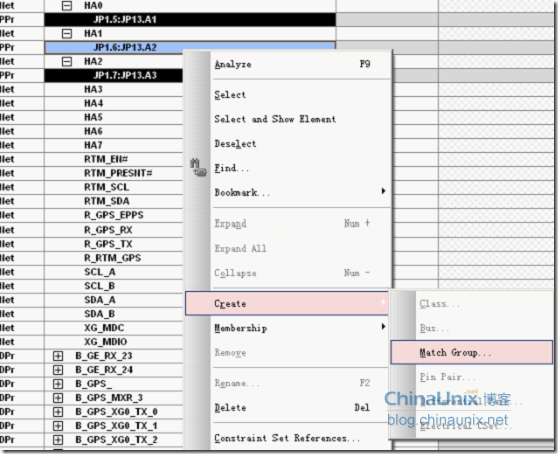

创建match group

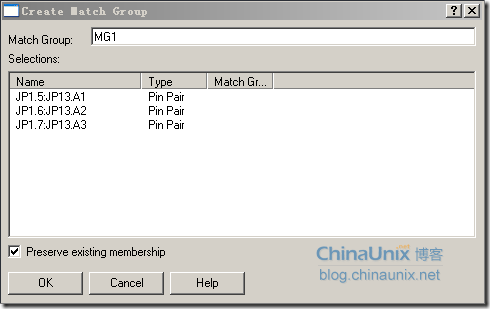

将所有设置等长的网络创建好的管脚对后,选中管脚对,右键选择create-match group。

输入名字后即可创建match group。

等长设置

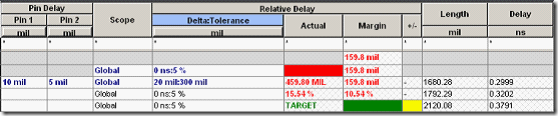

设置好match group后就可设置等长了。主要设置参数如下图所示

Scope:可以选择Local和global。Local意为仅比较同一Net或XNet内的管脚对,Global意为比较同一Match Group内的所有管脚对。一般选择Global即可。

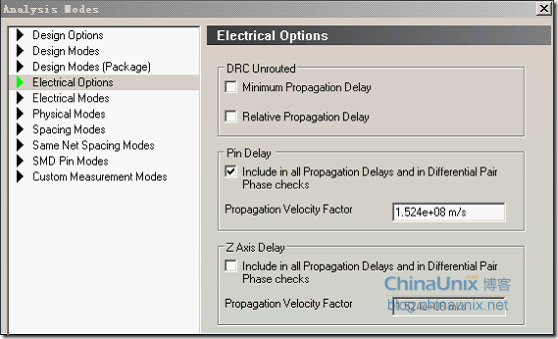

Pin delay:大多是在pin之间的延时不一致时,需要做一个补偿,那就需要设置pin delay,指的是IC包装内部的长度。需要在菜单Analyze -> Analysis Modes填入->Options.勾Analyze选PinDelay开启此功能。打开后,在计算线长时就会包括这段线长。

另外pin delay下的Z Axis Delay指的是计算线长时是否考虑Via的长度,设置好了叠层参数后就会加上via的长度。

delta:tolerance:这项控制了match group内的线长差。单位有三种:ns,mil,%;单位%指以目标线的N%为公差。对已经走好的线,以最长值为目标线。

Delta指的是基准线比目标线长还是短,长则写入+delta值,短则写入-delta值,和目标线一样长则写入0,计算公差时的基准线便是目标线长加上delta值的结果。如上图,target线长2120.08mil,delta值为20mil, 计算差值时就是(2120.08+20)-1680.28=459.80mil。

Tolerance值为于基准线的误差,是+/-误差。如果写50mil其实为+50/-50mil误差,实际为100mil的误差。一般设置等长时Delta为0,有特殊需要时可以考虑设置delta值。

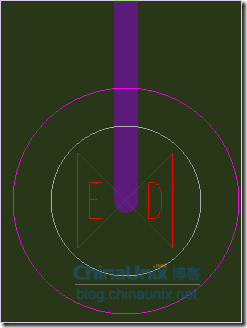

对不满足约束的走线,显示“ED”错误,如图所示。

电气规则规则设置内容

(1)Net/Singal Intergrity工作表中包括了Electrical Properties,Reflection,Edge Distortions,Estimated Xtalk,Simulated Xtalk和SSN六种用于设置电气属性的选项。不同的选项可以进行不同属性的设置,具体内容如下。

1 Electrical Properties选项。

Frequency:表示网络的频率。

Period:表示网络的周期,如果在Frequency项中输入了具体的数值,在周期栏中会自动算出频率,相应的当输入具体周期的数字是频率也会自动出现。

Duty cycle:表示占空比。

Jitter:表示时钟抖动值。

Cycle to measure:表示仿真时测量数据的周期。

2 Reflection选项

overshoot在max列中输入过冲约束。在“hign actual”选项中出现的为网络的实际高,低电压,在“margain”选项中显示的为最差情况的实际值和“max”的差值。

Noise Margin在“min”选项中出现的最小裕量约束吗,参考点为接受端的高和低阀值。

3 Edge Distortions选项后,可进行如下特性设置。

Edge secsitivity:标记网络或者扩展接受端是否对单调性敏感。

First incident switch:标记第一个波形到了时,是否需要转换。

4 Estimated Xtalk选项

Active window:表示网络正处于转换或者产生噪声的窗口。

Senstive window:表示网络处于稳态和易受干扰的状态窗口。

Ignore nets:表示计算串扰时可以忽略的网络。

Xtalk:在“max”列填写受扰网路上最大允许的串扰。

peak xtalk:在“max”列填写一个干扰网路对受扰网络上产生的最大可以允许的串扰。

5 Simulated Xtalk选项。该工作表的约束内容与Estimated Xtalk工作表的约束内容相同,区别是Simulated Xtalk工作表用于查看仿真的串扰结果;Estimated Xtalk工作表用于预测串扰结果。

6 SSN选项

Max SSN:最大同时转换噪声,单位MV。

Power bus name:电源总线名。

Ground bus name:地总线ming。

Actual:实际噪声。

Margin:裕量,如果为负值,则将会有冲突发生。

(2)设置时序规则

1 Switch/settle Delays工作表。Switch/Settle Delays工作表主要用于设置可以允许第一个转换延迟和最大的建立延迟,通过仿真对实际值和约束值进行比较,得出裕量值。

2 setup/Hold工作表。在Setup/Hold工作表中可以填写时钟的网络名称,周期,时钟延迟和时钟偏移等数值,将这些数值进行最终的比较,会得出所创建的系统是否符合元件要求的建立保持时间。

(3)设置走线规则

1 wiring选项

topology如果“verify schedule”选项设置为“yes"则进行DRC检查,最大同时转换噪声,转换的单位为MV,格式为”高“或者“低”,单击“schedule”栏中所对应的表格,在下拉列表中可以选择预置的几个拓扑结构,包括菊花链(dasiy-chaim),星形(star)等拓扑结构。

Stup length:设置菊花链走线时的最大短桩长度。

Via count:设置在表层走线的最大长度。

Parallel:设置并行走线线段的线宽和线距约束。

2 Impedance选项。可以在Impedance工作表内进行目标阻抗和偏差的设置,通过计算可以得出实际值和裕量。注意叠层和材料的设置一定要正确,这样才能得出正确的结果。

3 Min/Max Propagation Delay选项。在Min/Max Propagation Delay工作表内可以进行引脚允许的最大和最新传输延迟设置,单击Pin Pair所对应的表格,出现的下拉列表中具有Longest/shortest PIn Pair,Longest/shortest Driver/Receiver和All Drivers/all Receivers等选项。

Longest/shortest PIn Pair:将最小的延迟约束赋给最短的引脚对,将最大的延迟约束赋给最长的引脚对。

Longest/shortest Driver/Receiver:将最小的延迟约束赋给最短的驱动/接受器引脚对,将最大延迟赋给最长的驱动/接受引脚对。

All Drivers/all Receivers:将最大,最小约束赋给所有的驱动/接受引脚对。

(4)Total Etch Length选项。在Total Etch Length工资表内可以设置走线的最大和最小长度,在该工作表中具有两项工作栏,分别是unrouted net length栏和routed manhattan ratio栏,前一个工作栏用来设置估计的走线长度,后一个工作栏可以显示实际的曼哈顿比例。

(5)Differential Pair选项。见差分对约束设置。

(6)Relative Propagation Delay选项。在Relative Propagation Delay工作表内可以进行对匹配的传输延迟的设置。见等长约束设置。

本文深入介绍了电子设计自动化中差分对的设置方法及电气规则约束,包括差分对的创建、约束规则的定义、间距约束、区域约束和等长约束等内容。此外,还详细阐述了电气规则的设置,如Net/SingalIntegrity工作表、时序规则、走线规则、TotalEtchLength工作表、DifferentialPair选项和RelativePropagationDelay选项等。

本文深入介绍了电子设计自动化中差分对的设置方法及电气规则约束,包括差分对的创建、约束规则的定义、间距约束、区域约束和等长约束等内容。此外,还详细阐述了电气规则的设置,如Net/SingalIntegrity工作表、时序规则、走线规则、TotalEtchLength工作表、DifferentialPair选项和RelativePropagationDelay选项等。

7830

7830

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?