描述

首先,这里跑linux主要是PS部分的,这里暂时不用PL部分。

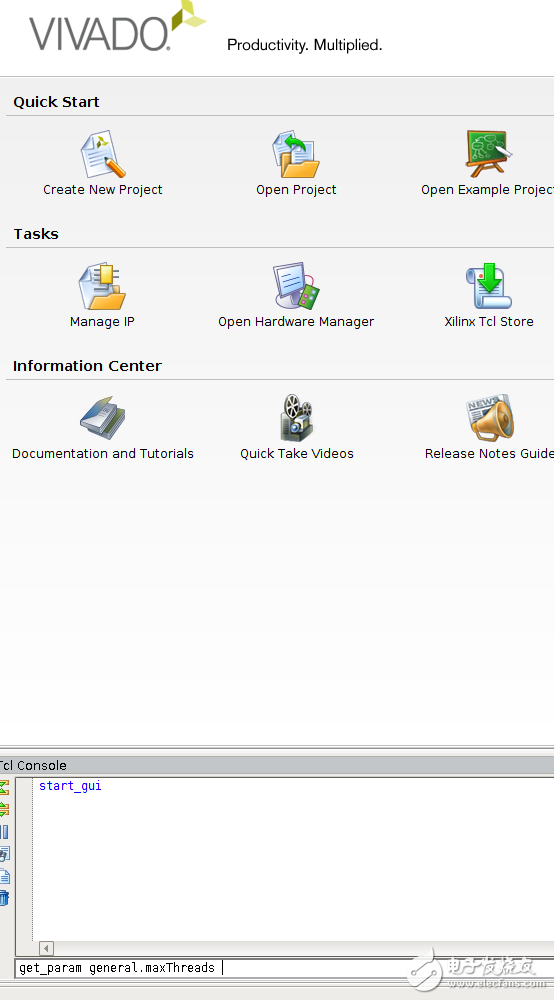

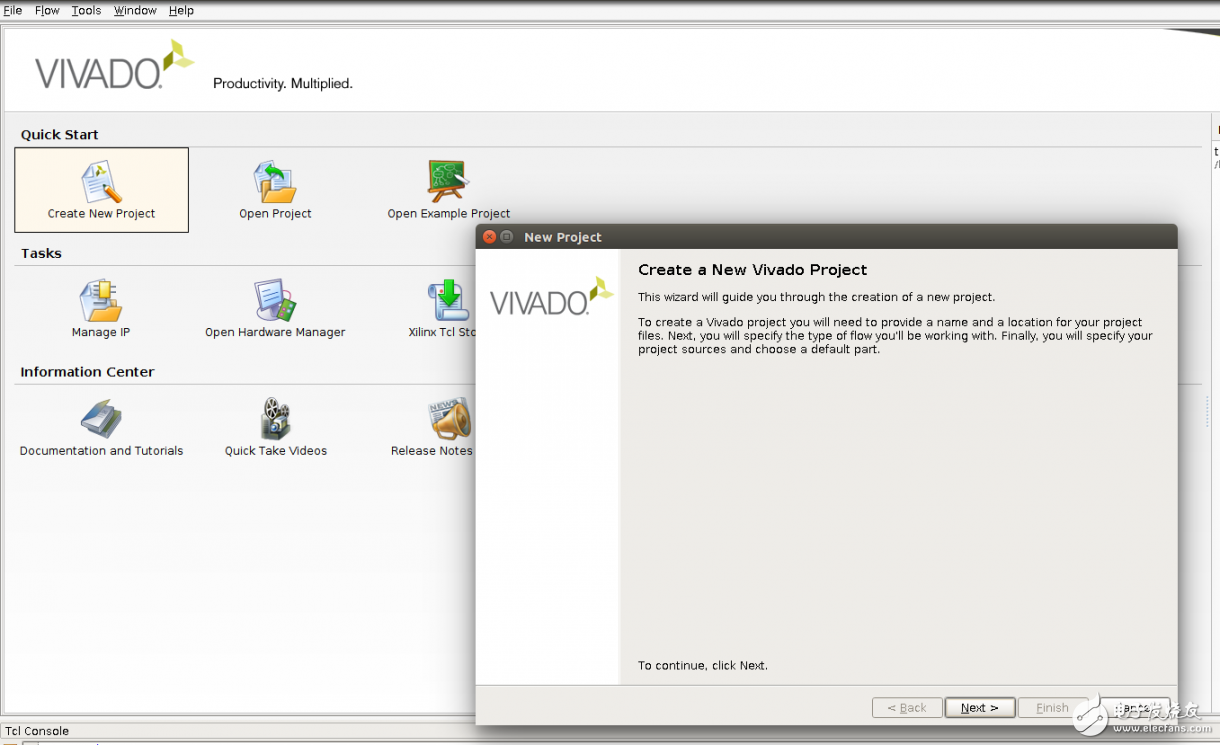

打开vivado新建一个project.

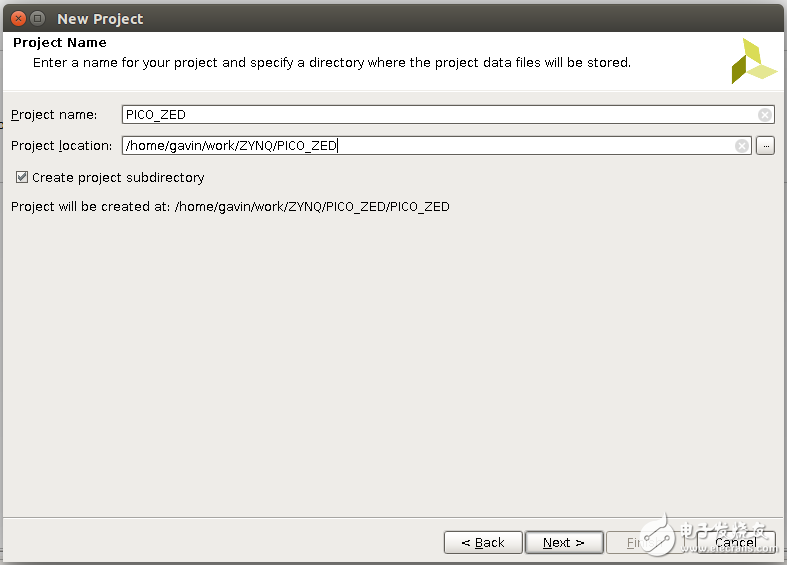

项目名和保存路径

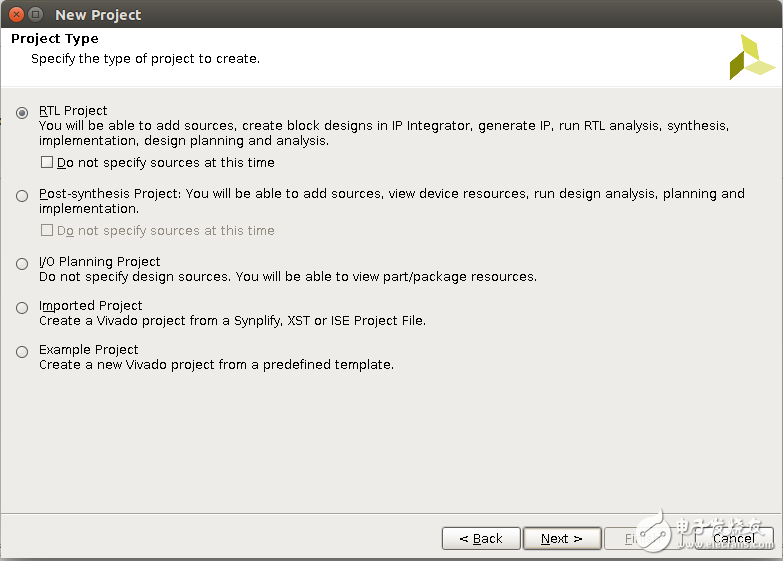

RTL project

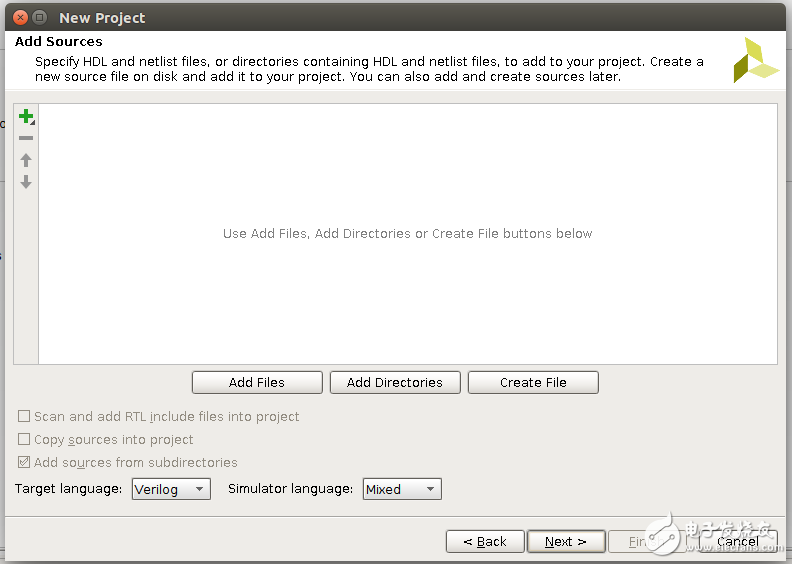

next

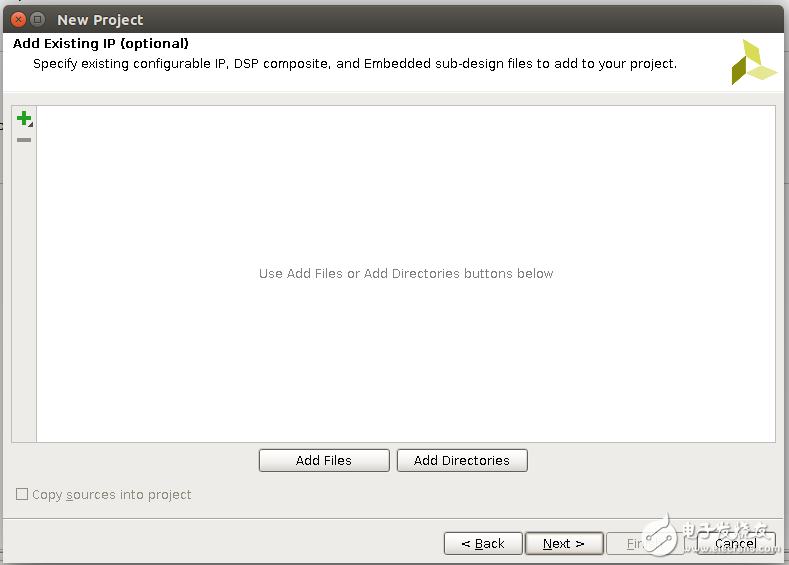

next

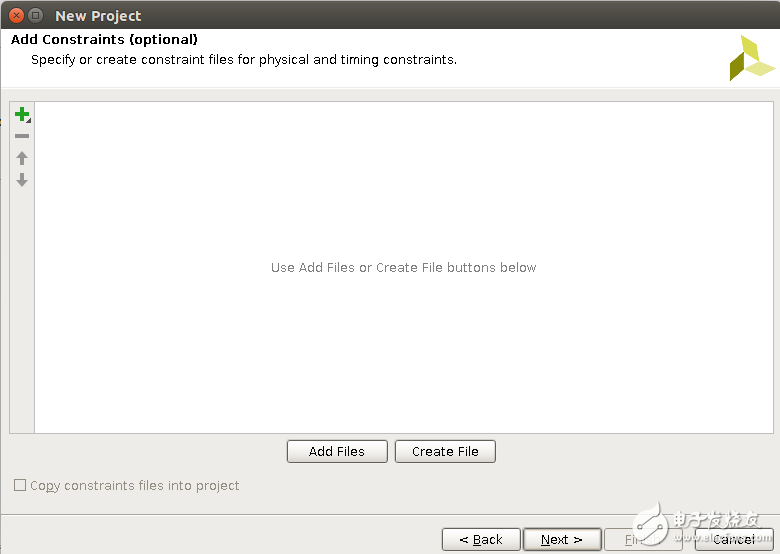

next

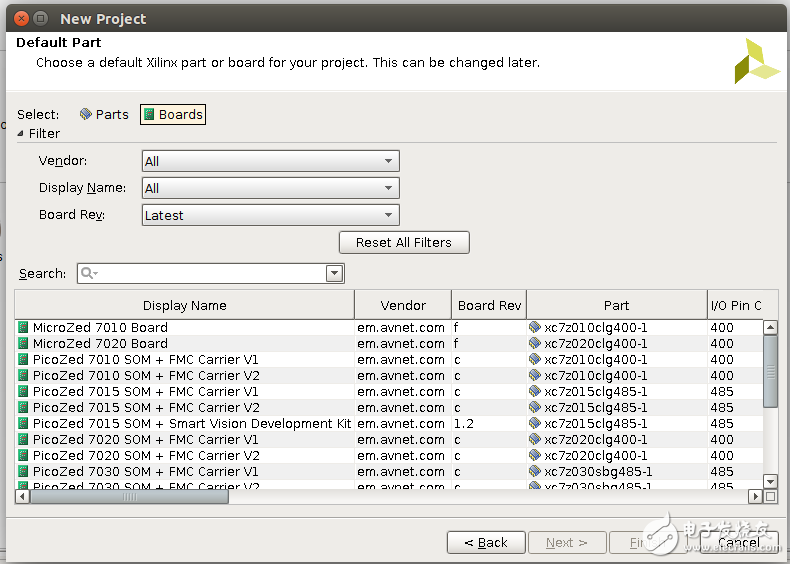

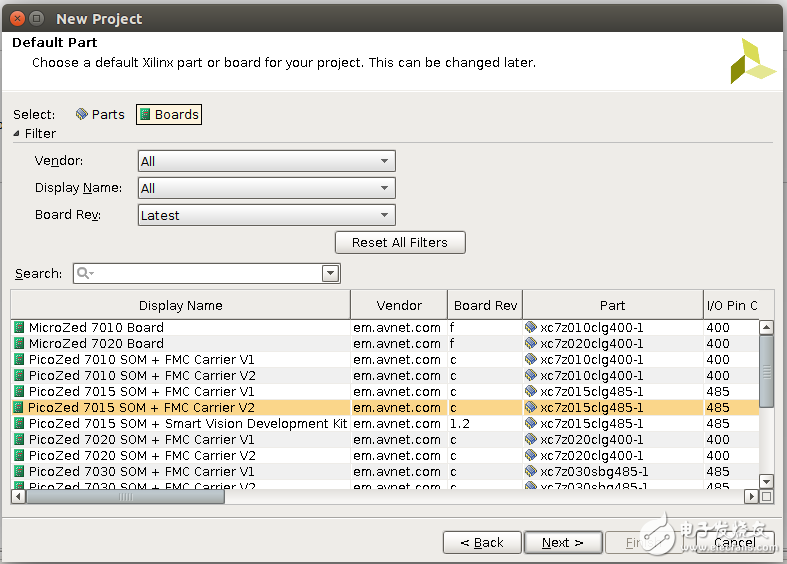

选Board,如果选器件,是一样的,只是需要去根据实际情况设置一些东西。

然后Next

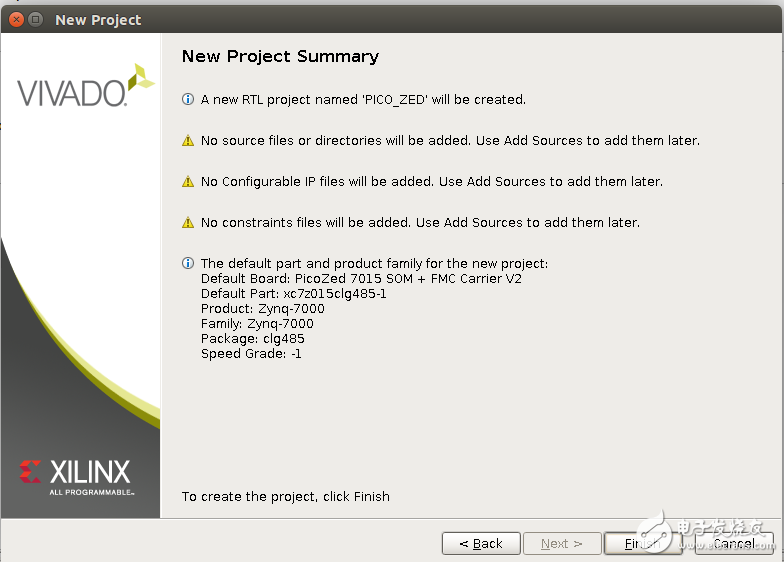

完成。

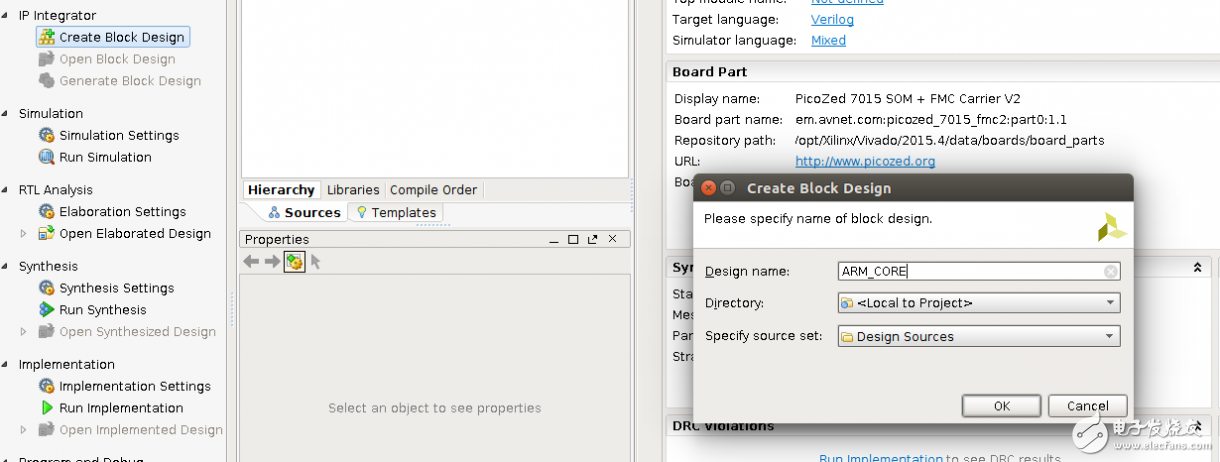

Create Block Design 这里我们需要构建PS核

所以我把Design name改成ARM_CORE,当然,是根据实际情况来,你想怎么命令都是可以的。然后在右则点添加IP,然后选zynq 7000如下图所示。

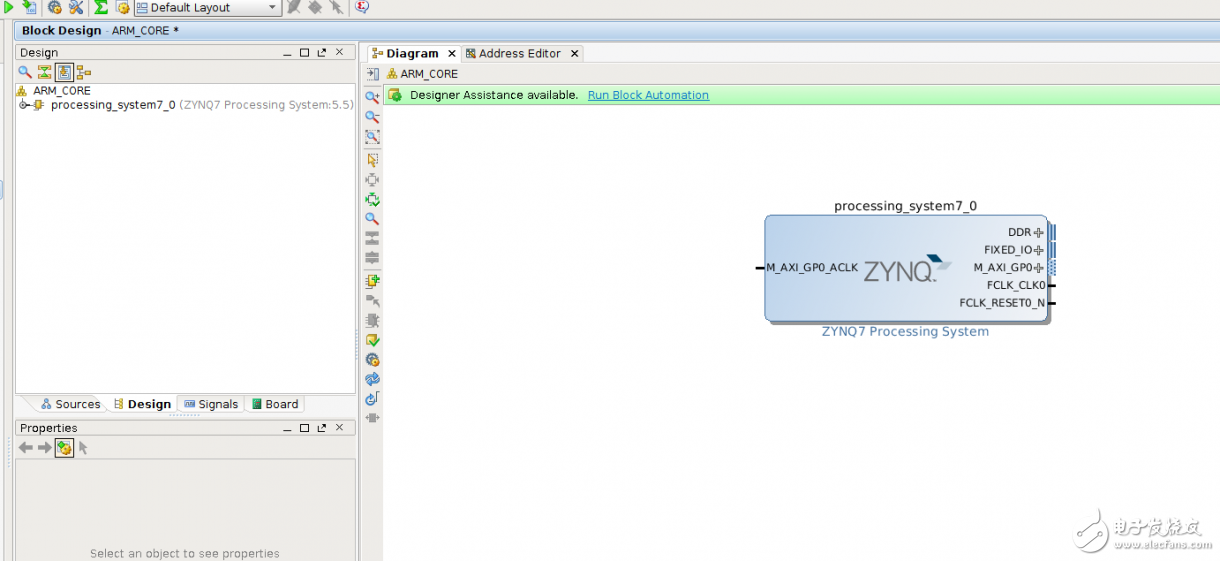

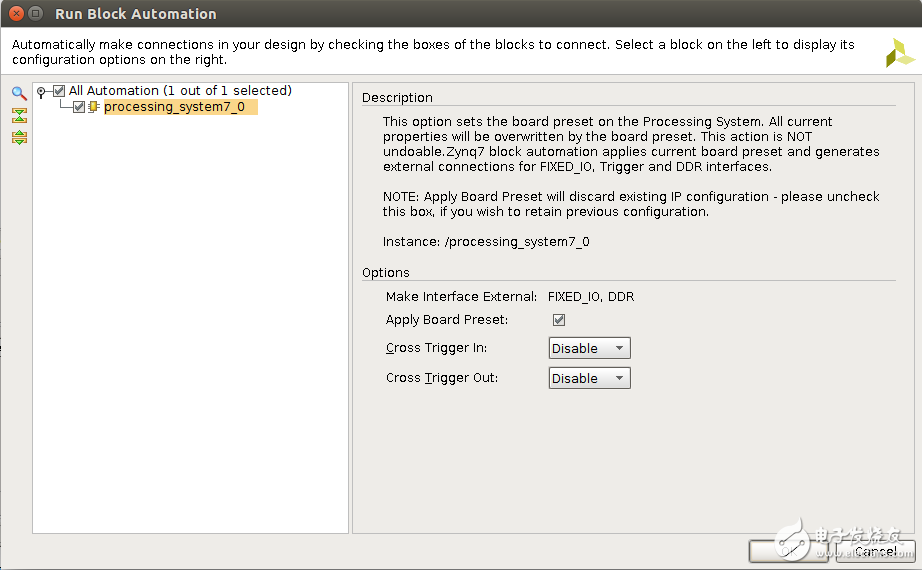

点Run Block Auto...会自动根据所选的板子,自动配置

OK

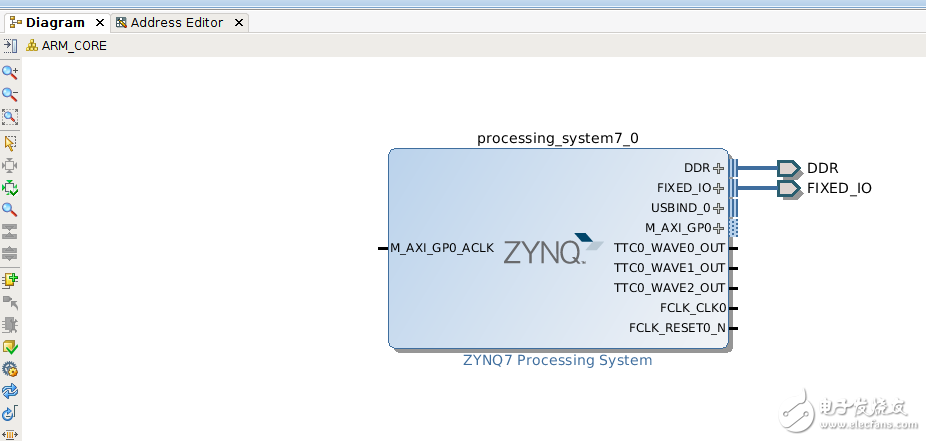

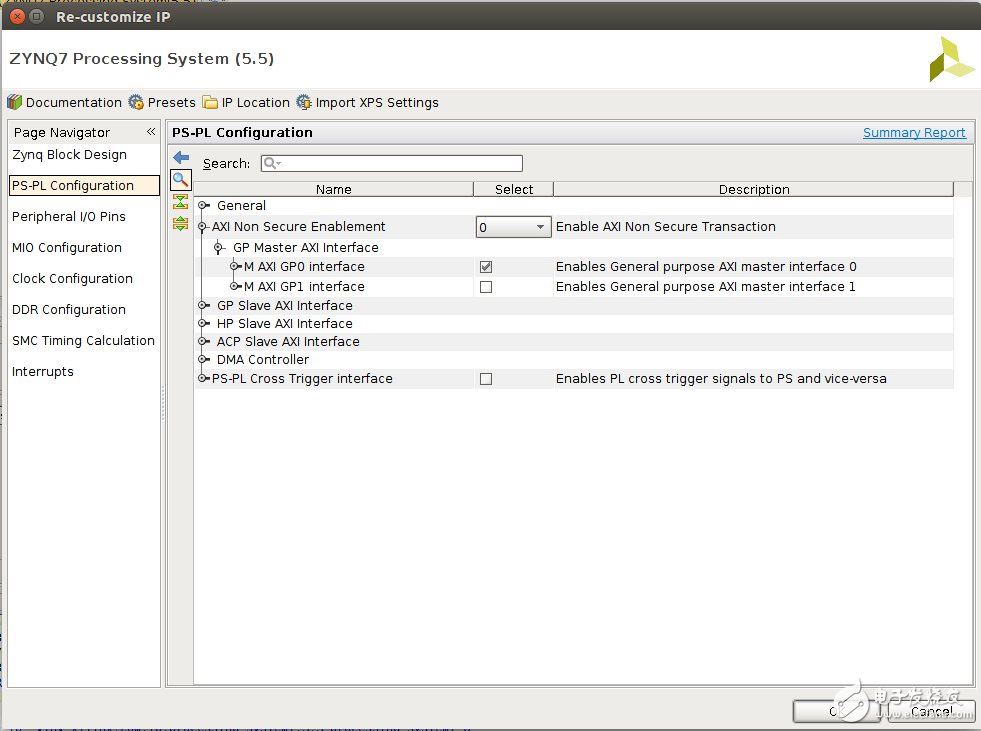

然后双击进去,进行配置,最好能和自己的板子实际情况对应起来,这里对PL部分都不做配置,配置完后保存。

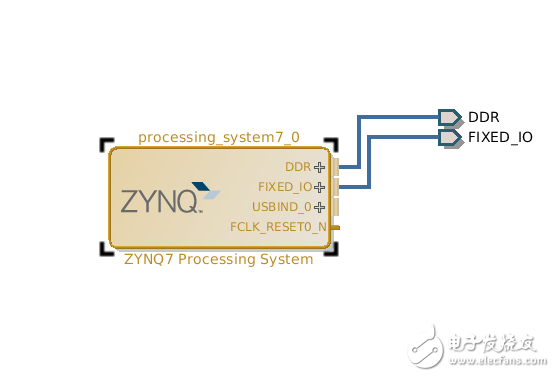

这是配好后的,这样看起来线比较难看,不要慌,右键选regenerate layout

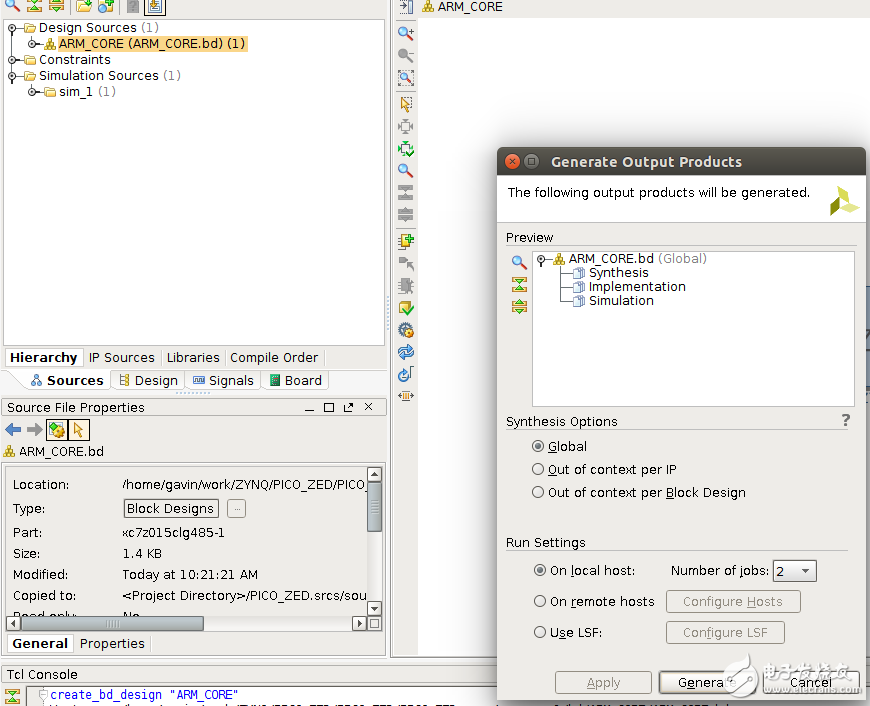

然后在ARM_CORM上右键Generate Output Products

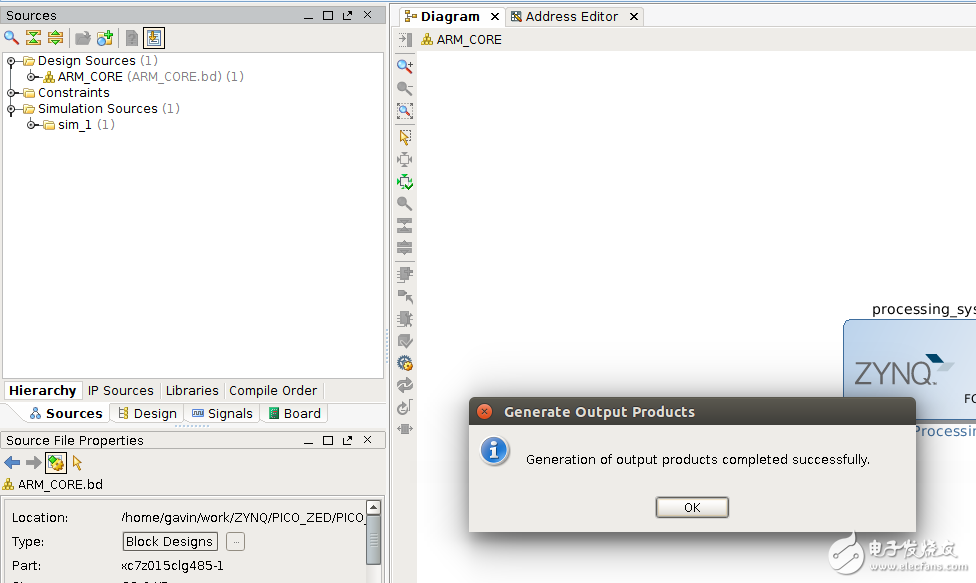

Generate

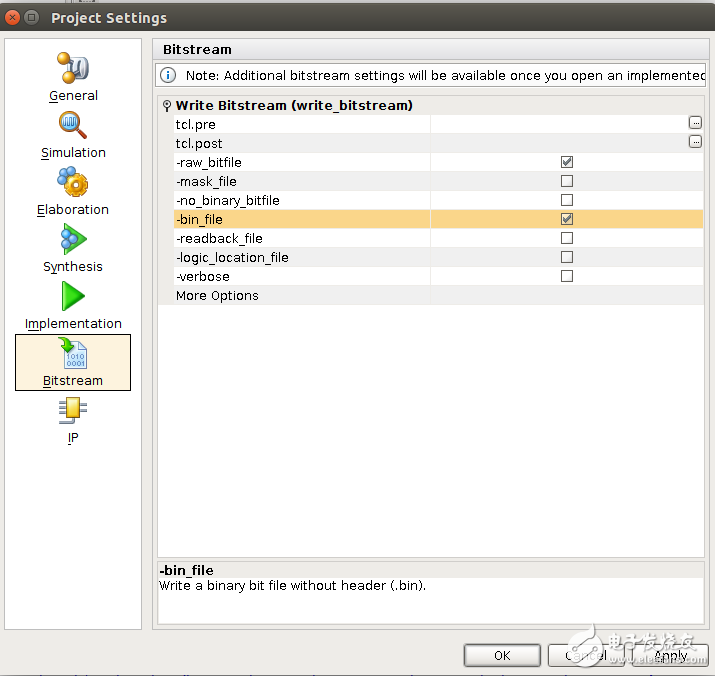

然后在ARM_CORM上右键Create HDL wraper,然后全部保存,因为这个软件是流程式作业,会从头执行到尾,所以我这里设置好bit stream相关的设置

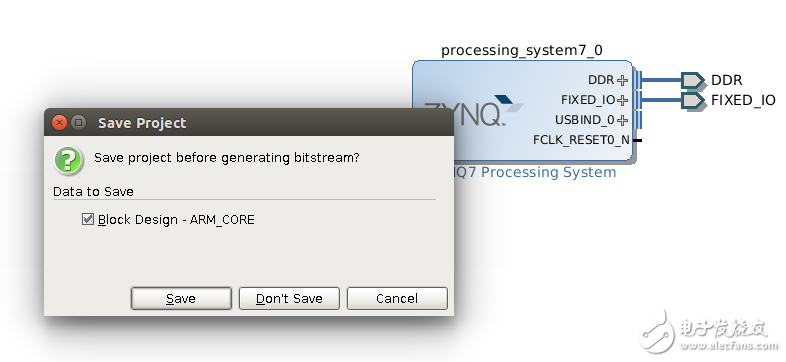

然后点Generate bitstream lic不出问题,正常等待一会儿就会OK.

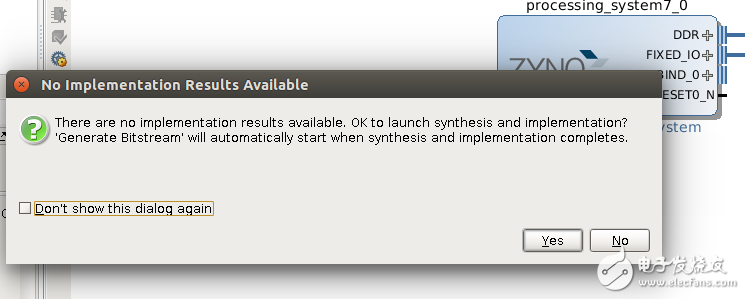

以上是我没有保存才有的提示,如果都保存了,就不会提示了。

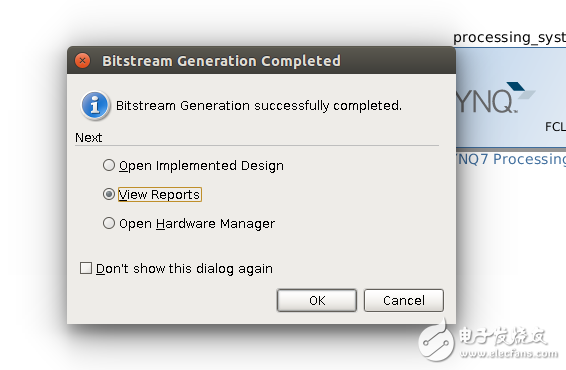

至此,文件都已生成,我们不做其他操作,直接选view Reports就OK了。下一节介绍如何导入到SDK然后新建一个应用工程,生成FSBL.

打开APP阅读更多精彩内容

点击阅读全文

6733

6733

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?