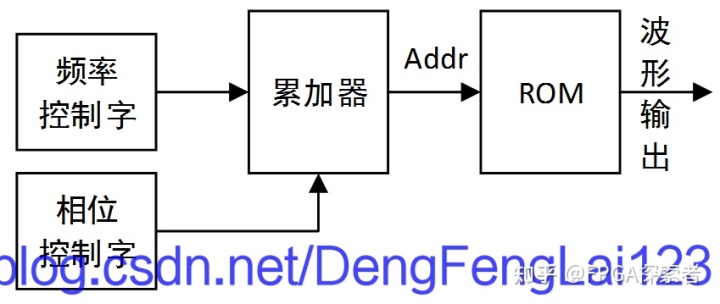

- 系统框图

基于FPGA的DDS信号发生器系统框图如下图所示,采取查表法。

(1)对一个完整周期的波形进行采样,将采样点存在ROM中;

(2)依次给出ROM的访问地址,即可输出一个完整的波形;

(3)通过设置不同的频率控制字可以让ROM的访问地址以不同的步进值访问,这样起到改变输出波形的频率的作用;

(4)通过设置不同的相位控制字可以让ROM的访问时的初始地址改变,这样起到改变输出波形初始相位的作用。

- DDS产生固定频率和固定相位的正弦信号

首先产生固定频率和相位的正弦信号,一个周期采样 256 点,数据位宽为 8 位,需要:

(1)在 ROM 中存储波形,ROM 设置参数:单口ROM,数据深度 256,数

该博客介绍了如何使用MATLAB生成正弦波样本并将其应用于FPGA的DDS(直接数字频率合成)信号发生器。通过Quartus II实现8位计数器,详细步骤包括存储波形到ROM、设置计数器产生地址。最终产生390.625 KHz的固定频率正弦波,不可调幅调频,初始相位为0。仿真验证在Modelsim中进行。

该博客介绍了如何使用MATLAB生成正弦波样本并将其应用于FPGA的DDS(直接数字频率合成)信号发生器。通过Quartus II实现8位计数器,详细步骤包括存储波形到ROM、设置计数器产生地址。最终产生390.625 KHz的固定频率正弦波,不可调幅调频,初始相位为0。仿真验证在Modelsim中进行。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?