FPGA中RAM的使用探索。以4bitX4为例,数据位宽为4为,深度为4。

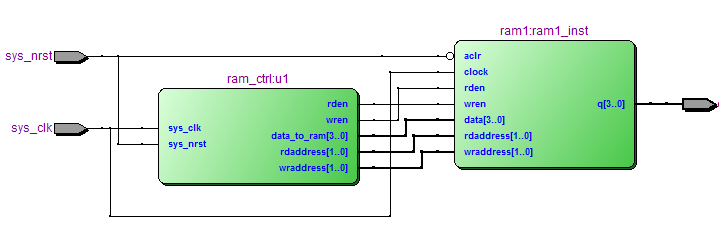

第一种方式,直接调用4bitX4的RAM。编写控制逻辑对齐进行读写。

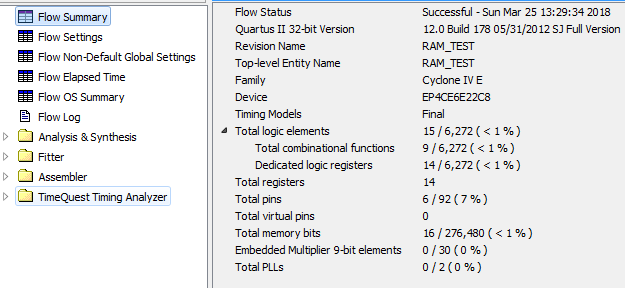

quartus ii 下的编译,资源消耗情况。

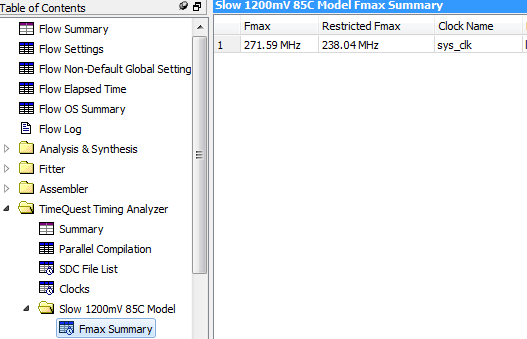

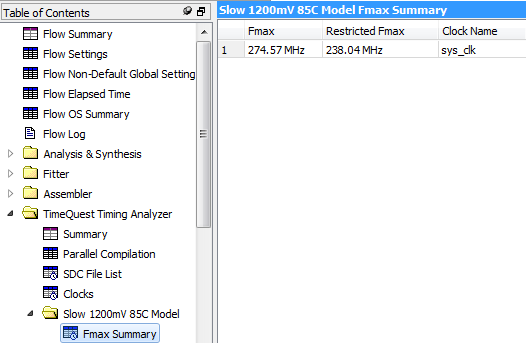

85C模型下的时钟频率。

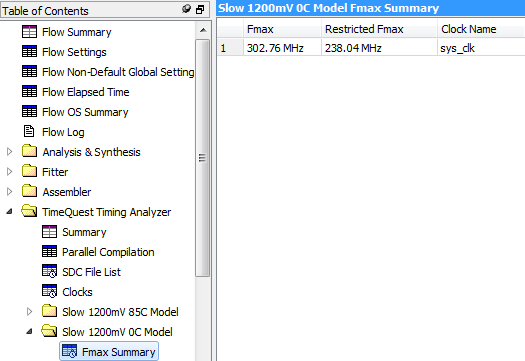

0C模型下的时钟频率。

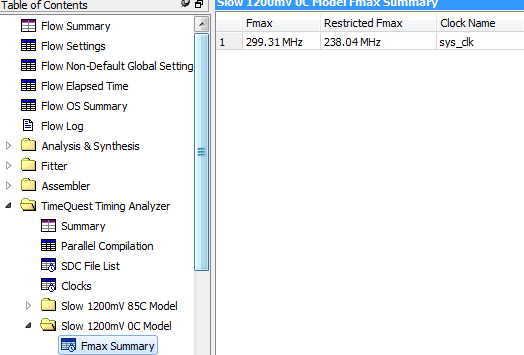

第二种方式,调用1bitX4的RAM,例化4次。编写控制逻辑对齐进行读写。

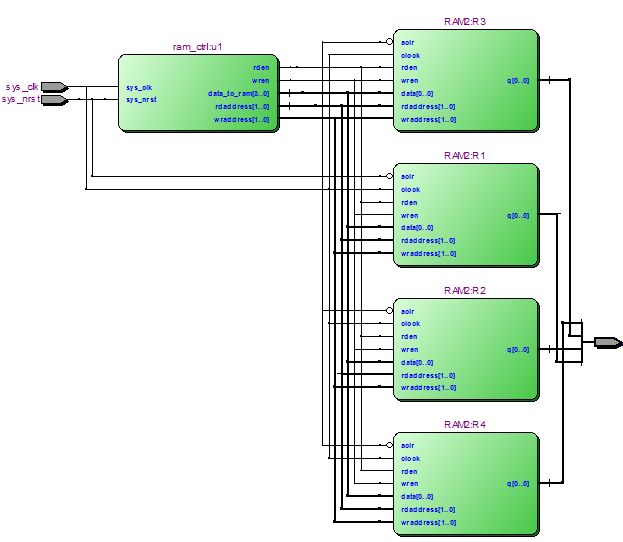

quartus ii 下的编译,资源消耗情况。

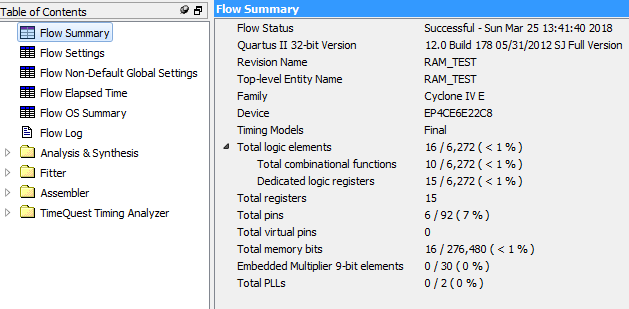

85C模型下的时钟频率。

0C模型下的时钟频率。

从上述两种情况来看,两种RAM的使用方式,最终使用资源比较接近,方案二稍多,而从时序模型综合结果看,方案二的时钟频率明显比方案一高。在高速情况下,建议使用方案二。同样在位宽较宽情况下,可使用生成块语句进行例化,减少顶层对同一模块的例化数,是比较方便的。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?