PCIE设备的Power状态有D0,D1,D2,D3hot, D3cold.

在D0,D1,D2,D3hot状态,设备收到PME_Turn_Off message之后,必须返回PME_TO_Ack。

在任何D状态,下游设备在执行完PME_Turn_Off/PME_TO_Ack之后,必须通过PM_Enter_L23 DLLP来请求进入L2或L3.

如果下游设备被设置成D1/D2/D3hot,它的US Port必须切换link状态至L1。

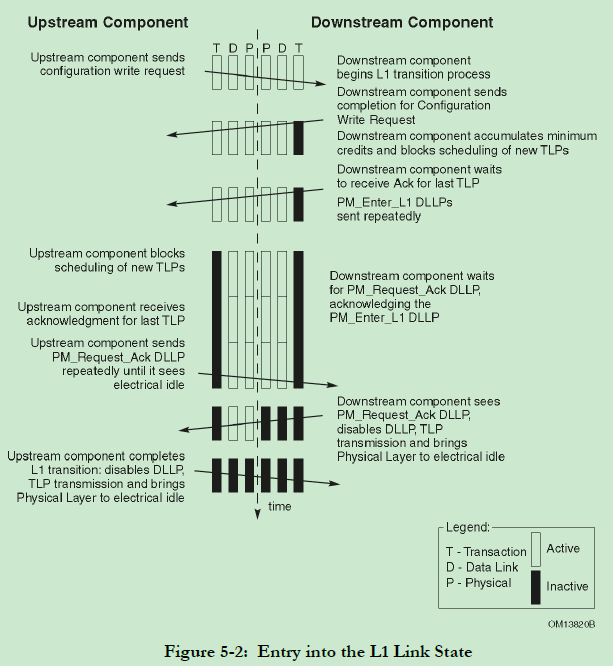

进入L1的过程:

1. PM software通过发送Configuration Write TLP写下游设备的PMCSR寄存器,将下游设备设置成D1(D2或D3hot也可以);

2. 下游设备返回CFG TLP的completion;

3. 下游设备等待足够发送最大的FC DLLP的credit,并停止Transaction Layer层的TLP调度;

4. 下游设备等待上游发来针对completion和所有之前已发送的TLP的acknowledgement,还有可能需要重新发送TLP;

5. 如果所有的TLP都已被acknowledge了,下游设备开始不停地发送PM_Enter_L1 DLLP,中间的间隔不超过4个(8b10b)或16个(128b/130b)symbol 的idle时间。

在期间如果需要发送SKP,SKP不计入IDLE的时间限制。下游设备持续发送PM_Enter_L1直到它收到了PM_Request_Ack。

下游设备能继续接收上游发来的TLP和DLLP,并能返回DLLP,包括FC update DLLP和ACK/NAK DLLP。如果有TLP要发送的话,将会使下游设备进入L1之后立马开始L1的退出过程。

6. 上游设备接收到PM_Enter_L1 DLLP之后,中止所有新TLP的发送;

7. 上游设备必须等到之前发送的TLP的acknowledge,如果需要的话,还会重发retry buffer里面的TLP;

8. 一旦所有的TLP都已被acknowledge,上游设备必须发送PM_Request_Ack给下游,两个DLLP的间隔不超过4个(8b10b)或16个(128b/130b)symbol 的idle时间。

在期间如果需要发送SKP,SKP不计入IDLE的时间限制。上游设备持续发送PM_Request_Ack直到它发现接收端已进入Electrical Idle状态。

9. 一旦下游设备获得PM_Request_Ack,它马上关闭DLLP的发送,并使physical link进入Electrical Idle,以表明自己进入了L1状态。

10. 当上游设备检测到Electrical Idle之后,就停止发送PM_Request_Ack,关闭DLLP的发送,并使发送端进入Electrical Idle状态,来完成L1的进入。

本文详细解析了PCIE设备如何从D状态转换至L1状态的全过程,包括软件配置、下游设备响应及物理链接状态变化等关键步骤,为理解PCIE设备的低功耗模式提供深入洞察。

本文详细解析了PCIE设备如何从D状态转换至L1状态的全过程,包括软件配置、下游设备响应及物理链接状态变化等关键步骤,为理解PCIE设备的低功耗模式提供深入洞察。

1526

1526

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?