完整uart发送与接收模块以后,为了便于测试我把发送模块连接在了一起进行测试,接收到的数据SRX_I是以16倍波特率的方式即(CLK_1)传入uart_rx,我用16倍的频率CLK_16进行采样,然后每8位data输出到到uart_tx,然后通过tuart_tx把data中的数据依次输出即STX_O,但是我们STX_O的输出是以CLK_16为时钟的这样只是为了便于简单,不用再考虑这两个module(uart_tx,uart_rx)之间不同时钟信号的同步化。在我们分开用的时候,我们的输出STX_O应该是以CLK_1

为时钟周期。

注:其实本人已经做了两个module(uart_tx,uart_rx)之间不同信号的同步化,但发觉如果这样,会增加很多代码,还有很多同步化后信号延迟的问题,所以没有给出STX_O以CLK_1的时钟形式输出,有兴趣的同学可以给我留言,我可以给出相关同步化的代码。

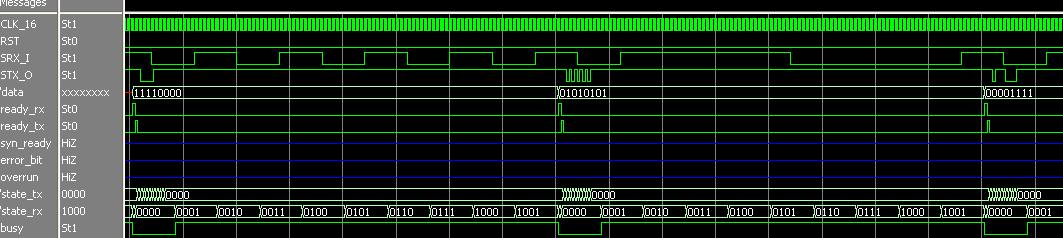

仿真波形如下:

模块代码如下:

1

module uart_top(CLK_16, RST, SRX_I, STX_O);

module uart_top(CLK_16, RST, SRX_I, STX_O);2

input CLK_16;

input CLK_16;3

input RST;

input RST;4

input SRX_I;

input SRX_I;5

output STX_O;

output STX_O;6

7

wire [7:0] data;

wire [7:0] data;8

wire ready_rx;

wire ready_rx;9

wire ready_tx;

wire ready_tx;10

wire syn_ready;

wire syn_ready;11

wire error_bit;

wire error_bit;12

wire overrun;

wire overrun;13

wire [3:0] state_tx;

wire [3:0] state_tx;14

wire [3:0] state_rx;

wire [3:0] state_rx;15

//u1,u3 is for the synchronization of the clk_16 and clk_1,which need a lot of code so I omit it.

//u1,u3 is for the synchronization of the clk_16 and clk_1,which need a lot of code so I omit it. 16

/**//* div_clk #(4,16)

/**//* div_clk #(4,16)17

u1(

u1(18

.clk(CLK_16),

.clk(CLK_16),19

.rst(RST),

.rst(RST),20

.o_clk(CLK_1)

.o_clk(CLK_1)21

);*/

);*/22

uart_rx u2(

uart_rx u2(23

.clk_16(CLK_16),

.clk_16(CLK_16),24

.rst(RST),

.rst(RST),25

.rxd(SRX_I),

.rxd(SRX_I),26

.dout(data),

.dout(data),27

.error_bit(error_bit),

.error_bit(error_bit),28

.overrun(overrun),

.overrun(overrun),29

.ready(ready_rx),

.ready(ready_rx),30

.busy(busy),

.busy(busy),31

.c_state(state_rx)

.c_state(state_rx)32

);

);33

/**//* syn_16to1 u3(

/**//* syn_16to1 u3(34

.clk_1(CLK_1),

.clk_1(CLK_1),35

.rst(RST),

.rst(RST),36

.asyn_data(ready_rx),

.asyn_data(ready_rx),37

.syn_data(syn_ready)

.syn_data(syn_ready)38

);*/

);*/39

uart_tx u4(

uart_tx u4(40

.din(data),

.din(data),41

.load(ready_rx),

.load(ready_rx),42

.clk(CLK_16),

.clk(CLK_16),43

.rst(RST),

.rst(RST),44

.txd(STX_O),

.txd(STX_O),45

.ready(ready_tx),

.ready(ready_tx),46

.c_state(state_tx)

.c_state(state_tx)47

);

);48

endmodule

endmodule49

testbench代码如下:

1

module uart_testbench;

module uart_testbench;2

parameter p=160;

parameter p=160;3

reg CLK_16;

reg CLK_16;4

reg RST;

reg RST;5

reg SRX_I;

reg SRX_I;6

wire STX_O;

wire STX_O;7

uart_top inst(

uart_top inst(8

.CLK_16(CLK_16),

.CLK_16(CLK_16),9

.RST(RST),

.RST(RST), 10

.SRX_I(SRX_I),

.SRX_I(SRX_I),11

.STX_O(STX_O)

.STX_O(STX_O)12

);

);13

initial

initial14

begin

begin15

16

RST=0;

RST=0;17

CLK_16=1;

CLK_16=1;18

SRX_I=1;

SRX_I=1;19

#1 RST=1;

#1 RST=1;20

#1 RST=0;

#1 RST=0;21

#p SRX_I=1;

#p SRX_I=1;22

#p SRX_I=1;

#p SRX_I=1;23

//1byte

//1byte24

#p SRX_I=0;

#p SRX_I=0;25

#p SRX_I=0;

#p SRX_I=0;26

#p SRX_I=0;

#p SRX_I=0;27

#p SRX_I=0;

#p SRX_I=0;28

#p SRX_I=0;

#p SRX_I=0;29

#p SRX_I=1;

#p SRX_I=1;30

#p SRX_I=1;

#p SRX_I=1;31

#p SRX_I=1;

#p SRX_I=1;32

#p SRX_I=1;

#p SRX_I=1;33

#p SRX_I=1;

#p SRX_I=1;34

//1byte

//1byte35

#p SRX_I=0;

#p SRX_I=0;36

#p SRX_I=1;

#p SRX_I=1;37

#p SRX_I=0;

#p SRX_I=0;38

#p SRX_I=1;

#p SRX_I=1;39

#p SRX_I=0;

#p SRX_I=0;40

#p SRX_I=1;

#p SRX_I=1;41

#p SRX_I=0;

#p SRX_I=0;42

#p SRX_I=1;

#p SRX_I=1;43

#p SRX_I=0;

#p SRX_I=0;44

#p SRX_I=1;

#p SRX_I=1;45

//1byte

//1byte46

#p SRX_I=0;

#p SRX_I=0;47

#p SRX_I=1;

#p SRX_I=1;48

#p SRX_I=1;

#p SRX_I=1;49

#p SRX_I=1;

#p SRX_I=1;50

#p SRX_I=1;

#p SRX_I=1;51

#p SRX_I=0;

#p SRX_I=0;52

#p SRX_I=0;

#p SRX_I=0;53

#p SRX_I=0;

#p SRX_I=0;54

#p SRX_I=0;

#p SRX_I=0;55

#p SRX_I=1;

#p SRX_I=1;56

//1byte

//1byte57

#p SRX_I=0;

#p SRX_I=0;58

#p SRX_I=1;

#p SRX_I=1;59

#p SRX_I=1;

#p SRX_I=1;60

#p SRX_I=0;

#p SRX_I=0;61

#p SRX_I=1;

#p SRX_I=1;62

#p SRX_I=1;

#p SRX_I=1;63

#p SRX_I=0;

#p SRX_I=0;64

#p SRX_I=1;

#p SRX_I=1;65

#p SRX_I=1;

#p SRX_I=1;66

#p SRX_I=1;

#p SRX_I=1;67

//1byte

//1byte68

#p SRX_I=0;

#p SRX_I=0;69

#p SRX_I=1;

#p SRX_I=1;70

#p SRX_I=1;

#p SRX_I=1;71

#p SRX_I=1;

#p SRX_I=1;72

#p SRX_I=1;

#p SRX_I=1;73

#p SRX_I=1;

#p SRX_I=1;74

#p SRX_I=1;

#p SRX_I=1;75

#p SRX_I=0;

#p SRX_I=0;76

#p SRX_I=1;

#p SRX_I=1;77

#p SRX_I=1;

#p SRX_I=1;78

#20000 $finish;

#20000 $finish; 79

end

end80

always #5 CLK_16=~CLK_16;

always #5 CLK_16=~CLK_16;81

endmodule

endmodule82

本文介绍了一个完整的UART发送与接收模块的设计过程,并详细说明了如何使用16倍波特率采样进行数据传输测试。文中提供了模块代码及测试bench实例。

本文介绍了一个完整的UART发送与接收模块的设计过程,并详细说明了如何使用16倍波特率采样进行数据传输测试。文中提供了模块代码及测试bench实例。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?