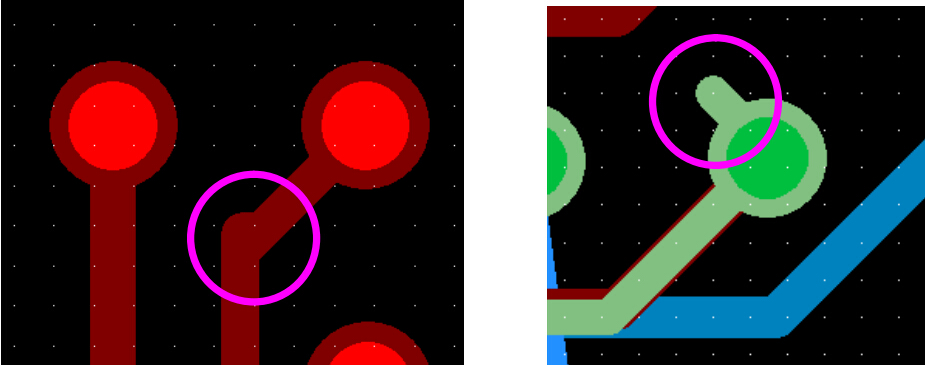

Stub线就是俗称的线头或歪线(特别在 Router中经常出现), 或者说信号没打算经过的路径,如图所示:

但是以下两种情况是可以忽略的:

1.在添加测试点的时候,为保证测试点的间距,不得不多拉一根线出来。

这种情况,对于High speed signal是完全禁止的。因为通过大量的仿真和布线经验,stub会严重影响高速线的信号质量。

信号对stub的长度也是有限制的,这就需要根据信号的速度而定。可通过仿真或直接咨询信号完整性工程师。

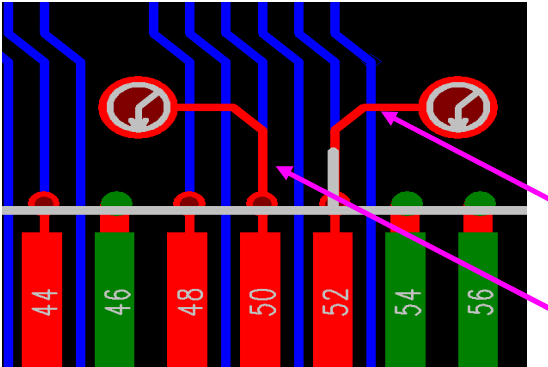

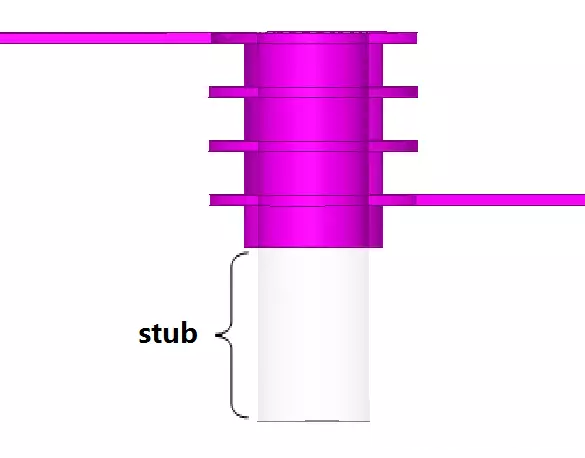

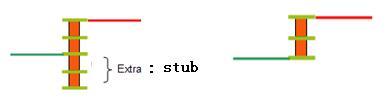

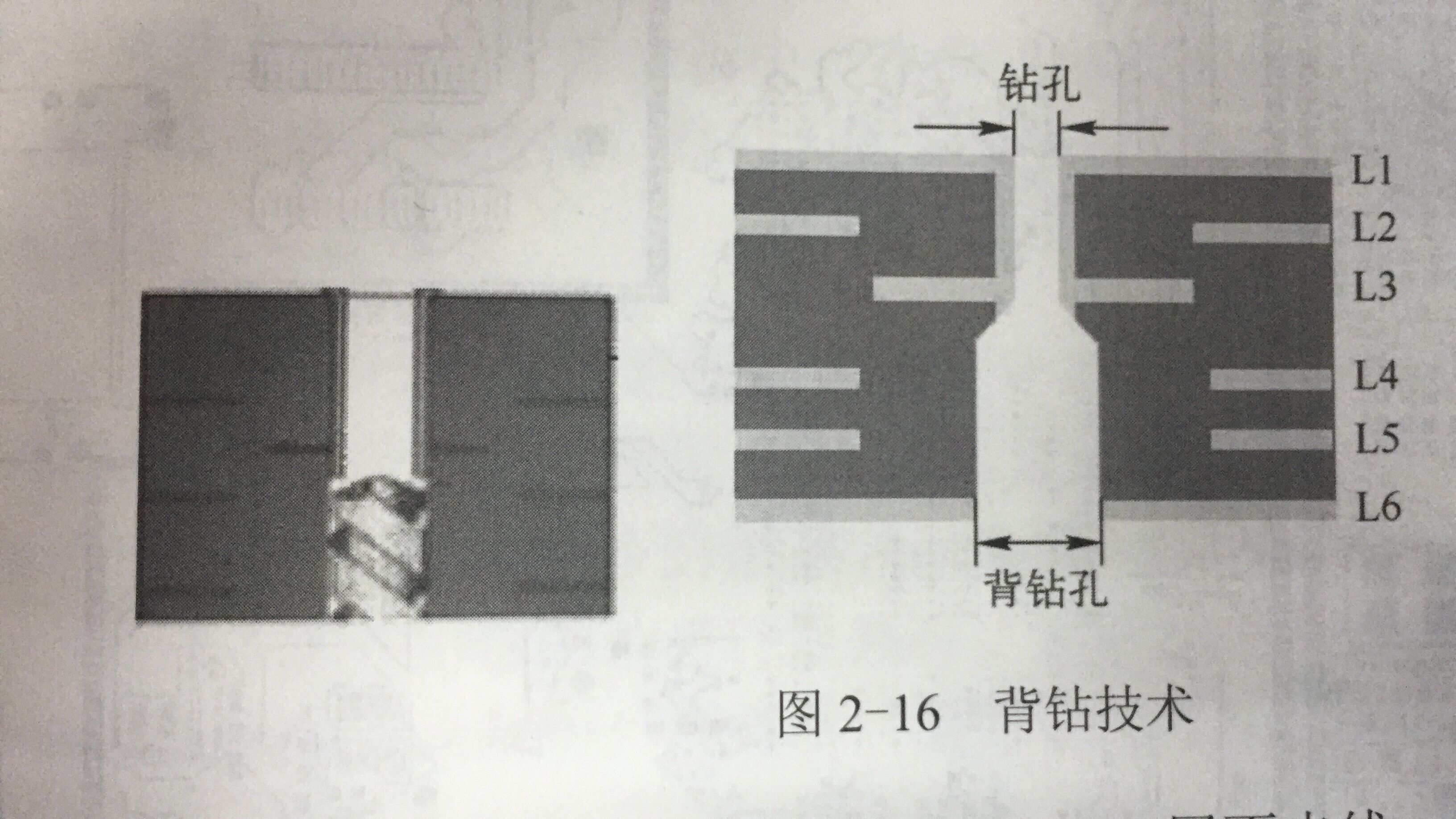

2.就是via stub对于press fit component而言的,当板厚在2.1mm以上时,并且信号是在上半部分层面进入press fit component ′s pin的时候,就产生了via stub。

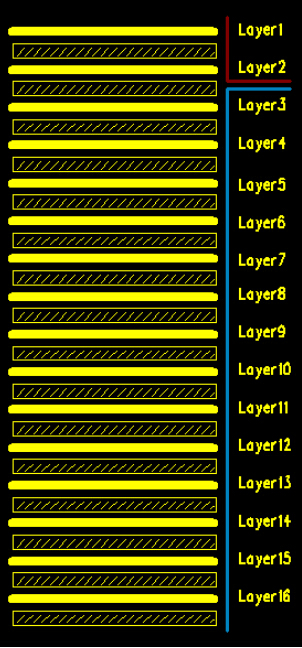

比如,一个16 层板,信号在 Layer3进入press fit component ′s pin,则红色路径为信号经过的路径。蓝色路径就是多出来的Stub。

此种情况一般3.125GHz以下是不需要考虑,但当频率高于3.125GHz时候,就一定要考虑via stub带来的影响,主要使用背钻技术(Back Drill)解决。

本博文部分参考:jimmy始发于EDA365高速PCB设计论坛的《PADS中如何检查Stub线》一文。

★独泽舟博客文章★ 原创文章转载请注明:http://www.cnblogs.com/duzezhou/

★独泽舟博客文章★ 原创文章转载请注明:http://www.cnblogs.com/duzezhou/

本文介绍了PCB设计中Stub线的概念及其对高速信号的影响。详细解释了两种特殊情况下的Stub线处理方式,包括添加测试点时的限制及Via Stub对Pressfit组件的影响。并提出了针对高频信号采用背钻技术解决问题的方法。

本文介绍了PCB设计中Stub线的概念及其对高速信号的影响。详细解释了两种特殊情况下的Stub线处理方式,包括添加测试点时的限制及Via Stub对Pressfit组件的影响。并提出了针对高频信号采用背钻技术解决问题的方法。

360

360

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?