一、简介

1、什么是内存屏障?

它是一个CPU指令。

2、为什么使用内存屏障?

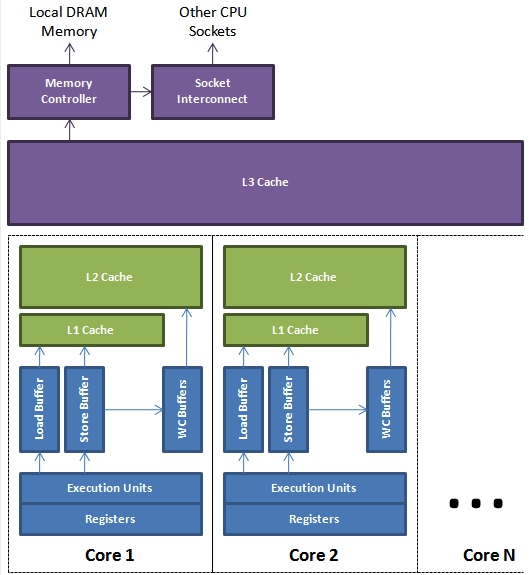

CPU硬件设计为了提高指令的运行速度,增设了两个缓冲区(store buffer, invalidate queue)。这个两个缓冲区能够避免CPU在某些情况下进行不必要的等待,从而提快速度,可是这两个缓冲区的存在也同一时候带来了新的问题。

编译器和CPU可以在保证输出结果一样的情况下对指令重排序,使性能得到优化。比如有的值在一个循环中,保存在寄存器中,没有被推倒cashe或者主内存中,这样其他进程根本看不到这个值。插入一个内存屏障,相当于告诉CPU和编译器先于这个命令的必须先执行,后于这个命令的必须后执行。

3、作用

a)确保一些特定操作执行的顺序; b)影响一些数据的可见性(可能是某些指令执行后的结果,强制更新一次不同CPU的缓存)。例如,一个写屏障会把这个屏障前写入的数据刷新到缓存,这样任何试图读取该数据的线程将得到最新值,而不用考虑到底是被哪个cpu核心或者哪颗CPU执行的。

我们在定义volatile变量时,写操作后插入一个写屏障指令,在读操作前插入一个读屏障指令。

4、对性能的影响

内存屏障作为另一个CPU级的指令,没有锁那样大的开销。内核并没有在多个线程间干涉和调度。但凡事都是有代价的。内存屏障的确是有开销的——编译器/cpu不能重排序指令,导致不可以尽可能地高效利用CPU,另外刷新缓存亦会有开销。所以不要以为用volatile代替锁操作就一点事都没。

本文深入探讨了内存屏障的概念,解释了其在多线程环境下防止指令重排序、确保数据一致性和可见性的重要作用。通过了解内存屏障如何影响CPU缓存和编译器行为,读者可以更好地掌握并发编程中的一致性问题。

本文深入探讨了内存屏障的概念,解释了其在多线程环境下防止指令重排序、确保数据一致性和可见性的重要作用。通过了解内存屏障如何影响CPU缓存和编译器行为,读者可以更好地掌握并发编程中的一致性问题。

6326

6326

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?