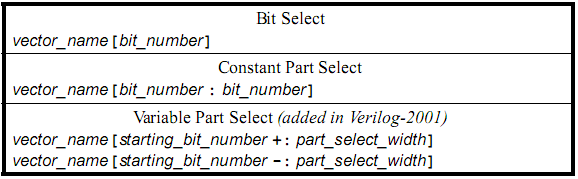

•A bit select can be an integer, a constant, a net, a variable or an expression.

•A constant part select is a group of bits from within the vector

•The part select must be contiguous bits.

•The bit numbers must be a literal number or a constant.

•The order of the part select must be consistent with the declaration of the vector (e.g. if the lsb is the the lowest bit number in the declaration, then the lsb of the part select must also be the lowest bit number).

•Variable part selects can vary the starting point of the part select, but the width of the part select must be a literal number, a constant or a call to a constant function. Variable part selects were added in Verilog-2001.

• + : indicates the part select increases from the starting point.

• - : indicates the part select decreases from the starting point.

Examples:

reg [31:0] big_vect;

reg [0:31] little_vect;

reg [63:0] dword;

integer sel;

The first four if statements show the identity between the two part select constructs.The last one shows an indexable nature.

initial begin

if ( big_vect[0 +:8] == big_vect[7 : 0] ) begin end

if ( little_vect[0 +:8] == little_vect[0 : 7] ) begin end

if ( big_vect[15 -:8] == big_vect[15 : 8] ) begin end

if ( little_vect[15 -:8] == little_vect[8 :15] ) begin end

if ( sel >0 && sel < 8) dword[8*sel +:8] = big_vect[7:0];

// Replace the byte selected.

本文详细介绍了 Verilog HDL 中的部分选择(part select)概念及其使用方法,包括常数部分选择、变量部分选择等,并通过具体实例展示了如何在代码中正确应用这些构造。

本文详细介绍了 Verilog HDL 中的部分选择(part select)概念及其使用方法,包括常数部分选择、变量部分选择等,并通过具体实例展示了如何在代码中正确应用这些构造。

1279

1279

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?