CPU Cache 之 直接映射缓存

直接映射缓存由若干缓存块(Cache Block,或Cache Line)构成

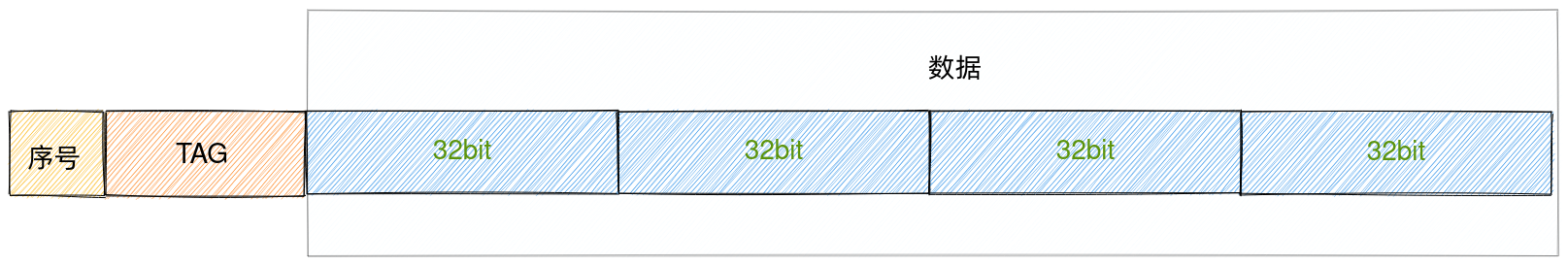

单个缓存块结构

这里假设一个缓存块的大小为

16字节

每个缓存块还会有有效位(valid bit)、脏位(dirty bit)、使用位(use bit)等,序号和TAG所占的位数和整个Cache大小,以及处理器的内存寻址方式。

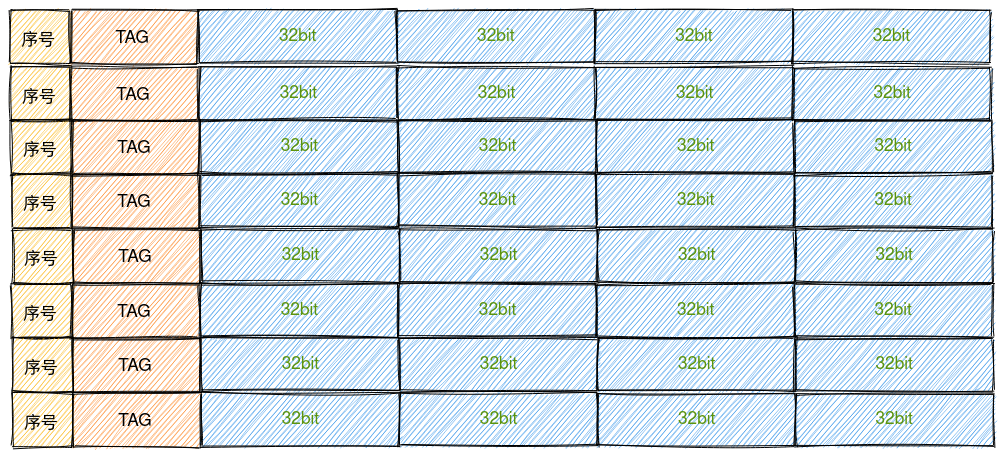

缓存结构

假设整个缓存的大小为

128字节,单个缓存块的大小为16字节

由于有8个缓存块,所以序号需要至少有3bit的空间

检查缓存是否命中

图片来自[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-cMtkjnnQ-1610702505423)(https://bk.tw.lvfukeji.com/baike-CPU%E7%BC%93%E5%AD%98)]

可以看出序号其实就是地址的低位,TAG是地址的高位。判断缓存是否命中就是先用低位地址定位到缓存块,然后再判断高位地址和TAG是否一致。

直接映射的各种计算

注:i5-6500采用的是

组相联映射模式,这里采用直接映射方式计算各种数据

- 查看

CPU L1 Cache大小

$ cat /sys/devices/system/cpu/cpu0/cache/index0/size

32K

可以看出我的i5-6500的L1大小为32K

- 查看

缓存块大小

# 这里我进入了/sys/devices/system/cpu/cpu0/cache/index0/

$ cat coherency_line_size

64

这里可以计算出有 :注:6500其实是组相联合的映射方式,这里只是为了展示计算过程

$ 2^5 * 2^{10}/ 2^6 = 2^9 $ 个缓存块

所以,如果使用直接映射的话,序号位置需要占用9bit

本文介绍了直接映射缓存的基本结构和工作原理,包括缓存块的组成(有效位、脏位、使用位)以及如何通过地址低位和TAG进行命中检查。通过实例展示了如何计算缓存块数量和序号所需位数,例如对于32K大小的L1缓存和64字节缓存块,序号需要9位。此外,内容还涉及到实际CPU(如i5-6500)的缓存配置和计算过程。

本文介绍了直接映射缓存的基本结构和工作原理,包括缓存块的组成(有效位、脏位、使用位)以及如何通过地址低位和TAG进行命中检查。通过实例展示了如何计算缓存块数量和序号所需位数,例如对于32K大小的L1缓存和64字节缓存块,序号需要9位。此外,内容还涉及到实际CPU(如i5-6500)的缓存配置和计算过程。

237

237

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?