MESI缓存一致性协议

一、CPU高速缓存(Cache Memory)

1、CPU为何高速缓存

CPU在摩尔定律的指导下以每18个月翻一番的速度在发展,然而内存和硬盘的发展速度远远不及CPU。这就造成了高性能能的内存和硬盘价格及其昂贵。然而CPU的高度运算需要高速的数据。为了解决这个问题,CPU厂商在CPU中内置了少量的高速缓存以解决I\O速度和CPU运算速度之间的不匹配问题。

在CPU中访问设备时无论是存取数据或者是存取指令,都趋于一个聚集的一片连续的区域中,及时局部性原理。

- 时间局部性:如果一个时间正在被访问,那么近期它可能还会被再次访问,比如:循环、递归、方法调用等

- 空间局部性: 如果一个存储器的位置被应用,那么将来他附近的位置也可能会被应用,比如:顺兴执行的代码,连续创建的两个对象、数组

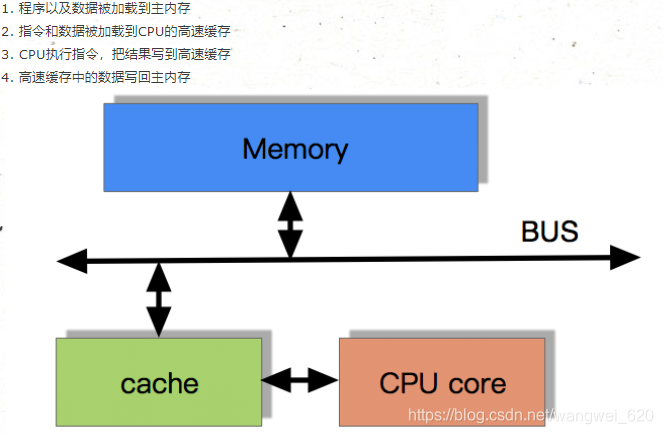

带高速缓存的CPU执行流程

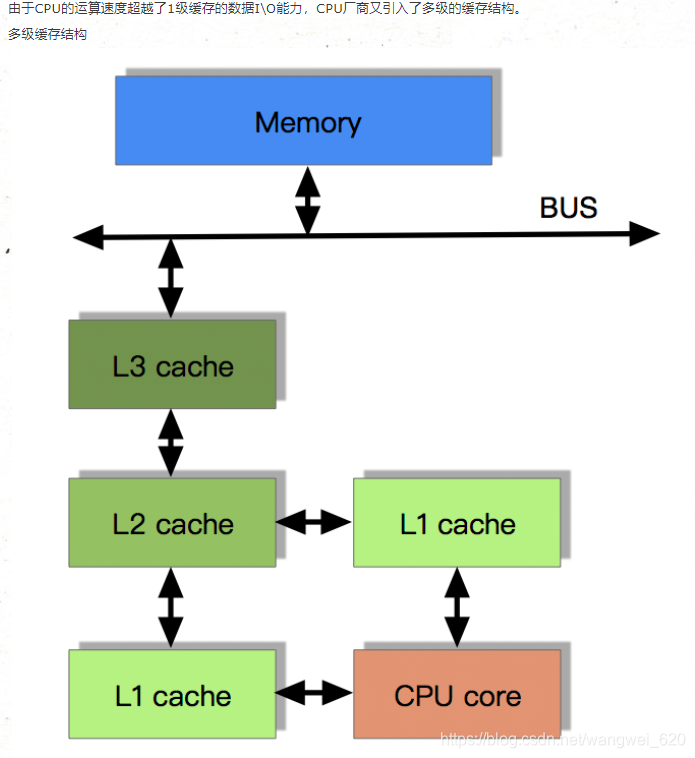

目前流行的多级缓存结构

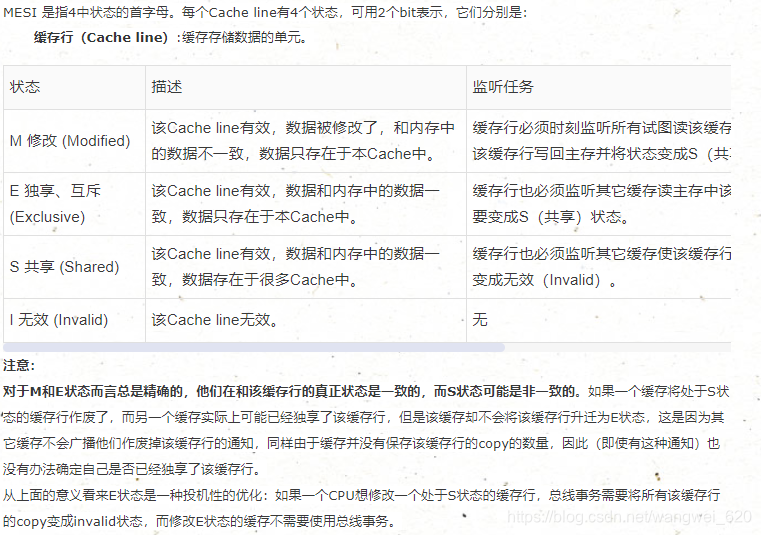

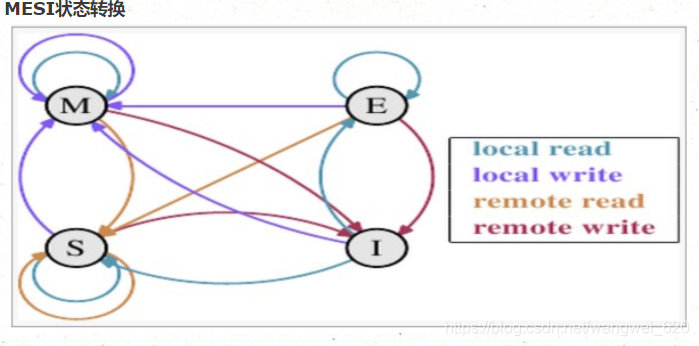

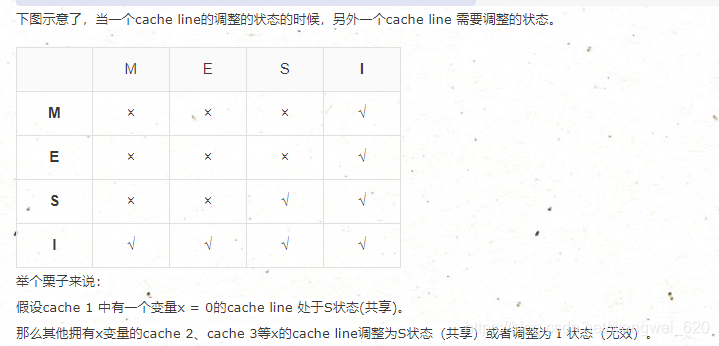

2、多核CPU缓存一致性协议MESI

多核CPU的情况xairui有多个一级缓存,如何保证内部的数据的不一致,不让系统数据混乱,这里就引出了一个一致性协议MESI

缓存行为分享

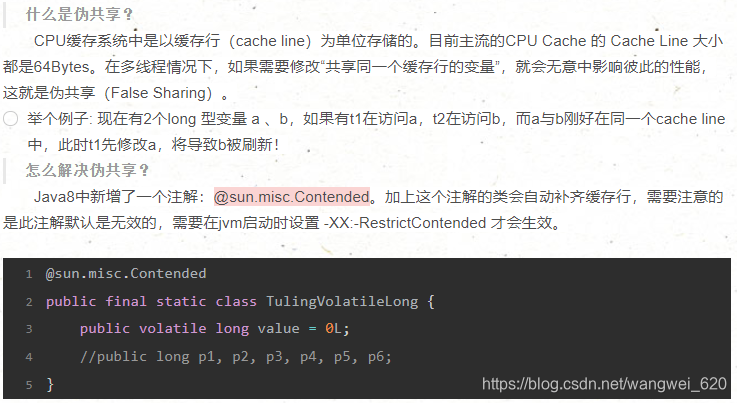

3、MESI引入的问题

缓存的一致性消息传递是要时间的,这就使其切换时会产生延迟。当一个缓存被切换状态时其他缓存收到消息完成各自的切换并且发出回应消息这么一长串的时间中CPU都会等待所有缓存响应完成。可能出现的阻塞都会导致各种各样的性能问题和稳定性问题。

1、CPU切换状态阻塞解决-存储缓存(Store - Bufferes)

比如你需要修改本地缓存中的一条信息,那么你必须将I(无效)状态通知到其他拥有该缓存数据的CPU缓存中,并且等待确认。等待确认的过程会阻塞处理器,这会降低处理器的性能。应为这个等待远远比一个指令的执行时间长的多。

Store BUfferes:

为了避免这种CPU运算能力的浪费,Store Bufferes被引入使用。处理器把它想要写入到主存的值写到缓存,然后继续去处理其他事情。当所有失效确认(Invalidate Acknowledge)都接收到时,数据才会最终被提交。

这么做有两个风险

Store bufferes 的风险

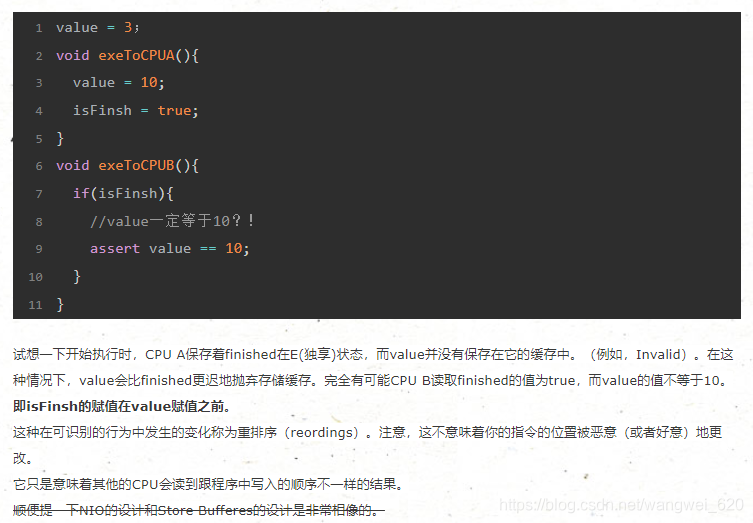

第一、就是处理器会尝试从存储缓存(Store buffer)中读取值,但它还没有进行提交。这个的解决方案称为Store Forwarding,它使得加载的时候,如果存储缓存中存在,则进行返回。

第二、保存什么时候会完成,这个并没有任何保证。

硬件内存模型

745

745

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?