背景:

ASPM--ACTIVE STATE POWER MANAGEMENT

ASPM是硬件自主的,软件无法控制且也无视其状态的变化,软件只能通过配置寄存器来使能或禁止ASMP。

PCI-PM--PCI Power Management

是PCIe设备之间通过功耗管理事件(Power Management Event,PME)来进行相互通信,并控制功耗状态的切换的协议。其要求PCIe设备的每个Function都包含PCI Power Management Capability寄存器。软件可以通过配置请求(Configuration Request)的方式来切换PCIe设备的某个Function的PM状态。

L1.2--Pcie规范还定义了L1低功耗子状态

L1是PCIe 链路的一种低功耗状态, L1.2是它的子状态也是目前功耗最低的状态,当在进入L1.2链路状态只保留CLKReq#信号,大部分模块处于掉电状态。

PCI-PM和ASPM都可以承载在L1.2之上。

NO SNOOP--一般情况下,内存数据是被CACHED的,但CACHE操作,费时有的时候,软件已知,某些内存是肯定不被CACHED的这样,就不需要SNOOP了。

注:这里的SNOOP,就是针对CACHE的操作

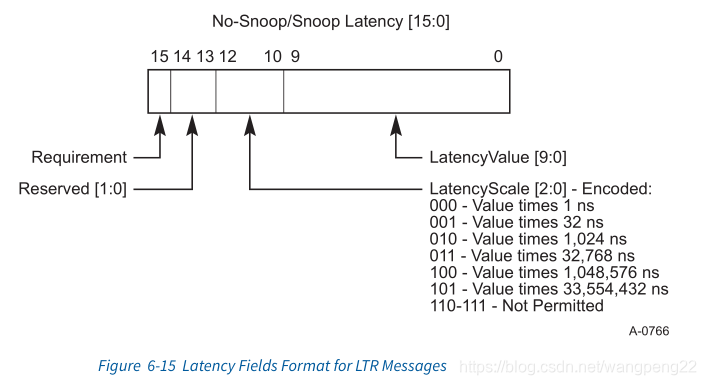

LTR--Latency Tolerance Reporting

The Latency Tolerance Reporting (LTR) mechanism enables Endpoints to report their service latency requirements for Memory Reads and Writes to the Root Complex, so that power management policies for central platform resources (such as main memory, RC internal interconnects, and snoop resources) can be implemented to consider Endpoint service requirements.

说人话就是控制端到端packet 延迟时间。(看起来似乎不太重要, 但是L1.2 必须要支持这个feature)

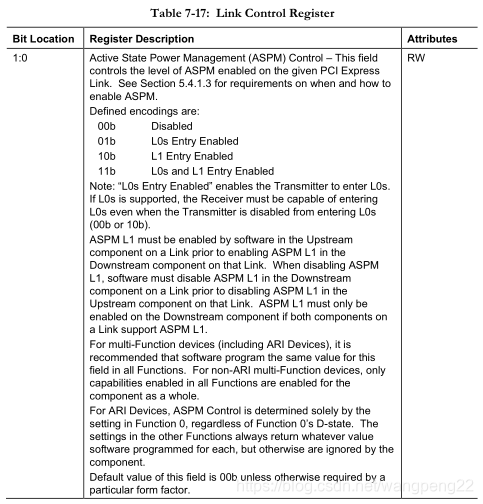

从协议分析L1.2--初始化配置

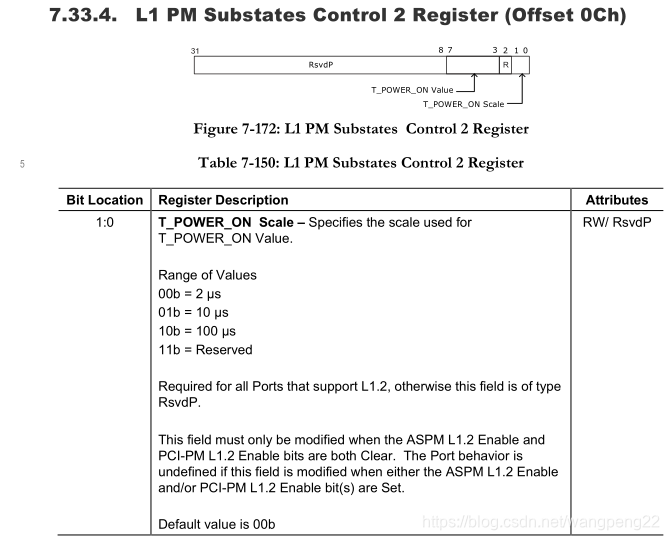

1. 配置T_Power_Value

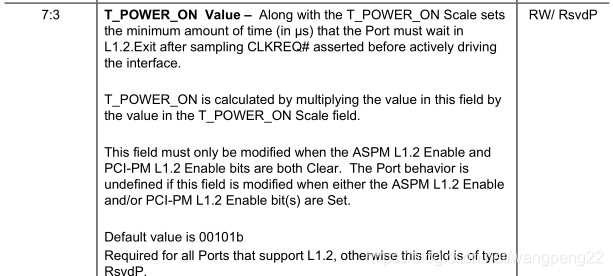

如图L1 PM substates control2 bit 1~0表示T_Power_On scale, bit 7~3表示T_Power_On value, 这里T_Power_On scale和T_Power_On value共同决定L1.2 <-> L1.0之间的时间。

如图,这里配置host配置为 0x31,即T_Power_On scale = 10us,T_Power_On value = 6,那么T_Power_on为600us。(Latency Value and Scale:这两个参数配合使用,可以将 Latency 配置为 1 纳秒 ~ 34 秒。如果将这两个值都设置为0,那就意味着任何延迟都会对设备产生影响,因此系统需要在第一时间响应该设备提出的请求)

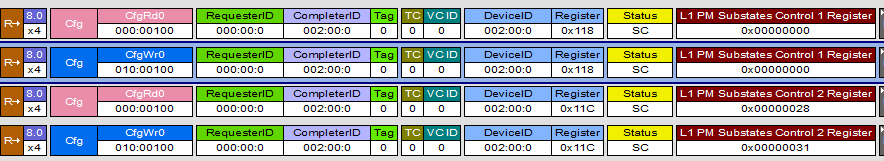

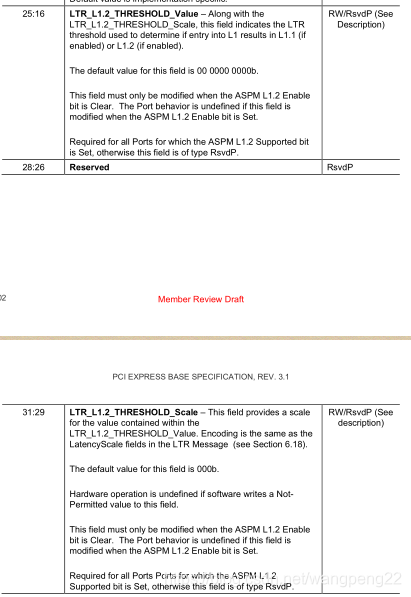

2. 配置PCI-PM / ASPM enable , 配置LTR threshold:

使用PCI-PM / ASPM 之前需要使能。如图:

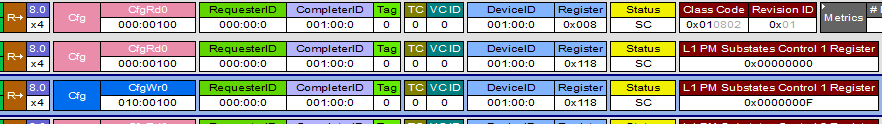

如图配置PCI-PM enable,ASPM enable。

如图配置LTR_L1.2_THRESHOLD_Value = 0xA0, LTR_L1.2_THRESHOLD_Scale = 2,这里LTR_L1.2_THRESHOLD_Value 和LTR_L1.2_THRESHOLD_Scale共同决定LTR threshold时间。

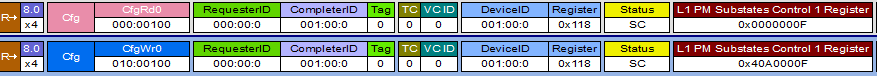

3. 配置Link Control

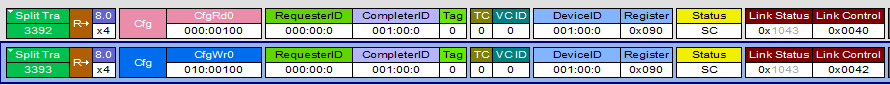

如图控制Link Control bit 1~0, set L1 entry enable。

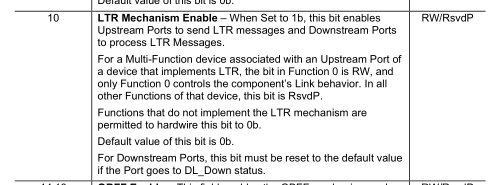

4. LTR enable

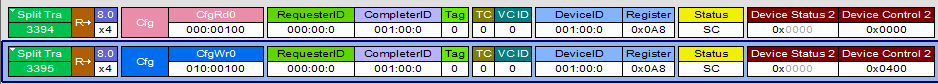

如图控制device Control2 bit 10, enable LTR。

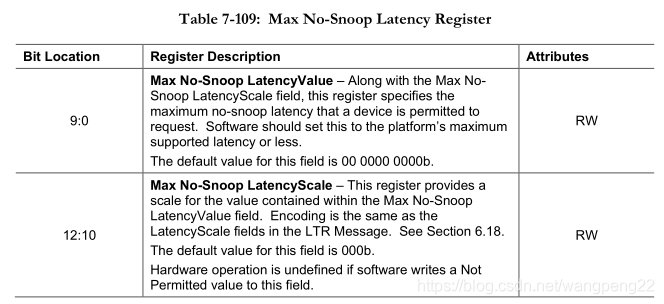

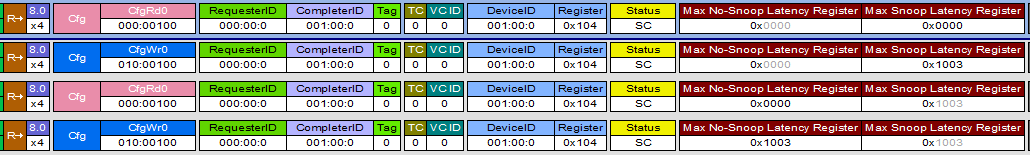

5. LTR latency

如图设置No-snoop Latency register / snoop Latency register 为0x1003.

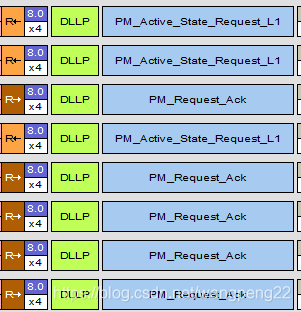

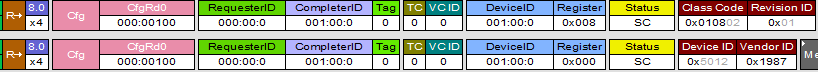

6. PM Active req

如图,device发起PM request L1.2, host 回复ACK, PM握手成功。一般PCIe End point在这个阶段会处理好内部的IO,当内部Idle发起这个请求,并对大部门模块掉电,只保留CLKReq#可以唤醒的Hardware模块。

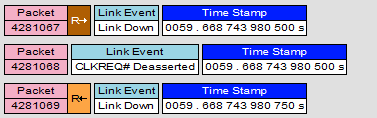

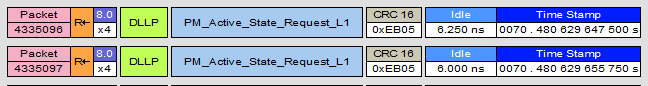

7. CLKReq# 拉高

CLKReq#拉高是L1.2 进入的最后一步,之后的该信号保持。

8. CLKReq#拉低

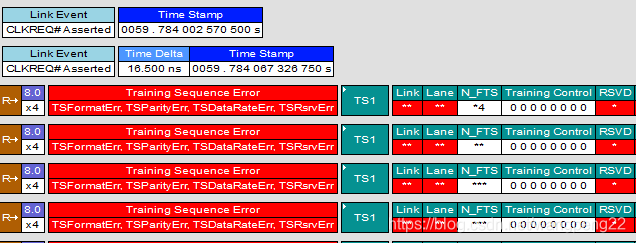

表示L1.2 退出请求, 该信号是host唤醒device的第一步,之后的该信号保持, 之后开始Link trianing。

9. 进入L0

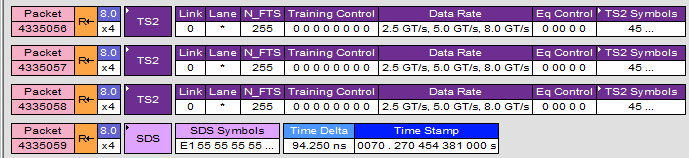

link training完成,进入L0, 并设置start data order set。

10. 收到报文

如图,可以看到唤醒device的是两条Config Read Packet。

11. PM L1 Request

再处理完报文之后,如果没有新的TLP / DLLP, ASIC会再次进入L1.2.

ASPM是一种Hardware主动进入的power management的协议,以上11步是ASPM整个流程,6~11步在PCIe ASPM L1.2 整个过程的循环执行。

PCI-PM / ASPM博大进深,本文仅介绍ASPM L1.2的协议流程,该协议可以适用于大部分PCIe EP, 比如PCIe 显卡, PCIe 网卡,PCIe存储设备(NVMe SSD)等。

本文详细介绍了PCI Express(PCIe)的ASPM(ACTIVE STATE POWER MANAGEMENT)中L1.2低功耗状态的配置和工作流程,包括T_Power_On配置、PCI-PM/ASPM启用、LTR阈值设定、Link Control和LTR Latency等关键步骤。内容适用于PCIe显卡、网卡和存储设备等。

本文详细介绍了PCI Express(PCIe)的ASPM(ACTIVE STATE POWER MANAGEMENT)中L1.2低功耗状态的配置和工作流程,包括T_Power_On配置、PCI-PM/ASPM启用、LTR阈值设定、Link Control和LTR Latency等关键步骤。内容适用于PCIe显卡、网卡和存储设备等。

145

145

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?