计算机组成原理学习笔记(一)

绪论

冯诺依曼计算机特点

- 计算机有五个部件组成,包括运算器ALU、控制器CU、存储器、输入设备、输出设备

- 指令和数据以同等地位存储于存储器中,可按地址访问

- 指令和数据以二进制表示

- 指令由操作码和地址码组成

- 核心特征是存储程序

- 以运算器为中心,输入输出设备必须经过运算器

缺点:运算繁忙,框图结构混乱

系统复杂性管理方法

- 层次化(Hierday):设计的系统分为多个模块

- 模块化(Modularity):有明确的功能和接口

- 规则性(regularity):模块更容易被重用

CPU组成

- CU控制器

| 名称 | 功能 |

|---|---|

| 指令寄存器(IR) | 存放当前欲执行的指令 |

| 计数器(PC) | 存放当前欲执行的指令的地址 |

- ALU算术逻辑运算器

| 名称 | 功能 |

|---|---|

| 累加器(ACC) | 存放被加数及和、被减数及差、乘积高位、被除数及余数 |

| 操作数寄存器(X) | 被乘数、除数、减数 |

| 乘商寄存器(MQ) | 乘数、乘积低位、商 |

- 存储寄存器

| 名称 | 功能 |

|---|---|

| 存储地址寄存器(MAR) | 存放从内存中读写数据的地址 |

| 存储数据寄存器(MDR) | 存放从内存中读写的数据 |

取数运行过程

- 将程序通过输入设备送至计算机

- 程序首地址送至PC,启动程序运行

- 取指令

- 分析指令

- 执行指令

- 完成取数

冯诺依曼结构和哈佛结构区别

- 冯诺依曼结构:指令与数据同等地位存储于内存中,仅有一条数据总线和地址总线

- 哈佛结构:指令和数据存储于不同内存中,有指令专用的数据总线和地址总线,有数据专用的数据总线和地址总线

硬件指标

- 机器字长

寄存器位数 - 运算速度

| 指标 | |

|---|---|

| 主频 | |

| 核数 | |

| 吉普森法 | |

| CPI | 执行一条指令所需时钟周期数 |

| MIPS | 每秒执行百万条指令 |

| FLOPS | 每秒浮点数运算次数 |

- 存储容量

字节数

总线

总线是各个部件的信息传输线,是各个部件共享的传输介质

总线分类

片内总线:芯片内部的总线

系统总线:计算机各部件的信息传输线,包括数据总线、地址总线、控制总线

- 数据总线:双向,与机器字长、存储字长有关

- 地址总线:单向,与存储地址、I/O地址有关

- 控制总线:有出有入(存储器读、存储器写、总线允许、中断确认、中断请求、总线请求)

通信总线:用于计算机系统之间过计算机系统与其他系统(如控制仪表、移动通信等)之间的通信,按照传输方式可分为串行通信总线和并行通信总线

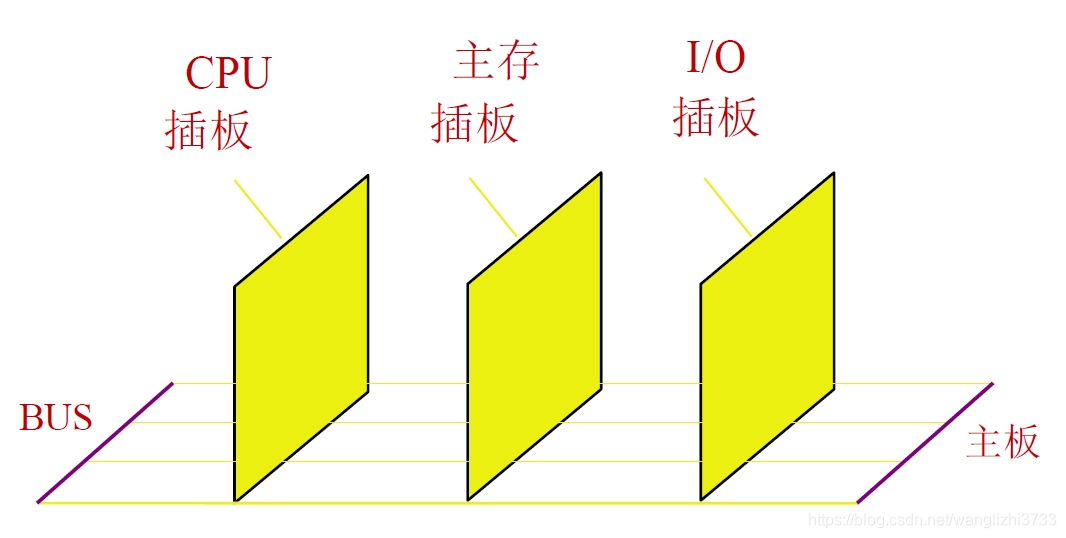

总线物理实现

总线性能指标

- 总线宽度:数据线宽度

- 标准传输率:每秒传输的最大字节数(MBps)

- 时钟同步/异步:同步、不同步

- 总线复用:地址线与数据线复用

- 信号线数:地址线、数据线和控制线综合

- 总线控制方式:负载能力

- 其他指标:突发、自动、仲裁、逻辑、计数

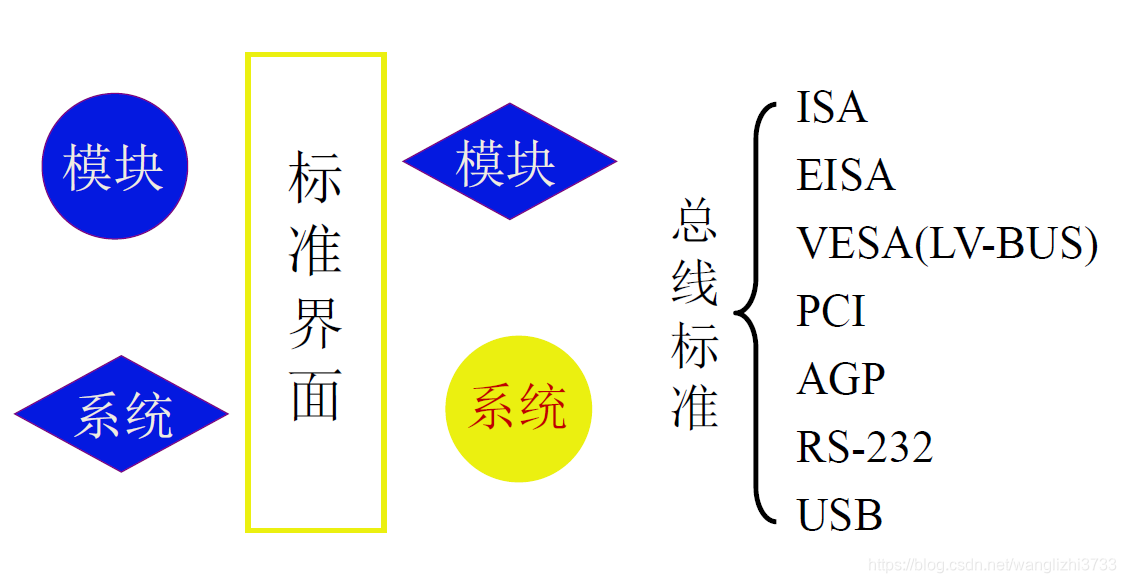

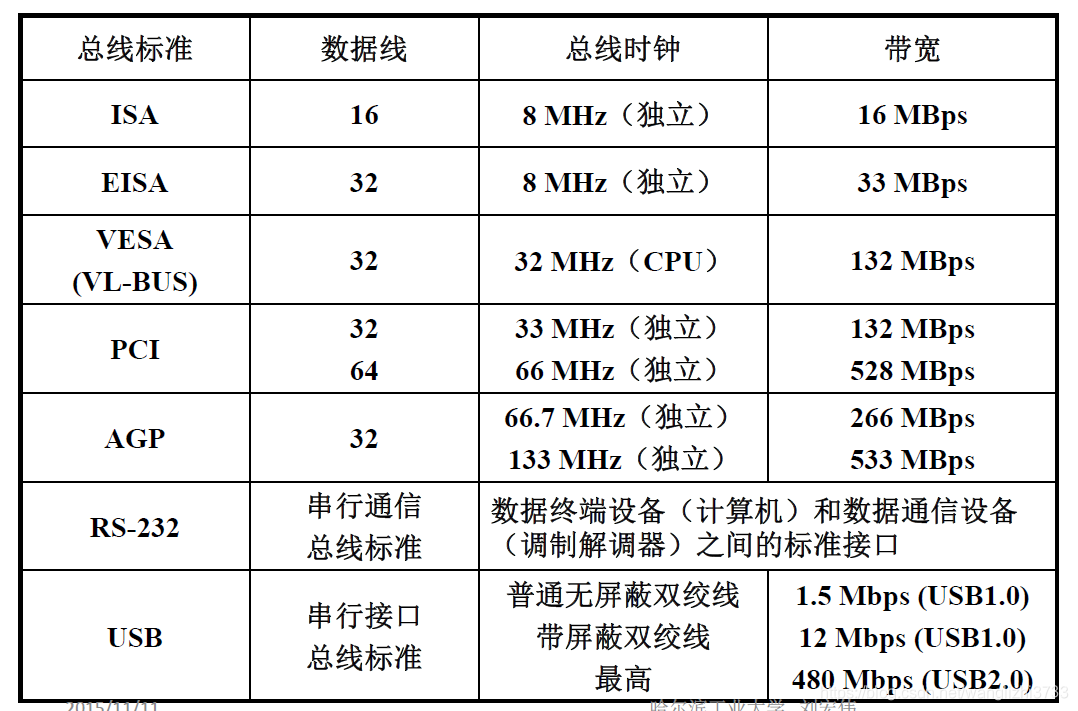

总线标准

总线结构

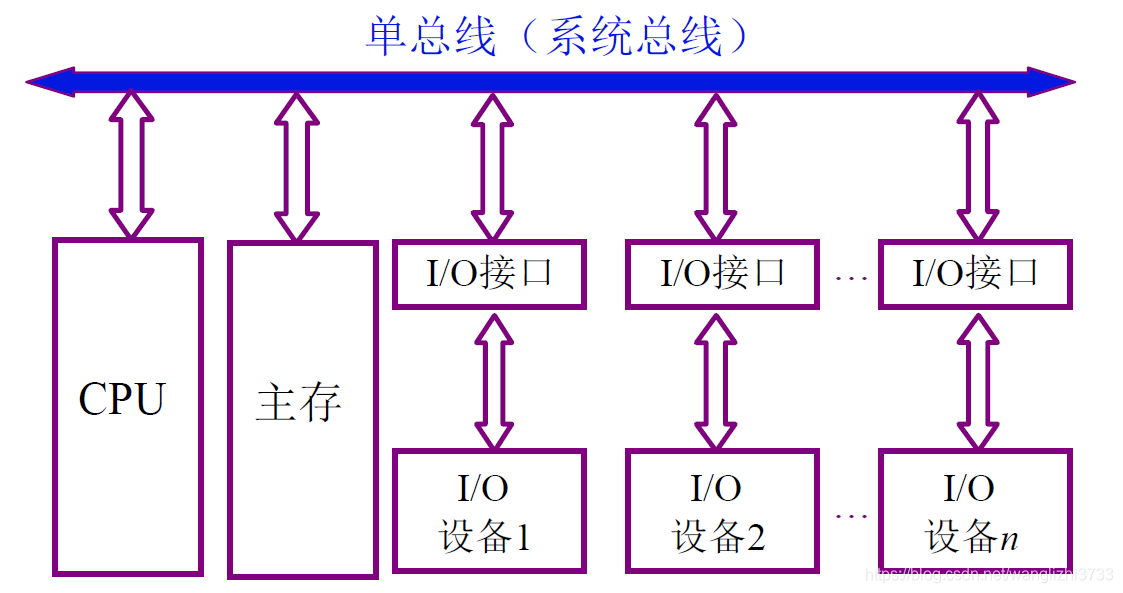

- 单总线结构

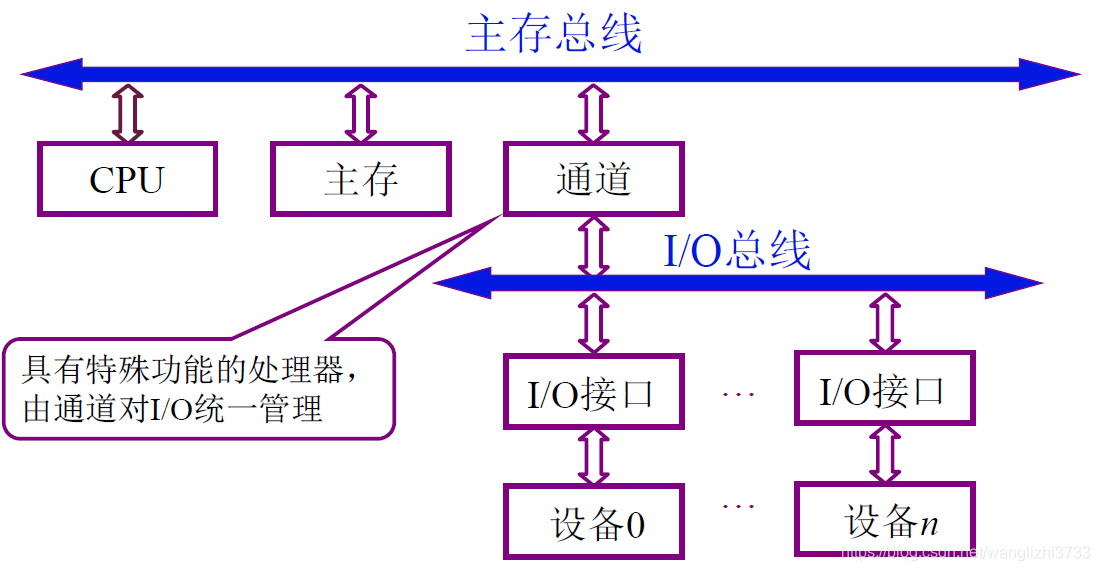

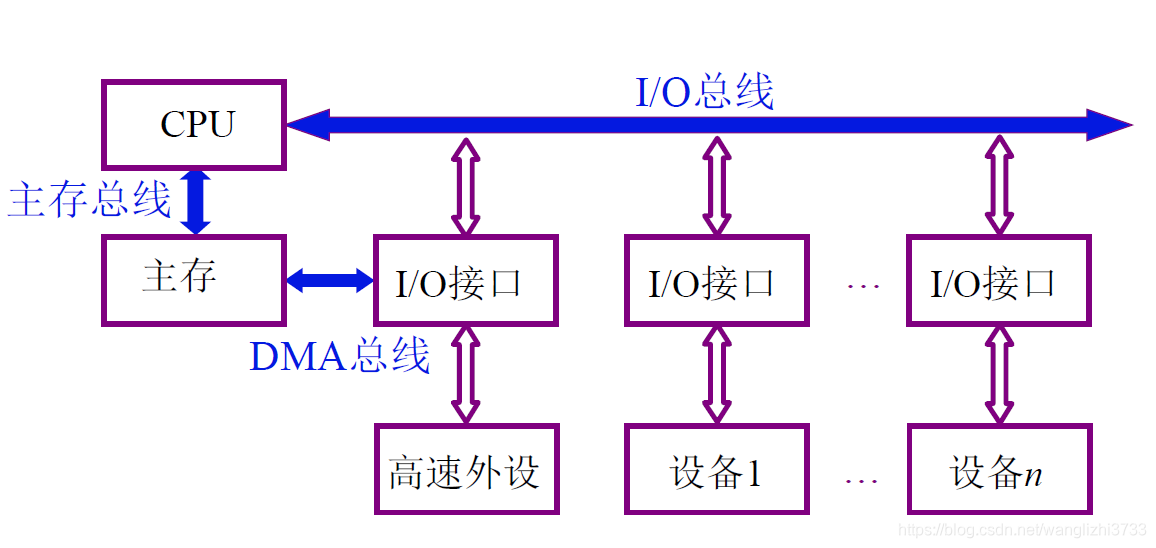

- 双总线结构

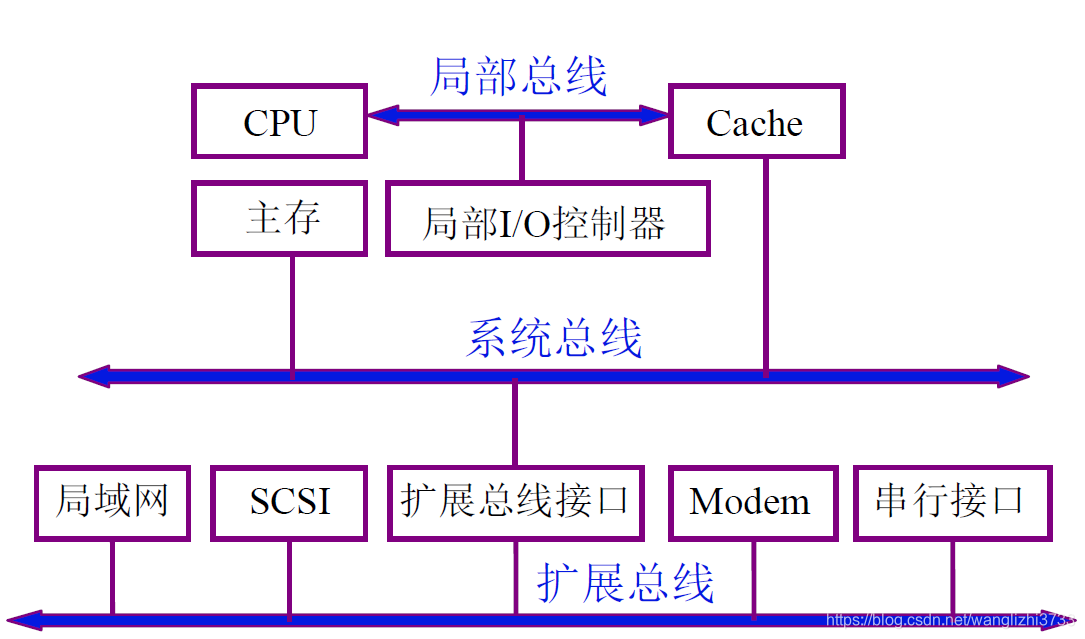

- 三总线结构I

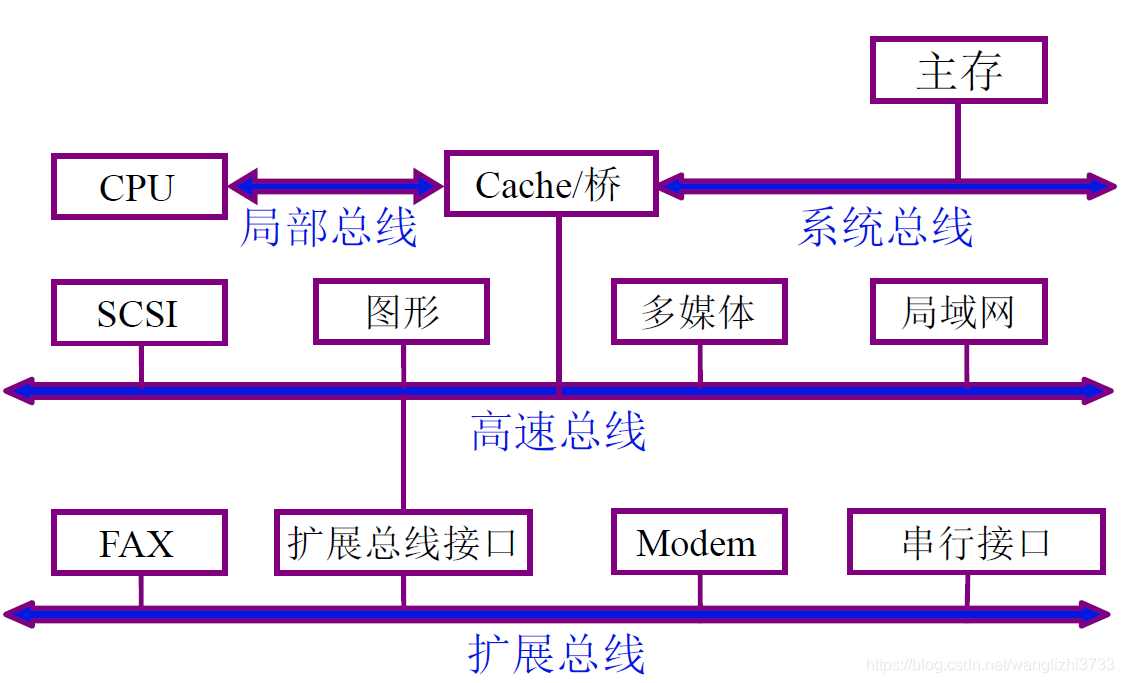

- 三总线结构II

- 四总线结构

总线判优控制

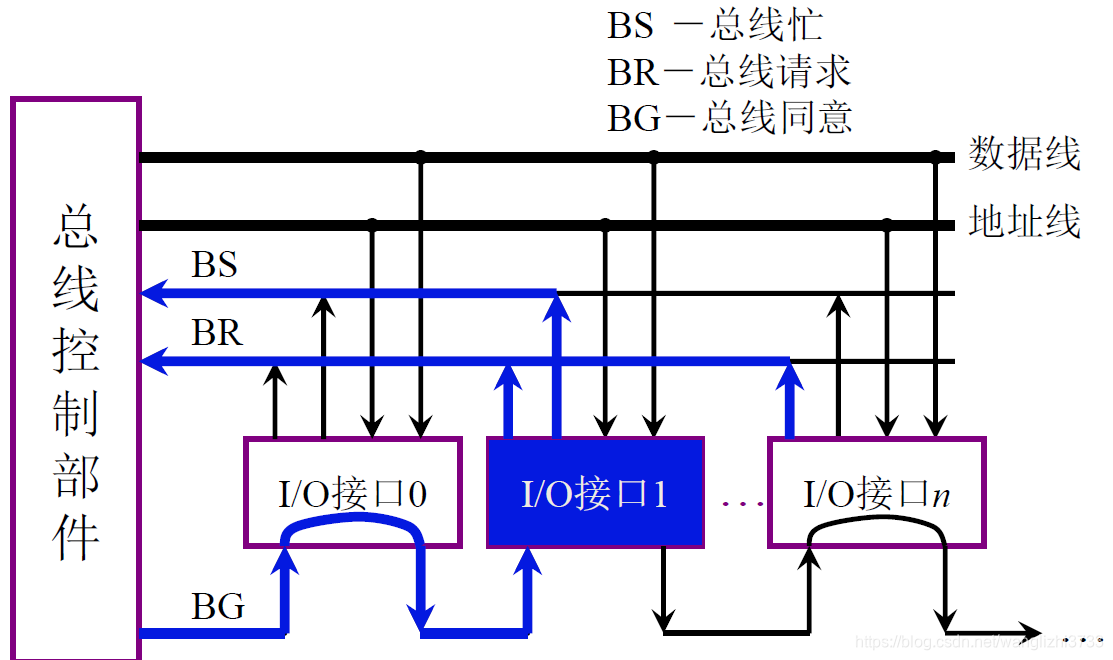

- 链式查询:仅有一条总线请求线,查询线串联,每次从IO1开始逐个查询,效率低,多用于微CPU

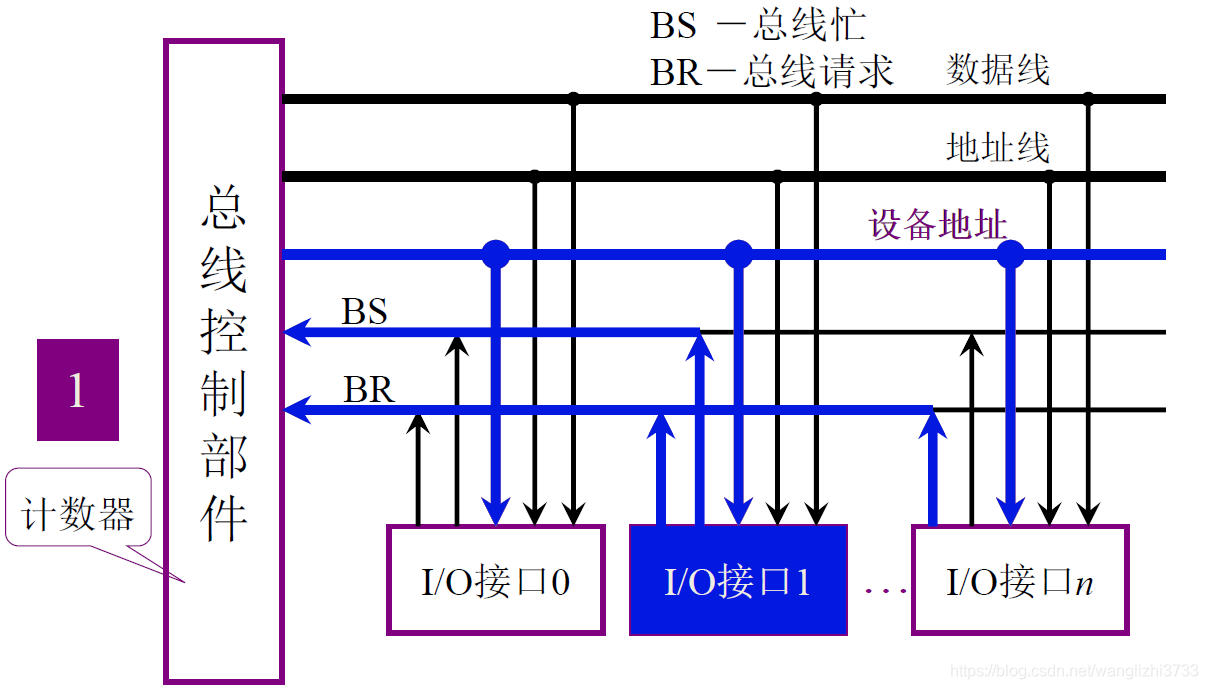

- 计数器定时查询:仅有一条地址线,但可以根据地址查询,方式灵活

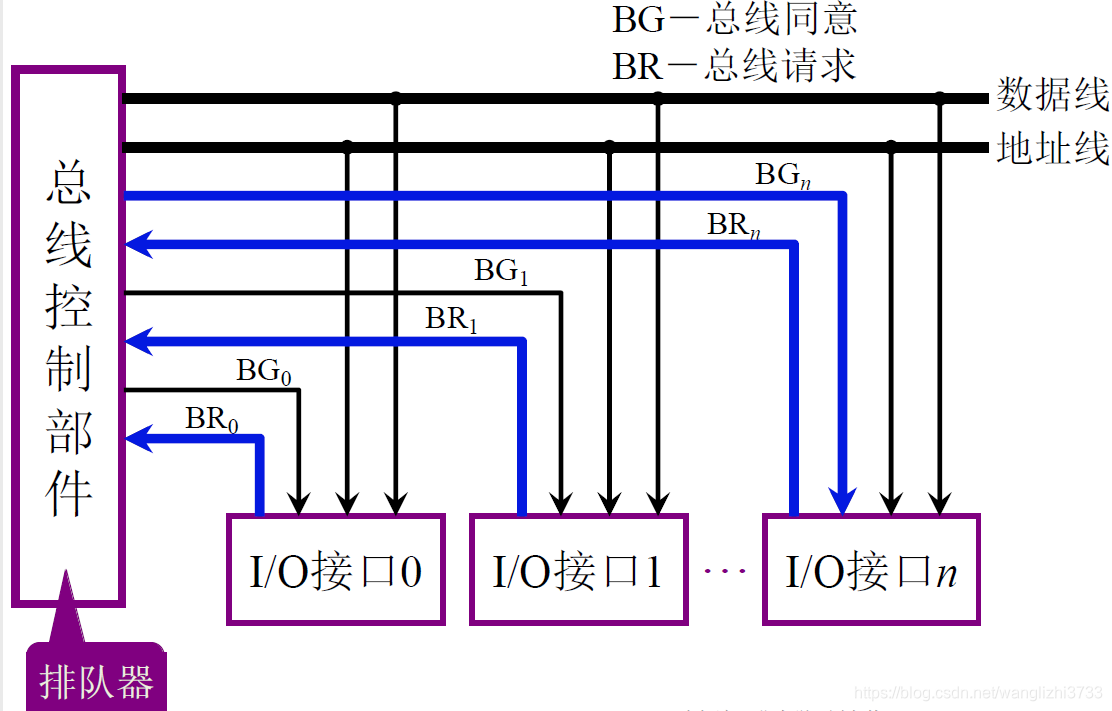

- 独立请求方式:有多根查询请求线,内部排队器判优

总线传输周期

- 申请分配阶段:主模块申请,总线仲裁决定

- 寻址阶段:主模块向从模块给出地址和命令

- 传数阶段:主模块和从模块交换数据

- 结束阶段:主模块撤销有关信息

总线通信

- 同步通信:由统一时标控制数据传送

- 异步通信:采用应答方式,没有公共时钟标准

- 半同步通信:同步、异步结合

- 分离式通信:充分挖掘系统总线每个瞬间的潜力

本文是关于计算机组成原理的学习笔记,详细介绍了冯诺依曼计算机的特点,包括其五大部分组成和存储程序核心特征。接着,探讨了系统复杂性管理方法,以及CPU的构成。内容涵盖取数运行过程、冯诺依曼结构与哈佛结构的区别,并深入讲解了总线的分类、物理实现、性能指标、标准和控制方式。

本文是关于计算机组成原理的学习笔记,详细介绍了冯诺依曼计算机的特点,包括其五大部分组成和存储程序核心特征。接着,探讨了系统复杂性管理方法,以及CPU的构成。内容涵盖取数运行过程、冯诺依曼结构与哈佛结构的区别,并深入讲解了总线的分类、物理实现、性能指标、标准和控制方式。

1382

1382

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?