输出250M时钟给AD9613,过FPGA ILA逻辑分析仪将AD9613采集的两个通道ADC数据250M数据显示出来。其中AD9613输出的是LVDS数据,通过select IO核转为并行数据。

一,搜索IP核:selectIO interface wizad ,并双击配置

配置为input,DDR模式,数据位宽为12bit,IO类型为差分,这里配置的是12对数据差分对。然后配置外部差分时钟。

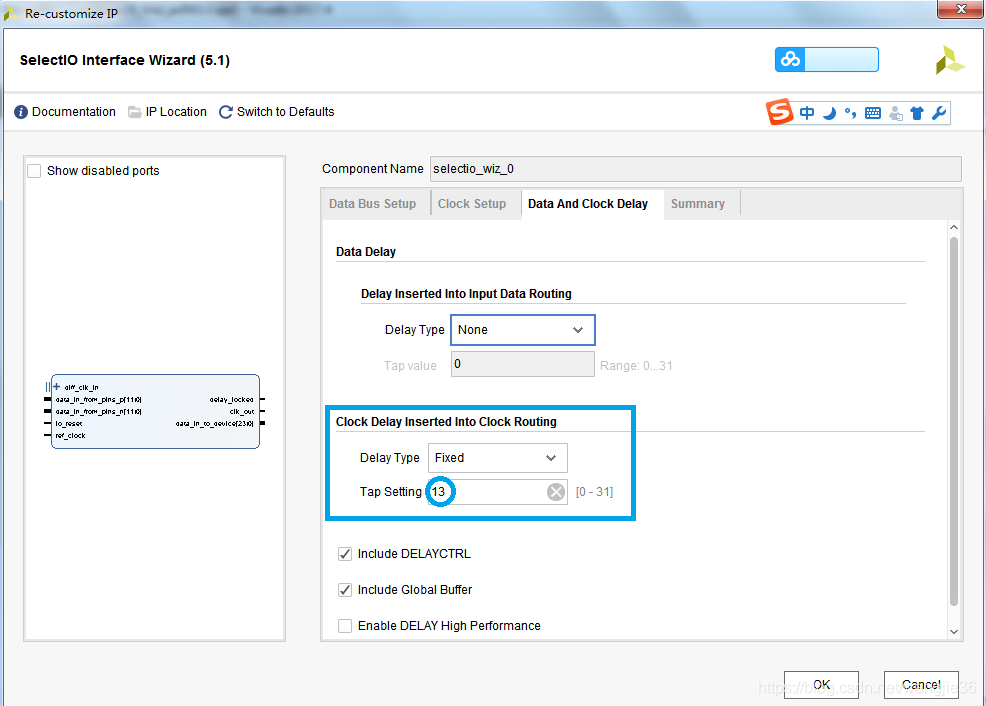

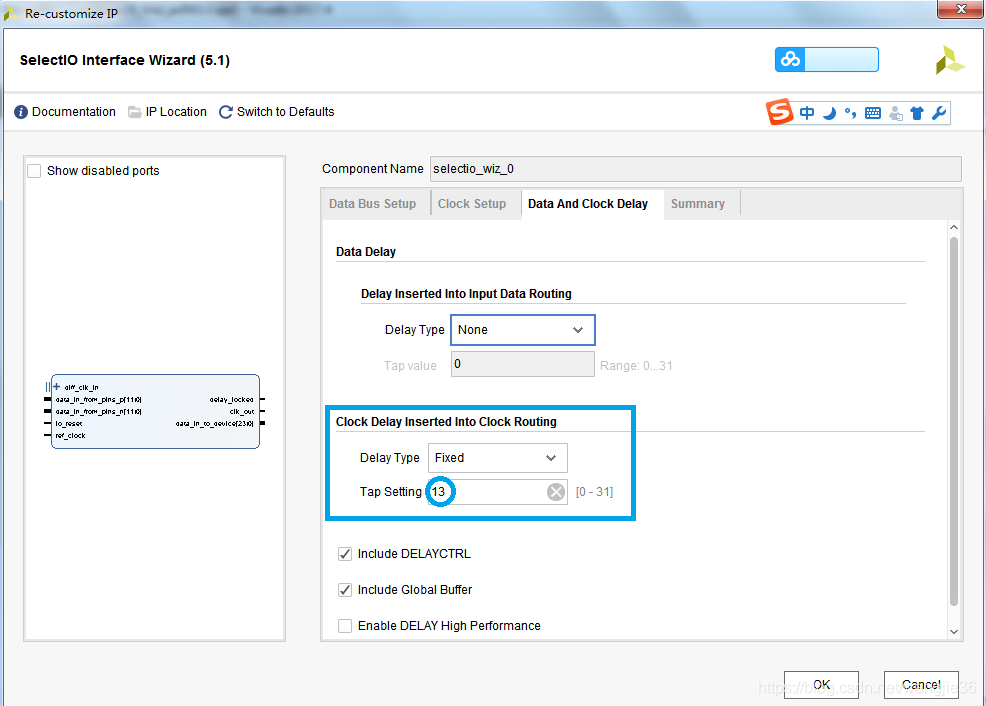

将tap setting 设置为13,将时钟的边沿对准数据的中间,以免数据出错

本文介绍了如何通过FPGA配置AD9613,输出250MHz时钟并利用ILA逻辑分析仪显示ADC数据。内容包括配置selectIO IP核为输入DDR模式,生成差分时钟,转换LVDS到并行数据,以及观察超量程信号。测试结果显示,数据成功在ILA中以有符号数形式展示。

本文介绍了如何通过FPGA配置AD9613,输出250MHz时钟并利用ILA逻辑分析仪显示ADC数据。内容包括配置selectIO IP核为输入DDR模式,生成差分时钟,转换LVDS到并行数据,以及观察超量程信号。测试结果显示,数据成功在ILA中以有符号数形式展示。

输出250M时钟给AD9613,过FPGA ILA逻辑分析仪将AD9613采集的两个通道ADC数据250M数据显示出来。其中AD9613输出的是LVDS数据,通过select IO核转为并行数据。

一,搜索IP核:selectIO interface wizad ,并双击配置

配置为input,DDR模式,数据位宽为12bit,IO类型为差分,这里配置的是12对数据差分对。然后配置外部差分时钟。

将tap setting 设置为13,将时钟的边沿对准数据的中间,以免数据出错

1万+

1万+

770

770