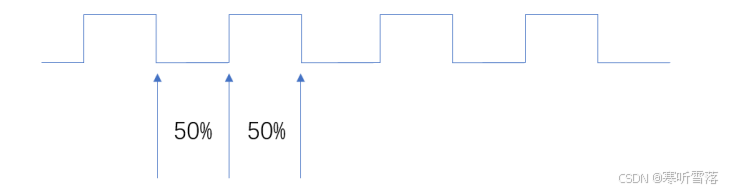

1,时钟

理想的时钟模型是一个占空比为50%且周期固定的方波。时钟是FPGA中逻辑运行的一个基准。

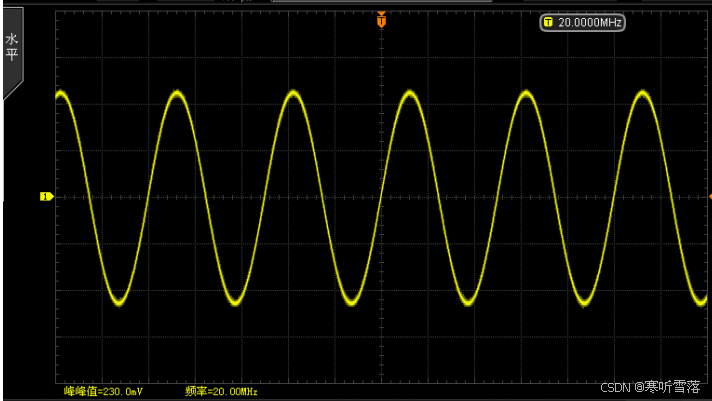

实际电路中输入给FPGA的晶振时钟信号其实是正弦波,这个波形不影响FPGA对时钟的识别。

2,时钟抖动

理想的时钟信号是非常完美的正弦波,但是实际晶振产生的正弦波是存在一些时钟抖动的。

时钟抖动(Clock Jitter)是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的

本文总结了复旦微FPGA开发过程中的各种问题,包括启动方式确认、PS软复位、DMA数据交互、中断配置、网络通信、程序加载异常等,并提供了相应的解决办法,如调整硬件配置、优化代码、更新烧录工具等。

本文总结了复旦微FPGA开发过程中的各种问题,包括启动方式确认、PS软复位、DMA数据交互、中断配置、网络通信、程序加载异常等,并提供了相应的解决办法,如调整硬件配置、优化代码、更新烧录工具等。

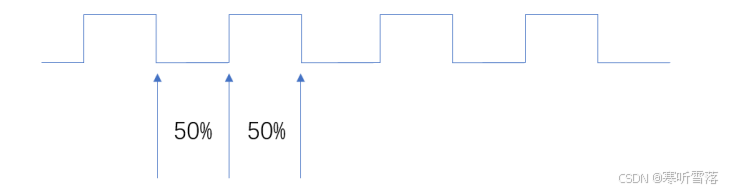

1,时钟

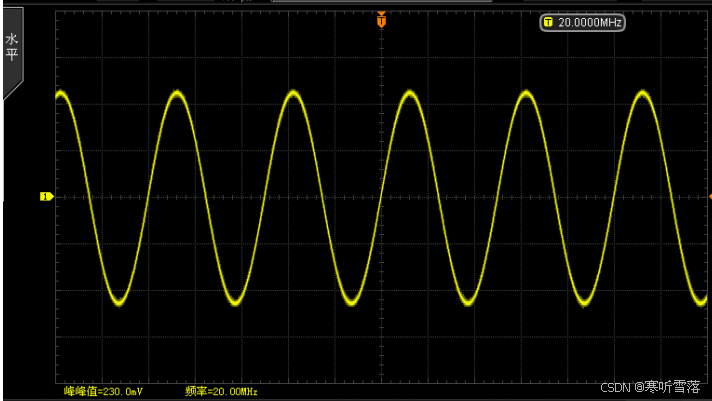

2,时钟抖动