文章目录

- Chapter 8 System Boot

- 8.1 Overview

- 8.2 引导模式

- 8.3 Device configuration

- 8.4 Device initialization

- 8.5 Boot devices (internal boot)

- 8.6 QuadSPI serial flash memory boot

- 8.7 Program image

- 8.8 Plugin image

- 8.9 Serial Downloader

- 8.10 Recovery devices

- 8.11 USB low-power boot

- 8.12 SD/MMC manufacture mode

- 总结

Chapter 8 System Boot

i.MX 6ULL Applications Processor Reference Manual, Rev. 1, 11/2017

8.1 Overview

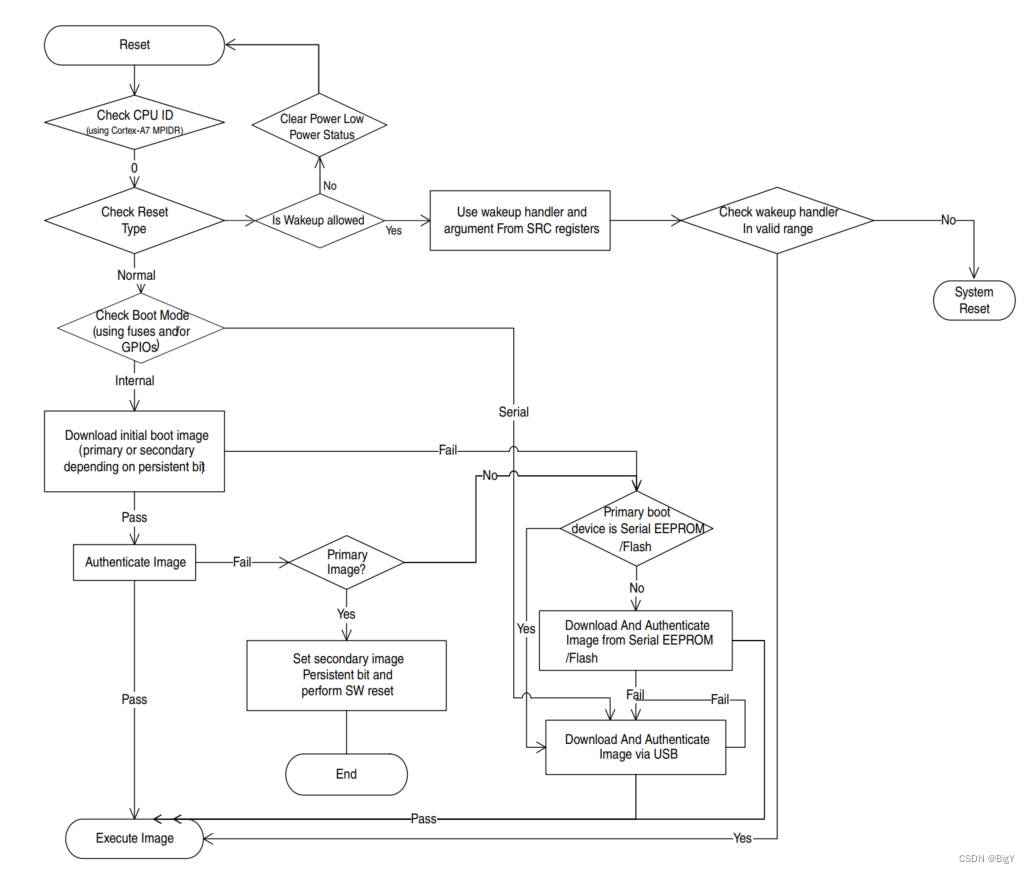

引导过程始于Power-On Reset (POR),其中硬件复位逻辑强制Arm核从片上启动ROM开始执行。引导ROM代码使用内部寄存器BOOT_MODE [1:0]的状态以及各种eFUSE和/或GPIO设置的状态来确定设备的引导流程行为。

ROM的主要功能包括:

- 支持从各种引导设备引导

- 串行下载器支持(USB OTG和UART)

- 设备配置数据(DCD)和插件

- 基于数字签名和加密的高保障引导(HAB)

- 从低功耗模式唤醒

引导ROM支持以下引导设备: - NOR Flash

- NAND Flash

- OneNAND Flash

- SD/MMC

- 串行(SPI)NOR Flash 和 EEPROM

- QuadSPI(QSPI) Flash

引导ROM使用BOOT_MODE和eFUSEs的状态来确定引导设备。为了开发方便,用于确定引导设备的eFUSE可以使用GPIO引脚输入进行覆盖。

引导ROM代码还允许下载要在设备上运行的程序。例如,一个配置程序可以通过串行连接进一步使用,以提供具有新镜像的引导设备。通常,配置程序会下载到内部RAM中,并允许对引导设备(如SD/MMC闪存)进行编程。ROM串行下载器使用高速USB以非流模式连接,UART以流模式连接。

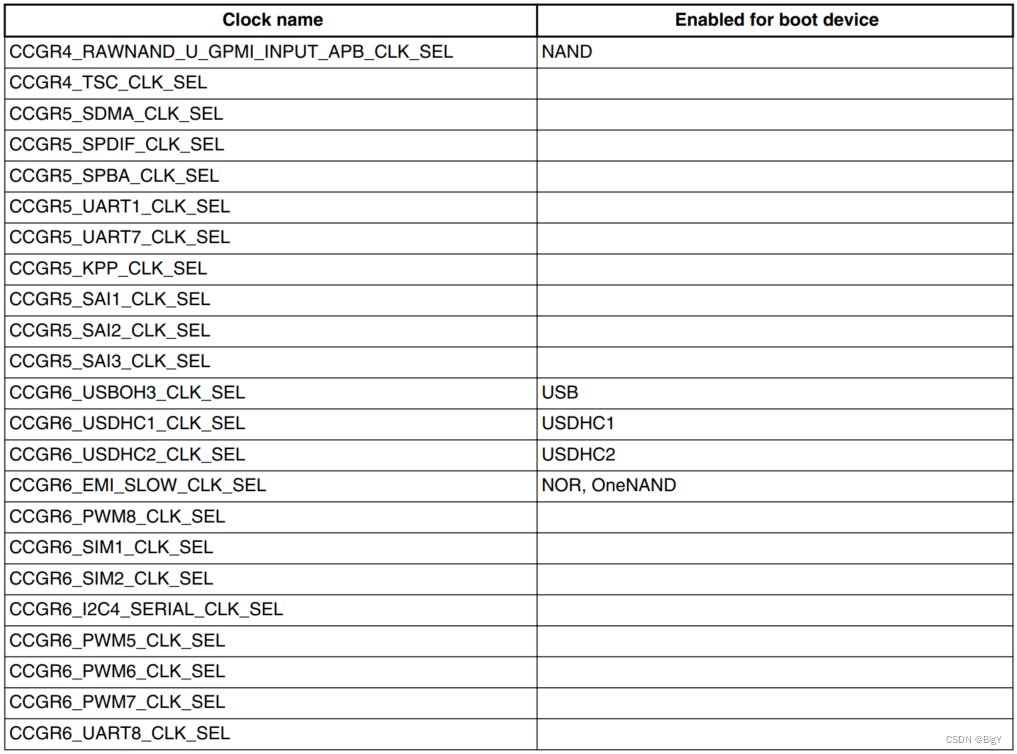

引导ROM允许从低功耗模式唤醒。复位时,ROM会检查电源门控状态寄存器。从低功耗模式唤醒时,核心会跳过从引导设备加载镜像的步骤,并跳转到PERSISTENT_ENTRY0中保存的地址。

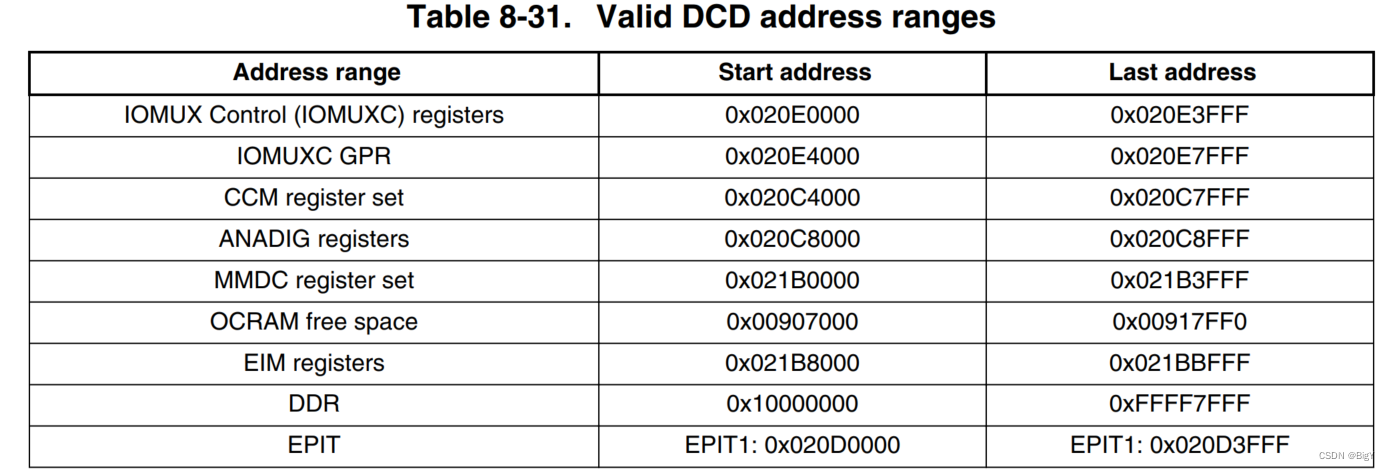

设备配置数据(DCD)功能允许引导ROM代码从存储在引导设备上的外部程序镜像中获取SOC配置数据。例如,DCD可以用于为DDR控制器设置最佳配置,提高引导性能。DCD仅限于被认为对引导目的至关重要的内存区域和外设地址(参见写数据命令)。

引导ROM的一个关键特性是能够执行安全引导,也称为高保证引导(HAB)。这一特性由HAB安全库支持,后者是ROM代码的一个子组件。HAB利用硬件和软件结合以及公钥基础设施(PKI)协议来保护系统免受未经授权的程序执行。在HAB允许用户镜像执行之前,镜像必须经过签名。签名过程是由私钥持有者在镜像构建过程中完成的,然后将签名作为最终程序镜像的一部分包含进去。如果配置为这样做,ROM将使用程序镜像中包含的公钥验证签名。除了支持数字签名验证以认证程序镜像外,还支持加密引导。加密引导可用于防止直接从引导设备克隆程序镜像。

在芯片支持的所有引导设备上(包括串行下载器),HAB都可以执行安全引导。引导ROM中的HAB库还提供API函数,允许额外的引导链组件(引导加载程序)扩展安全引导链。SEC_CONFIG的出厂设置是开放配置,在此配置下,ROM/HAB执行图像认证,但忽略所有认证错误并仍允许图像执行。

8.2 引导模式

在复位期间,芯片会检查电源门控制器状态寄存器。在引导过程中,核心的行为由引导模式引脚设置定义,如引导模式引脚设置所述。从低功耗引导模式唤醒时,核心跳过时钟设置。引导ROM会检查PERSISTENT_ENTRY0寄存器(参见持久化位)是否指向一个有效的地址空间(OCRAM、DDR、QSPI或EIM)。如果PERSISTENT_ENTRY0指向一个有效的范围,它将使用PERSISTENT_ENTRY0寄存器中的入口点开始执行。如果PERSISTENT_ENTRY0指向无效的范围,核心执行系统复位。

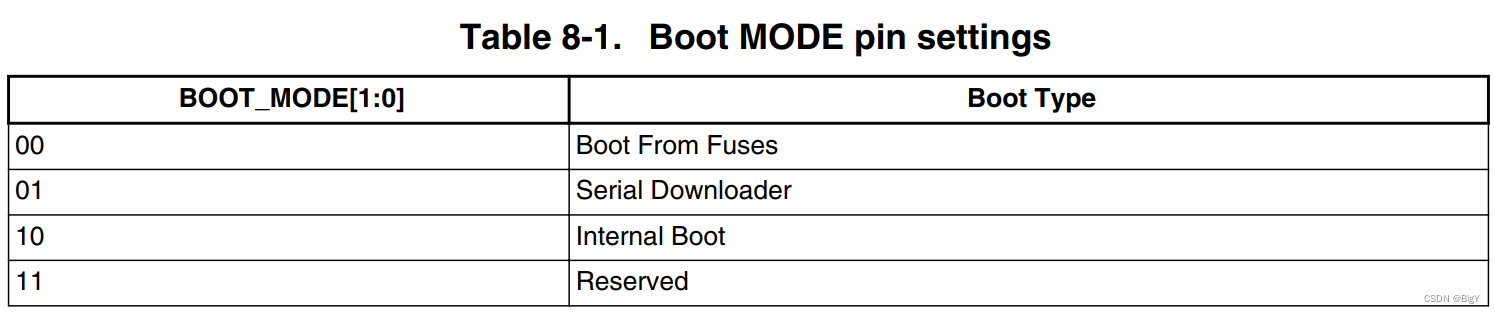

8.2.1 引导模式引脚设置

该设备有四种引导模式(其中一种为NXP保留)。引导模式是基于存储在内部BOOT_MODE寄存器中的二进制值进行选择的。

BOOT_MODE通过在POR_B上升沿采样BOOT_MODE0和BOOT_MODE1输入来初始化。采样这些输入后,它们后续的状态不会影响BOOT_MODE内部寄存器的内容。可以从SRC Boot Mode寄存器(SRC_SBMR2)的BMOD[1:0]字段读取内部BOOT_MODE寄存器的状态。可用的引导模式有:从熔丝引导、通过USB串行引导和内部引导。有关设置,请参见以下表格:

8.2.2 High-level boot sequence

在BOOT_MODE[1:0]寄存器中的00b值选择了"Boot From Fuses"模式。该模式类似于"内部引导"模式中描述的BOOT_MODE[1:0] = 0b10,但有一个区别。在这种模式下,GPIO引导覆盖引脚会被忽略。引导ROM代码仅使用引导eFUSE设置。该模式还支持使用HAB进行安全引导。

如果设置为"Boot From Fuses",则引导流程由BT_FUSE_SEL eFUSE值控制。如果BT_FUSE_SEL = 0,表示引导设备(例如闪存、SD/MMC)尚未编程,则引导流程直接跳转到串行下载器。如果BT_FUSE_SEL = 1,则按照正常的引导流程进行,ROM尝试从所选的引导设备引导。

在首次使用板子时,默认eFUSE可能对平台上的硬件配置不正确。在这种情况下,引导ROM代码可能尝试从一个不存在的设备引导,这可能导致某些引脚发生电气/逻辑违例。使用"Boot From Fuses"模式可以解决这个问题。

设置BT_FUSE_SEL=0会强制ROM代码直接跳转到串行下载器。这允许下载一个引导加载程序,然后可以用程序图像配置引导设备并烧写BT_FUSE_SEL和其他引导配置eFUSE。复位后,引导ROM代码确定BT_FUSE_SEL已经烧写(BT_FUSE_SEL = 1),然后根据新的eFUSE设置执行内部引导。这允许用户在生产设备上设置BOOT_MODE[1:0]=00b,并且在同一设备上烧写保险丝(通过强制进入串行下载器),而无需更改BOOT_MODE[1:0]的值或者BOOT_MODE引脚上的上拉/下拉电阻。

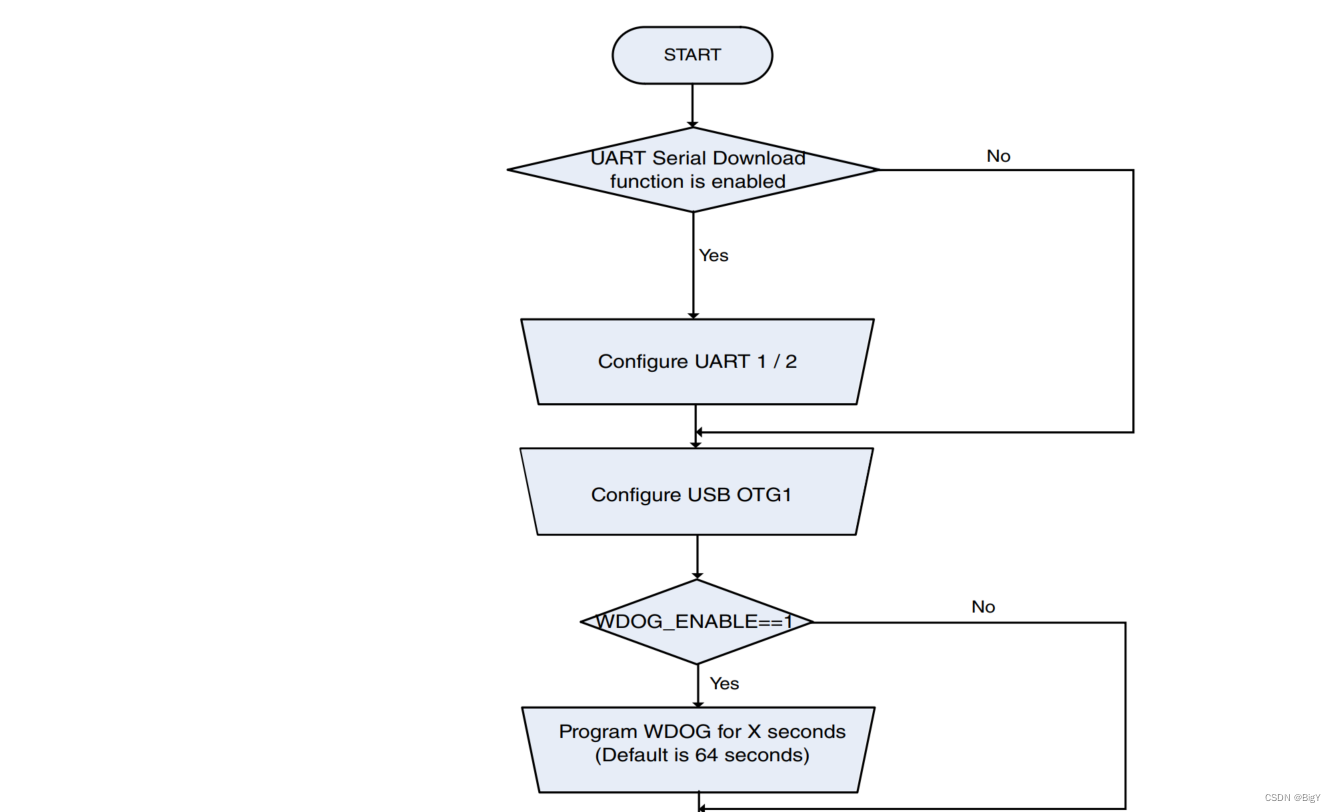

8.2.4 Serial Downloader

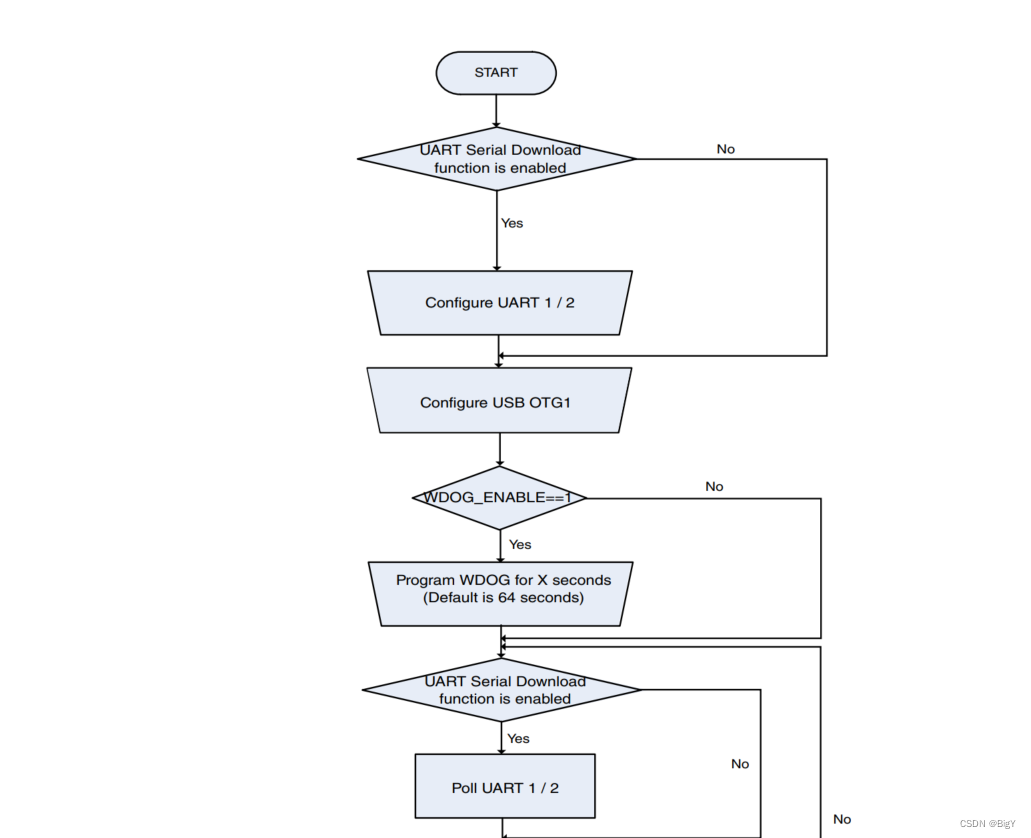

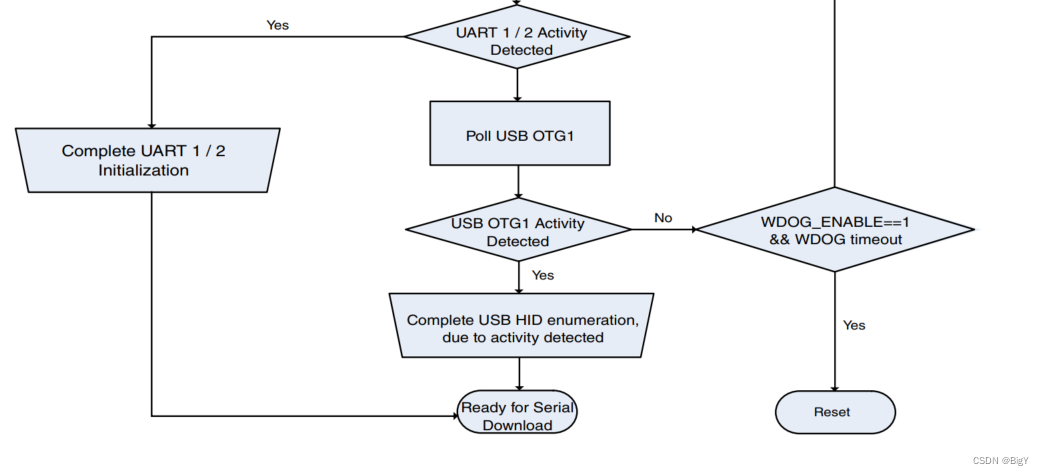

串行下载器提供了通过USB和UART串口连接将程序图像下载到芯片的方法。

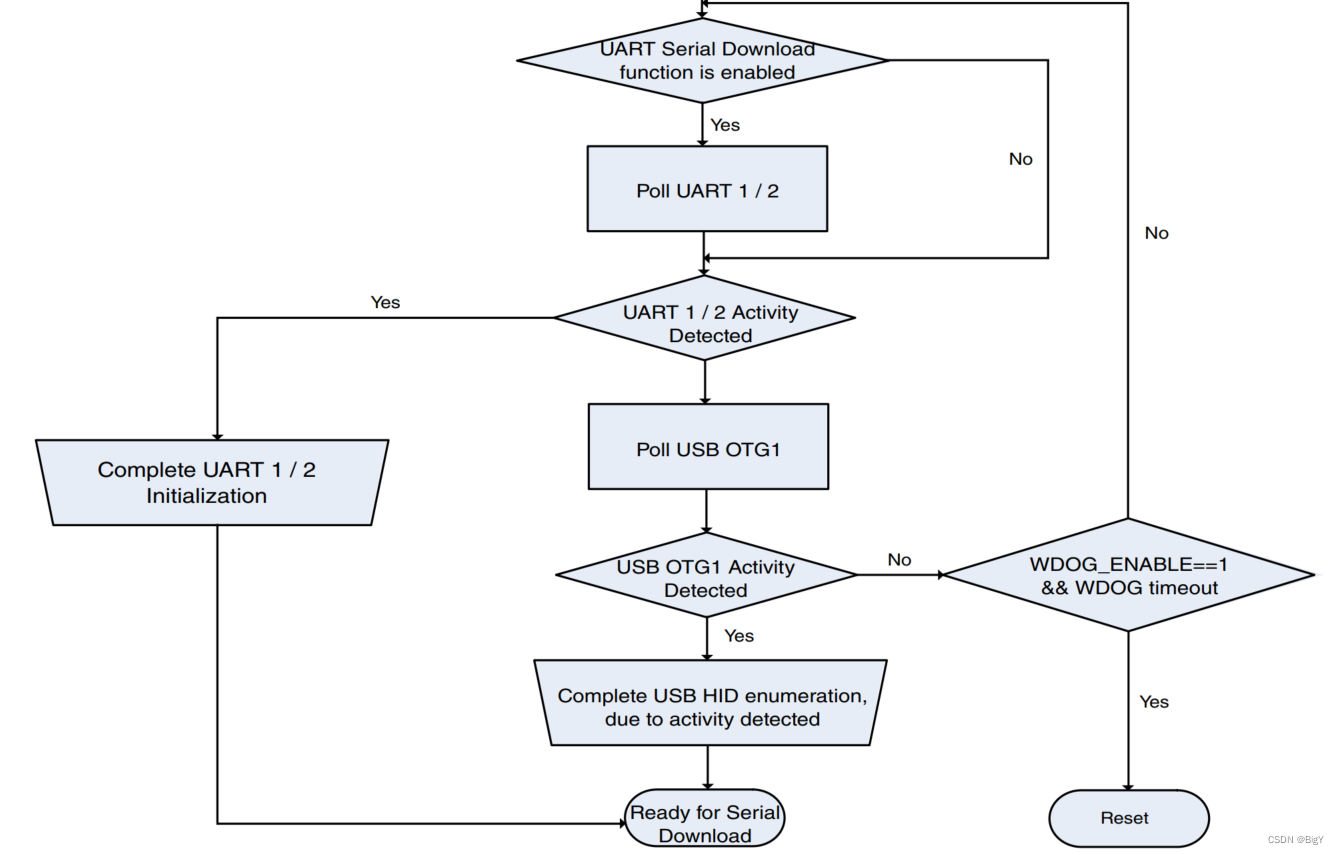

在这种模式下,如果WDOG_ENABLE eFuse为1,则ROM会根据保险丝WDOG Time-out Select(详见保险丝映射表)为WDOG1设置超时时间,并持续轮询USB和UART连接。如果在USB OTG1和UART 1/2上没有任何活动并且看门狗计时器超时,Arm核心将被复位。下载完图像后,它负责适当地管理看门狗复位。

8.2.5 Internal Boot mode (BOOT_MODE[1:0] = 0b10)

在BOOT_MODE[1:0]寄存器中的值为0b10选择了"内部引导"模式。在这种模式下,处理器会继续从内部引导ROM执行引导代码。引导代码会进行硬件初始化,从选择的引导设备加载程序图像,使用HAB库进行图像验证(参见引导安全设置),然后跳转到根据程序图像派生的地址。如果在内部引导过程中发生错误,引导代码会跳转到串行下载器(见串行下载器)。使用HAB进行安全引导在三种引导模式下均可实现。

当设置为"内部引导"时,引导流程可以由eFUSE设置的组合来控制,并且有选项使用通用GPIO引脚来覆盖保险丝设置。GPIO引导选择保险丝(BT_FUSE_SEL)确定在该模式下ROM是否使用GPIO引脚来控制选定数量的配置参数或者使用eFUSE。

- 如果BT_FUSE_SEL = 1,则所有引导选项由表8-2中描述的eFUSE控制。

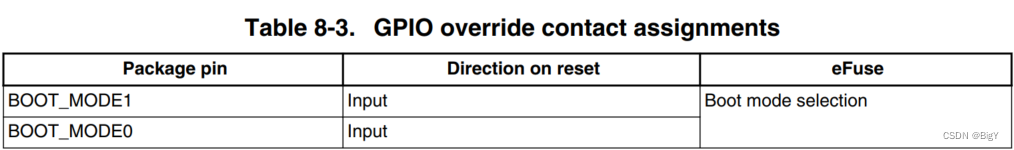

- 如果BT_FUSE_SEL = 0,则特定的引导配置参数可以使用GPIO引脚设置,而不是使用eFUSE。在此模式下可以覆盖的保险丝在表8-2的GPIO列中指示。表8-3提供了GPIO引脚的详细信息。

GPIO覆盖的使用意在开发过程中,因为这些引脚在部署产品中用于其他目的。NXP建议在部署产品中通过eFUSE来控制引导配置,并且仅将GPIO模式保留给开发和测试目的。

8.2.6 Boot security settings

内部引导模式使用三种安全配置之一。

- 封闭(Closed):该级别适用于出货安全产品。执行所有HAB功能并初始化安全硬件(安全控制器或SNVS进入安全状态),如果存在DCD,则进行处理,并且在程序图像执行之前由HAB进行验证。所有检测到的错误都将被记录,并且引导流程将被中止,并控制被传递给串行下载器。在此级别上,除非目标可执行图像经过认证,否则执行不会离开内部ROM。

- 开放(Open):该级别适用于非安全产品或者安全产品开发阶段。所有HAB功能的执行方式与封闭设备相同。安全硬件被初始化(除了SNVS处于非安全状态),如果存在DCD,则进行处理,并且在程序图像执行之前由HAB进行验证。所有检测到的错误都将被记录,但不会影响引导流程的继续进行,就好像这些错误没有发生一样。这种配置对于安全产品的开发非常有用,因为即使认证数据缺失或不正确,程序图像也会运行,并且可以检查错误日志以确定认证失败的原因。

- 返厂(Field Return):该级别适用于从已出货产品中退回的零件。

8.3 Device configuration

本节描述了控制引导ROM代码行为的外部输入。这包括引导设备选择(SPI、EIM、NOR、SD、MMC、QSPI等)、引导设备配置(SD总线宽度、速度等)和其他内容。通常,此配置的来源是嵌入芯片内部的eFUSEs。然而,某些配置参数可以从GPIO引脚获取,允许在开发过程中进一步灵活性。

8.3.2 GPIO boot overrides

提供的输入引脚在引导时进行采样,并根据BT_FUSE_SEL保险丝的设置,可以用于覆盖相应的eFUSE值。

8.3.3 Device Configuration Data (DCD)

DCD是指镜像中包含的配置信息(不在ROM内部),ROM解释这些信息以配置各种芯片上的外设。有关DCD的更多详细信息,请参阅设备配置数据(DCD)。

8.4 Device initialization

本节描述了ROM的详细信息并提供了初始化详细信息。这包括以下内容:

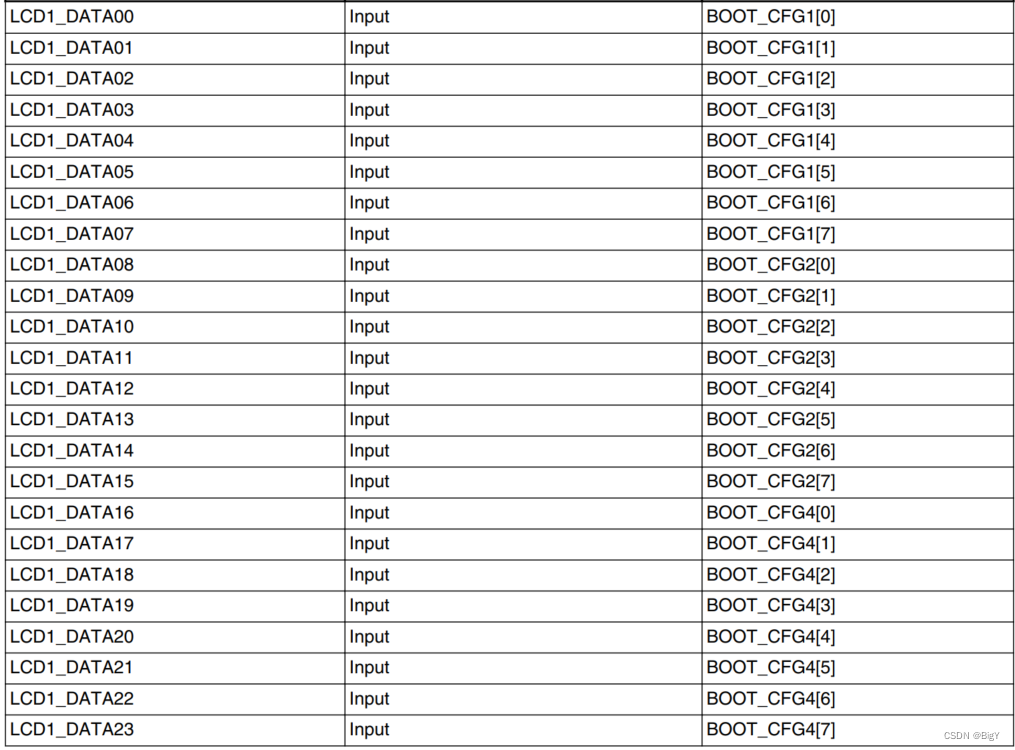

• ROM内存映射

• RAM内存映射

• ROM必须使用或更改POR寄存器默认值的芯片上块

• 时钟初始化

• 启用MMU / L2缓存

• 异常处理和中断处理

8.4.1 Internal ROM/RAM memory map

在引导后,整个OCRAM区域可以自由使用。

在引导后,整个OCRAM区域可以自由使用。

8.4.2 Boot block activation

在引导流程中,引导ROM会影响并激活多个不同的硬件模块,这些模块在引导过程中发挥着关键的作用。

引导ROM在引导过程中配置和使用以下硬件模块(按字母顺序列出)。需要注意的是,实际使用的模块取决于引导模式和引导设备的选择:

• APBH:用于驱动GPMI模块的DMA引擎

• BCH:具有AXI总线主机和与GPMI模块的私有连接的40位错误校正硬件引擎

• CCM:时钟控制模块

• ECSPI:增强型可配置串行外设接口

• EIM:用于NOR和OneNAND设备的外部接口模块

• GPMI:NAND控制器引脚接口

• OCOTP_CTRL:片上OTP控制器;OCOTP包含了eFUSE

• IOMUXC:I/O多路复用器控制,允许GPIO使用覆盖eFUSE引导设置

• IOMUXC GPR:I/O多路复用器控制通用寄存器

• DCP:数据协处理器

• QSPI:QuadSPI闪存

• SNVS:安全非易失存储

• SRC:系统复位控制器

• UART:通用异步收发器控制器

• USB:用于串行下载引导设备配置程序

• USDHC:超安全数字主机控制器

• WDOG-1:看门狗计时器

这些硬件模块在引导过程中起到了不同的作用,具体的使用方式和配置取决于引导模式和引导设备的选择。

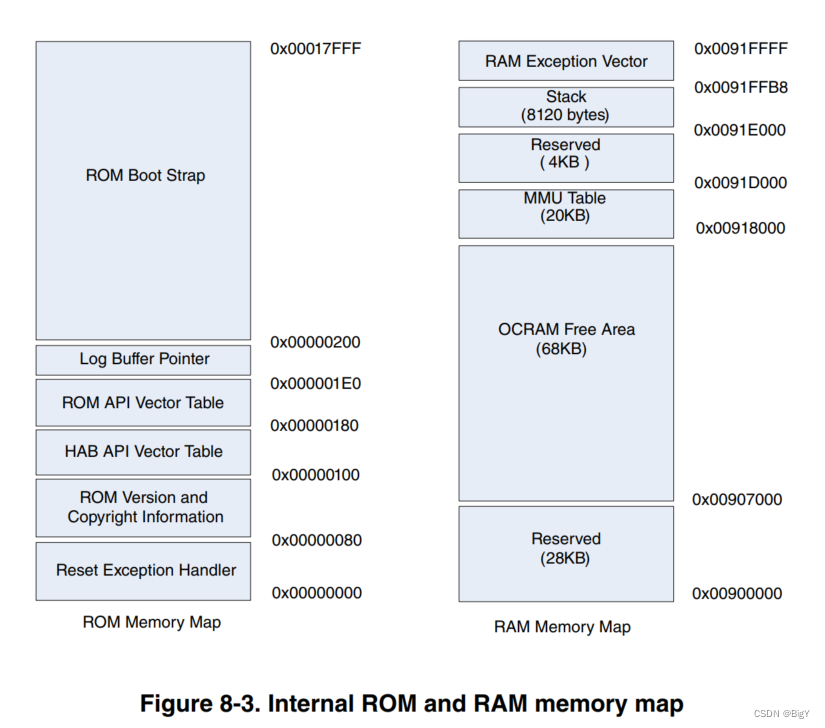

8.4.3 Clocks at boot time

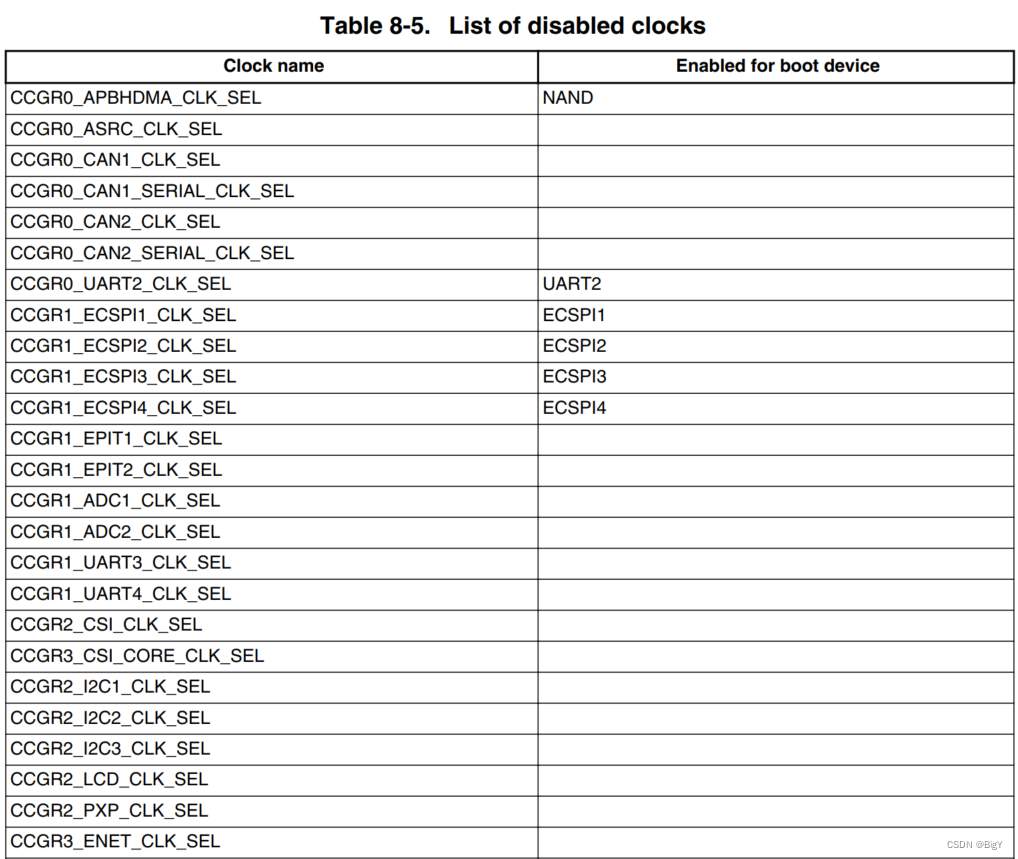

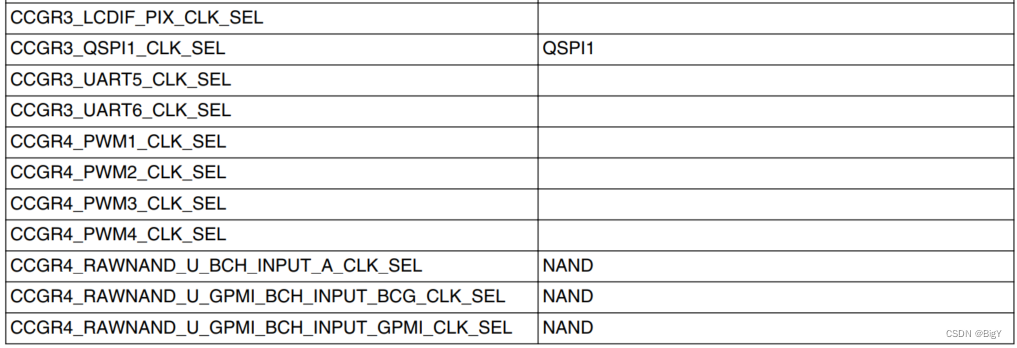

重置后,每个Arm核心都可以访问所有外设。然而,ROM代码会禁用以下表格中列出的时钟,但会保留第二列中列出的引导设备所需的时钟。

8.4.4 Enabling MMU and caches

引导ROM包括一个功能,可以启用内存管理单元(MMU)和缓存以提高引导速度。

在镜像下载开始时,L1指令缓存被启用。在镜像验证过程中,L1数据缓存、L2缓存和MMU被启用。当HAB认证完成后,ROM会禁用L1数据缓存、L2缓存和MMU。

L1指令缓存、L1数据缓存、L2缓存和MMU由eFuse控制。默认情况下,这些功能是启用的。

在使用SEC_CONFIG=Open并将图像向量表中的CSF指针设置为NULL时,即使在非安全引导时启用MMU也不会对引导性能产生影响。在这种配置下,建议烧录BT_MMU_DISABLE保险丝。

8.4.5 Exception handling

在ROM的开头位置,异常向量被用来将所有的Arm异常(除了复位异常)映射到一个内部RAM中的重复异常向量表中。

在CPU0的引导阶段,RAM向量指向ROM中的串行下载器。

引导完成后,程序镜像可以根据需要覆盖向量。下面的代码用于将ROM异常向量表映射到RAM中的重复异常向量表中。

; Map ROM Exception Vector Table

LDR R0, =VECTORS_RAM ; Load address of RAM vector table into R0

MCR p15, 0, R0, c12, c0, 0 ; Write RAM vector table address into VBAR

其中,VECTORS_RAM是指向RAM中的向量表的地址。该代码将RAM中异常向量表的地址写入VBAR寄存器,以将ROM异常向量表映射到RAM中的重复异常向量表中。

8.4.6 Interrupt handling during boot

在引导过程中不需要特殊的中断处理例程。在引导ROM执行期间,中断被禁用,并且可能在后续的引导阶段中被启用。

8.4.7 Persistent bits

引导ROM的某些模式需要在软复位后保留其值的寄存器。SRC通用寄存器用于此目的。

8.5 Boot devices (internal boot)

该芯片支持以下启动闪存设备:

• 位于CS0、16位总线宽度上的带有外部接口模块(EIM)的NOR闪存。

• 位于CS0、16位总线宽度上的带有EIM接口的OneNAND闪存。

• 通过GPMI-2接口支持原始NAND(MLC和SLC)和Toggle-mode NAND闪存。支持2 KB、4 KB和8 KB的页大小。支持8位总线宽度和2至40位BCH硬件ECC(错误纠正)。

• Quad SPI闪存。

• 通过USDHC接口支持SD/MMC/eSD/SDXC/eMMC4.4,支持高容量卡。

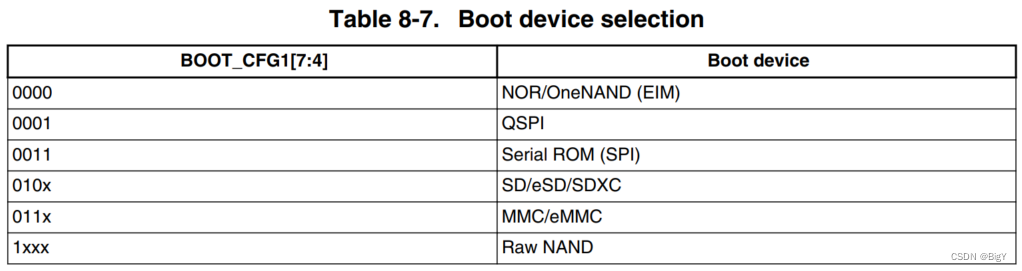

• 通过SPI(串行闪存)进行EEPROM引导。外部启动设备类型的选择由BOOT_CFG1[7:4] eFUSEs控制。详见下表:

8.5.1 NOR flash/OneNAND using EIM interface

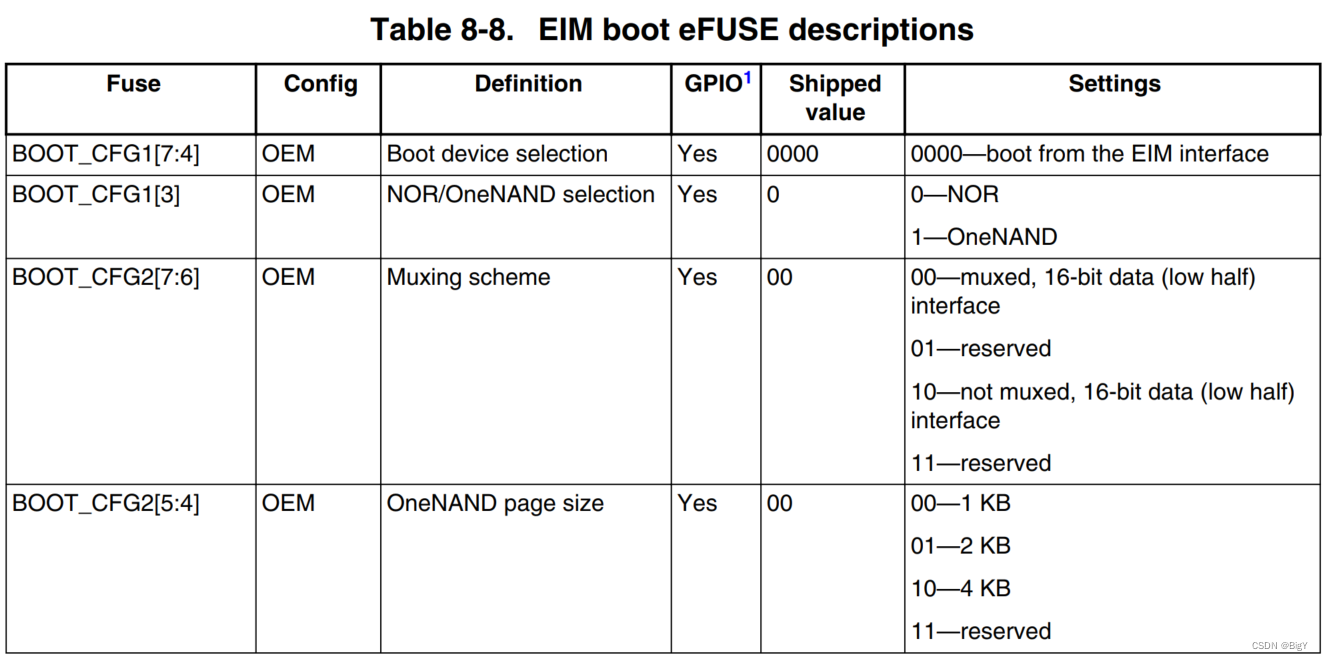

外部接口模块(EIM)以异步模式工作,并根据保险丝设置支持复用、地址/数据或非复用方案。当BT_FUSE_SEL保险丝完好无损时,此设置可以被GPIO设置所覆盖。请查看相应GPIO引脚的GPIO引导覆盖功能。

8.5.1.1 NOR flash boot operation

通过EIM接口支持从NOR闪存引导。ROM会读取Image Vector Table和Boot Data结构来确定是否可以直接从EIM地址空间执行镜像,或者将其复制到其他内存中。

Boot Data结构的start字段指定了镜像的最终位置(参见Image Vector Table和Boot Data)。

8.5.1.2 OneNAND flash boot operation

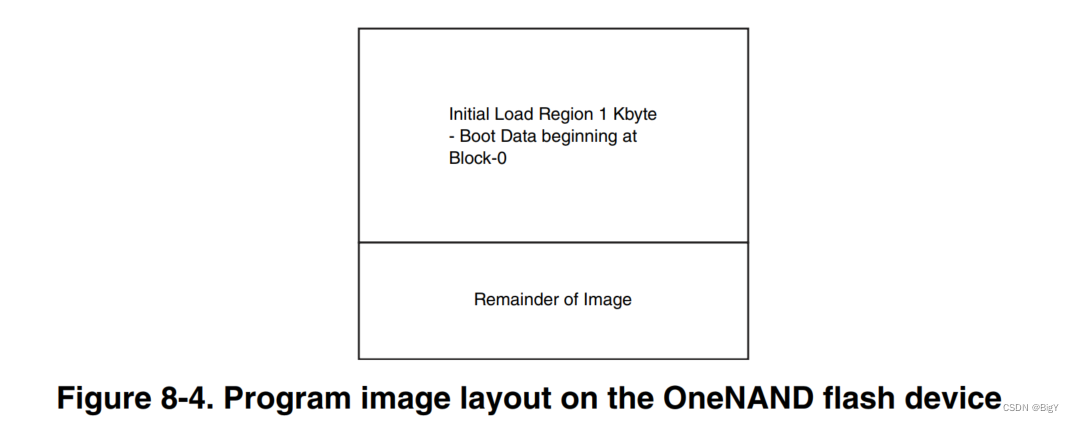

在系统上电时,OneNAND设备会自动将flash阵列的初始加载区域(扇区0和扇区1,页0,块0)的1 KB内容复制到其引导RAM(OneNAND的内部RAM)中。

注意:OneNAND引导RAM中包含的初始1 KB加载区域必须包含IVT、DCD和Boot Data结构。

接下来,ROM会处理DCD,然后开始将程序镜像内容复制到应用目标指针(位于Boot Data的start字段中,请参见Image Vector Table和Boot Data)。ROM会通过Boot Data结构中的size字段指定的长度来确定程序镜像的大小(请参见Image Vector Table和Boot Data)。如果由于任何原因从OneNAND设备加载数据失败,芯片将进入串行下载模式。否则,将继续从OneNAND设备引导。

以下图示了程序镜像在OneNAND引导设备上的布局:

在访问OneNAND设备之前,芯片在上电复位后会等待大约500微秒。这个延迟是为了等待OneNAND设备准备就绪。在这个初始的500微秒延迟之后,OneNAND设备将1 KB的初始加载区域复制到它的引导RAM中,这可能需要额外的70微秒时间。芯片会轮询OneNAND设备的中断状态寄存器,以确认第一个1 KB已经加载到OneNAND引导RAM中,然后才会继续进行引导流程。

在访问OneNAND设备之前,芯片在上电复位后会等待大约500微秒。这个延迟是为了等待OneNAND设备准备就绪。在这个初始的500微秒延迟之后,OneNAND设备将1 KB的初始加载区域复制到它的引导RAM中,这可能需要额外的70微秒时间。芯片会轮询OneNAND设备的中断状态寄存器,以确认第一个1 KB已经加载到OneNAND引导RAM中,然后才会继续进行引导流程。

8.5.2 NAND flash

引导ROM支持来自不同供应商的多种MLC/SLC NAND闪存设备,以及LBA NAND闪存设备。错误校正和控制(ECC)子块(BCH)用于检测错误。

8.5.2.1 NAND eFUSE configuration

引导ROM通过参数确定外部NAND闪存的配置,这些参数可以由eFUSE提供,也可以在引导过程中通过GPIO引脚采样获得。详细的参数信息请参考表8-10。

8.5.2.2 NAND flash boot flow and Boot Control Blocks (BCB)

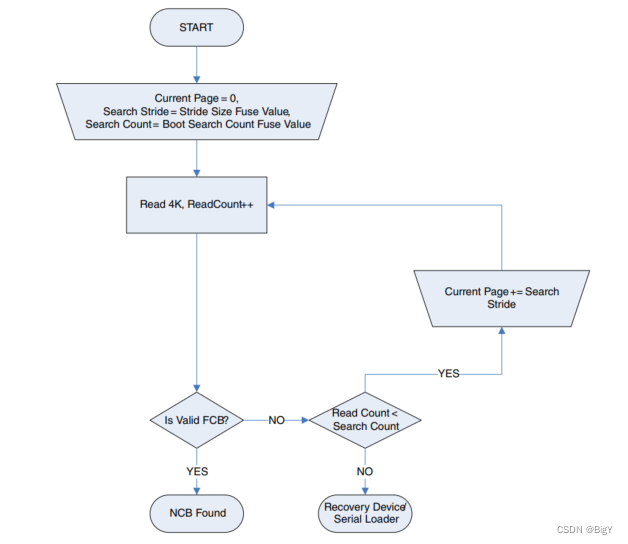

在NAND媒体初始化的过程中,引导ROM驱动程序使用安全的NAND时序来搜索包含最佳NAND时序、发现的坏块表(DBBT)搜索区域的页地址以及主固件和备用固件的起始页地址的固件配置块(FCB)。要使用的硬件ECC级别嵌入在FCB块中。FCB数据结构也使用ECC进行保护。驱动程序读取第一个扇区的原始2112字节,并通过软件ECC引擎运行,确定FCB数据是否有效。

如果找到了FCB,则会加载最佳的NAND时序以进行进一步的读取。如果ECC失败,或者指纹不匹配,块搜索状态机会将页号增加到搜索步幅数目的页,直到已经读取了SearchCount页。

如果搜索未能找到有效的FCB,NAND驱动程序会报错,并且引导ROM会进入串行下载模式。

FCB包含了DBBT搜索区域的页地址,以及主引导和备用引导镜像的页地址。DBBT在DBBT搜索区域中进行搜索,就像FCB一样进行搜索。在读取了FCB之后,DBBT被加载,并使用FCB中的起始页地址加载主引导或备用引导镜像。

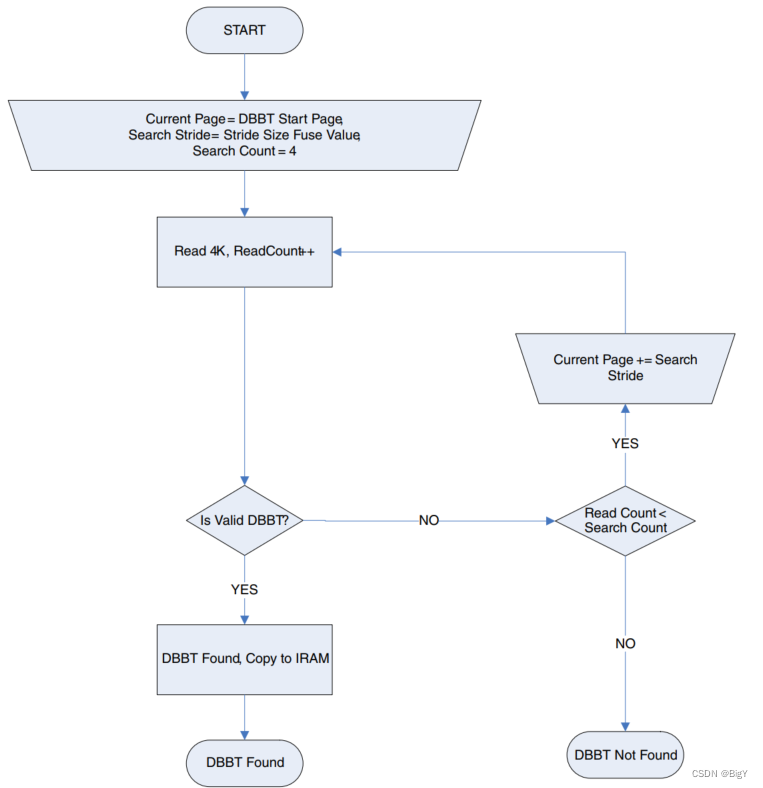

以下是FCB搜索状态图示:

当找到FCB时,引导ROM会搜索发现的坏块表(DBBT)。如果FCB中的DBBT搜索区域为0,则ROM会假定NAND设备引导区域上没有坏块。请参考下图以获取DBBT搜索流程:

BCB搜索和加载函数还监视ECC纠正阈值,并在阈值超过最大ECC纠正能力时设置PERSIST_BLOCK_REWRITE持久位。

如果在主引导镜像读取过程中存在错误数量超过ECC能够纠正的页面,引导ROM会打开PERSIST_SECONDARY_BOOT位,并执行软件复位(软件复位后,使用备用镜像)。

如果在备用镜像读取过程中存在错误数量超过ECC能够纠正的页面,引导ROM会进入串行加载模式。

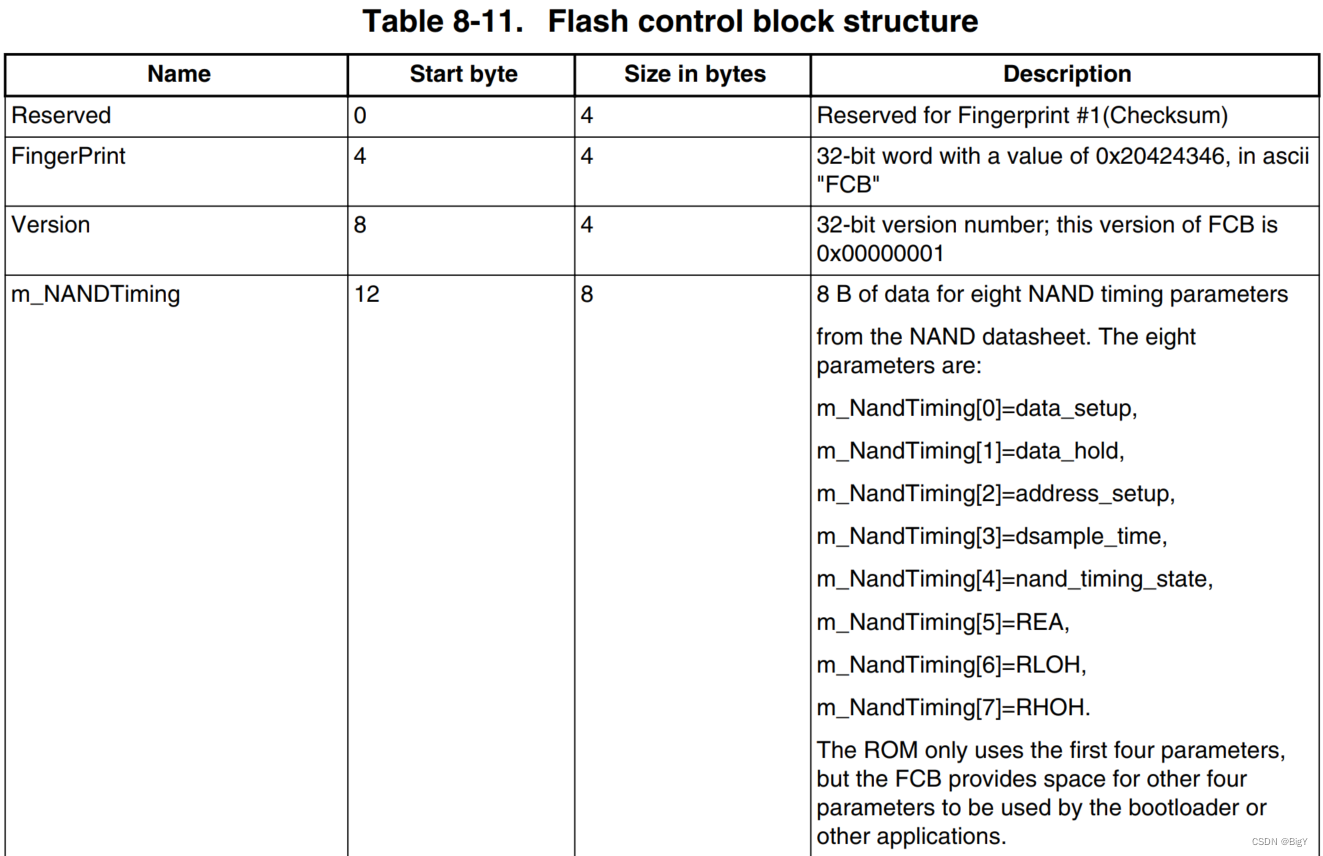

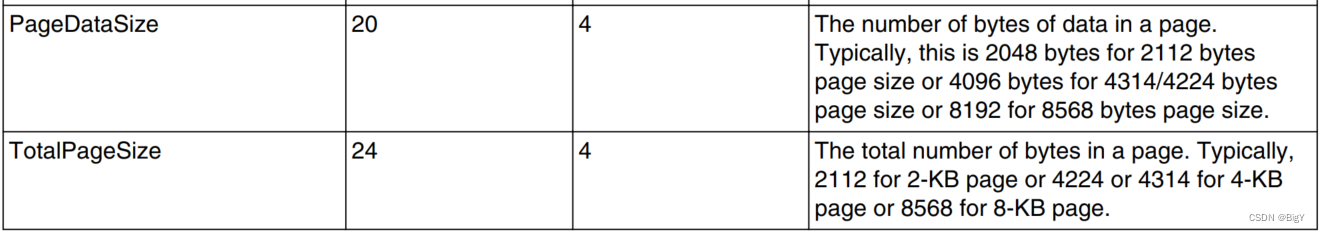

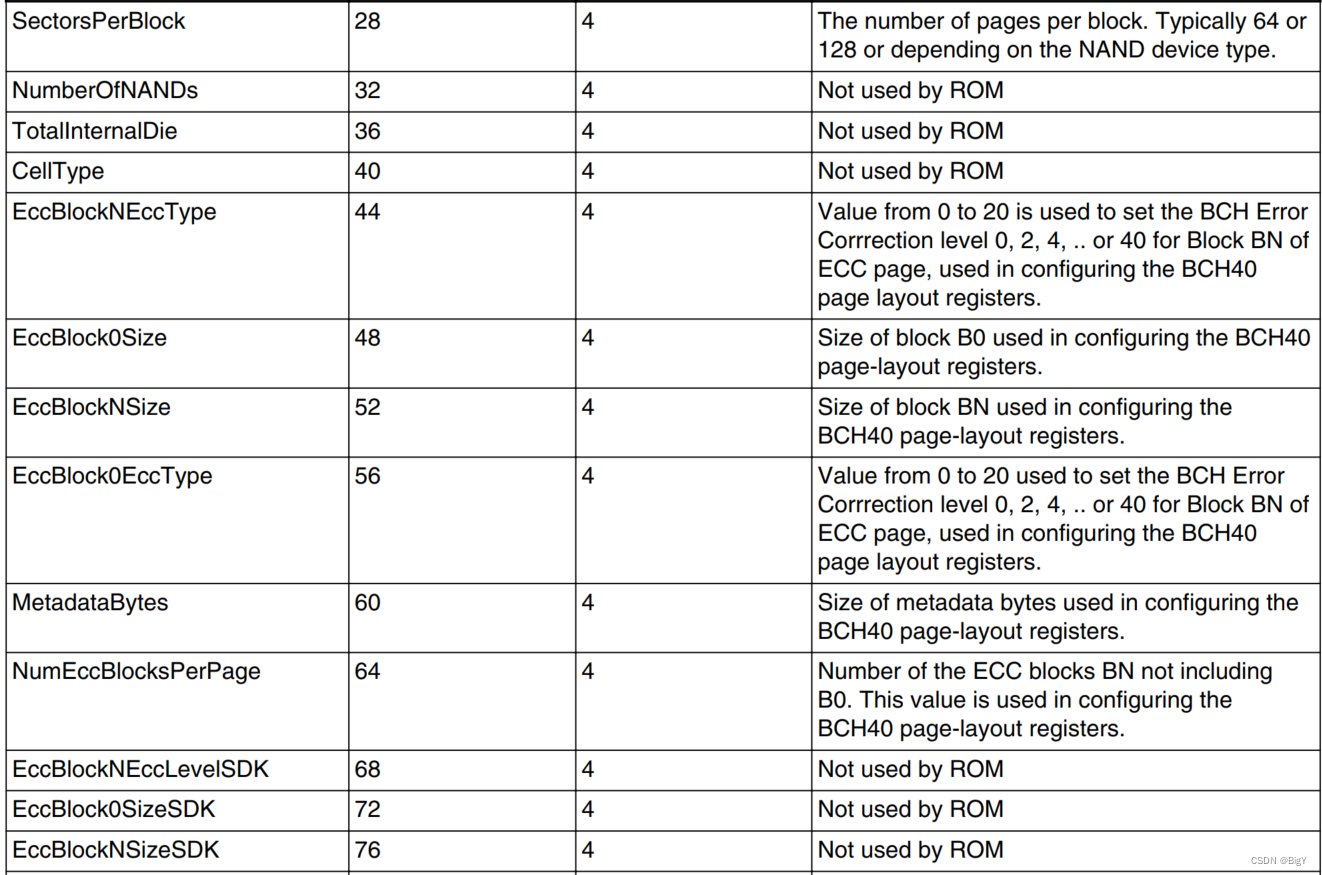

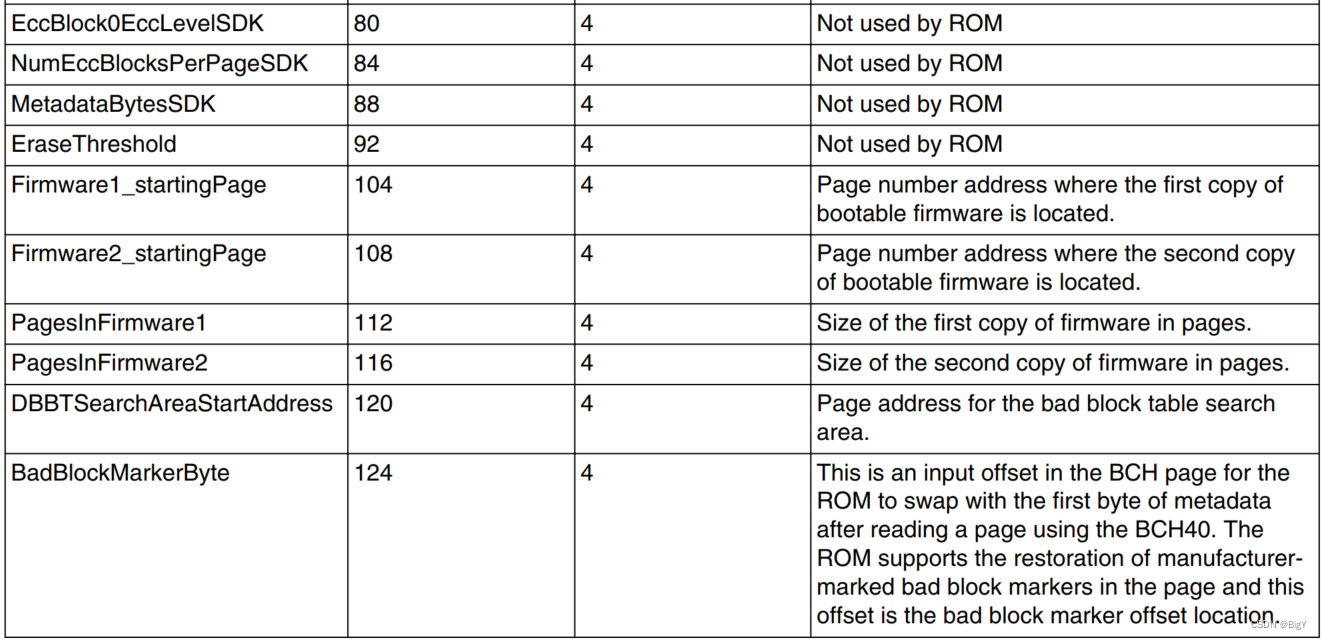

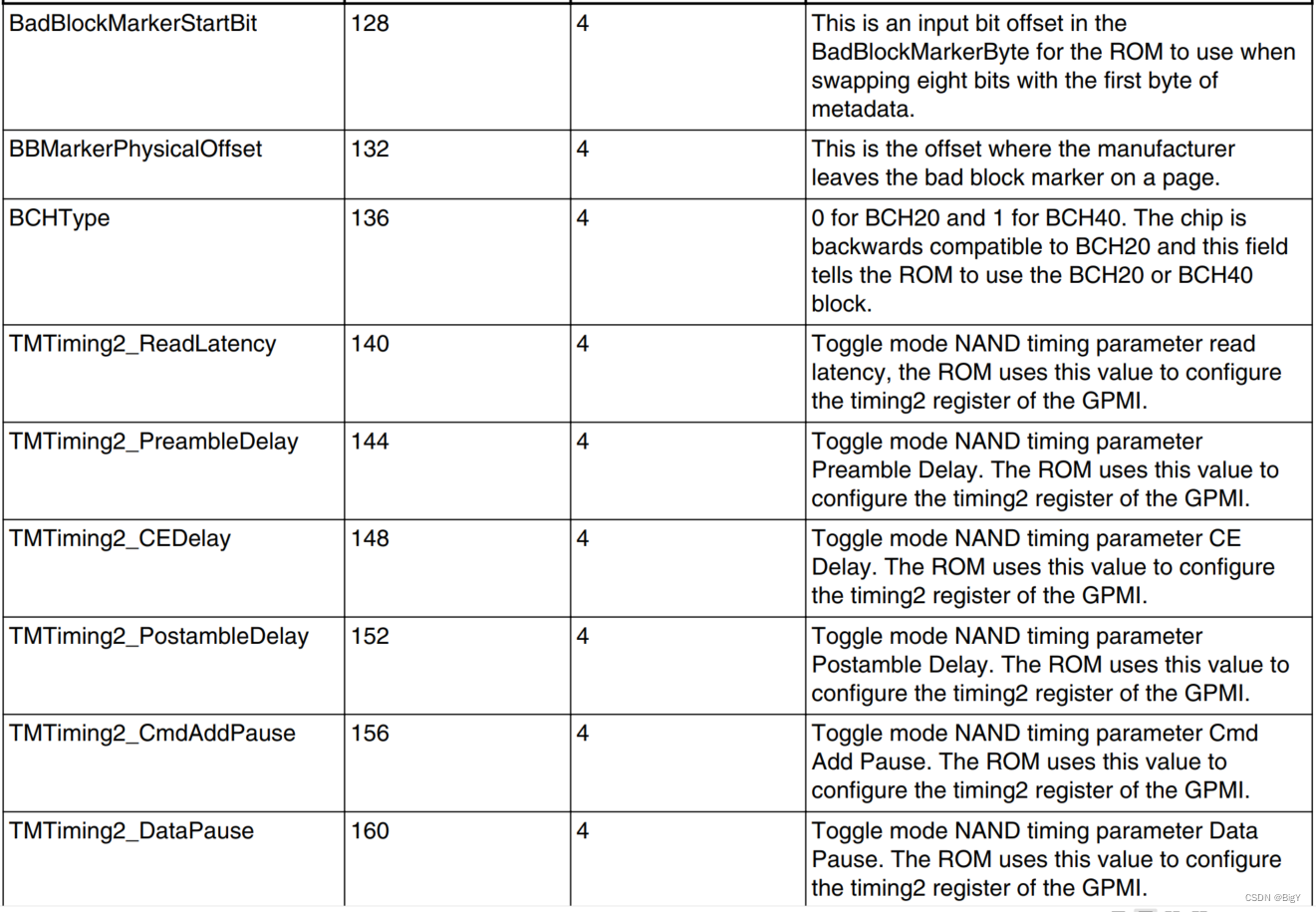

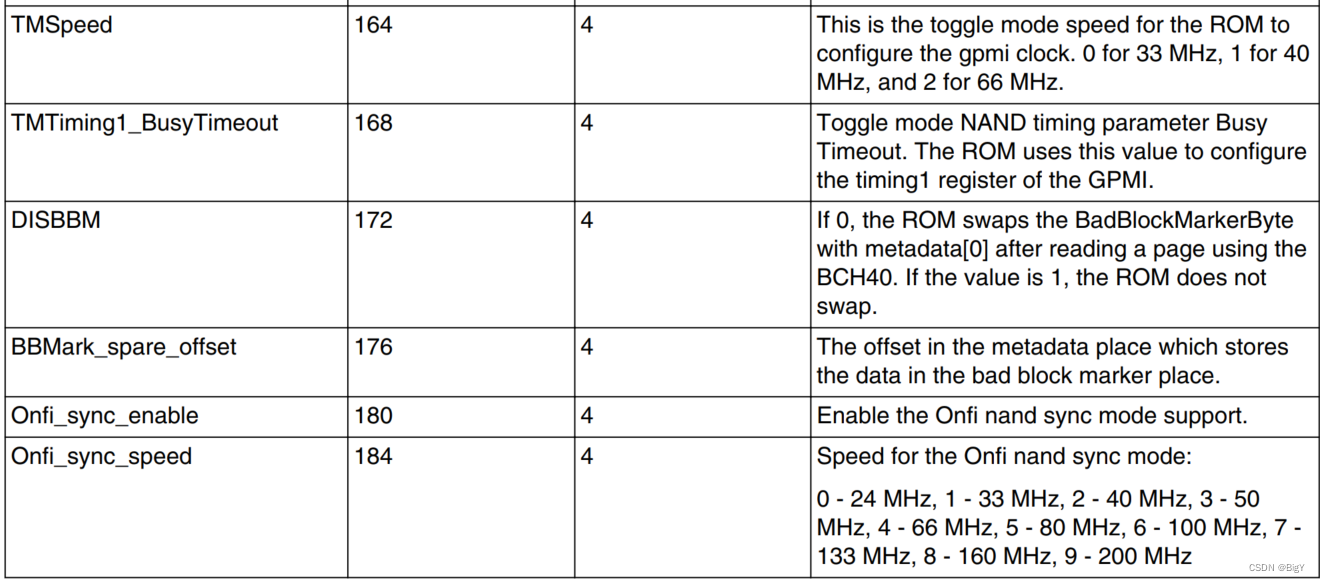

8.5.2.3 Firmware configuration block

FCB是第一个好块中的第一个扇区。FCB必须在搜索区域的每个搜索步幅处存在。

搜索区域包含每个步幅距离处FCB的副本,因此,如果第一个NAND块损坏,ROM会在下一个NAND块中找到其副本。搜索区域必须跨越至少两个NAND块。DBBT搜索区域、FW1和FW2的位置信息都在FCB中指定。以下表格显示了闪存控制块的结构:

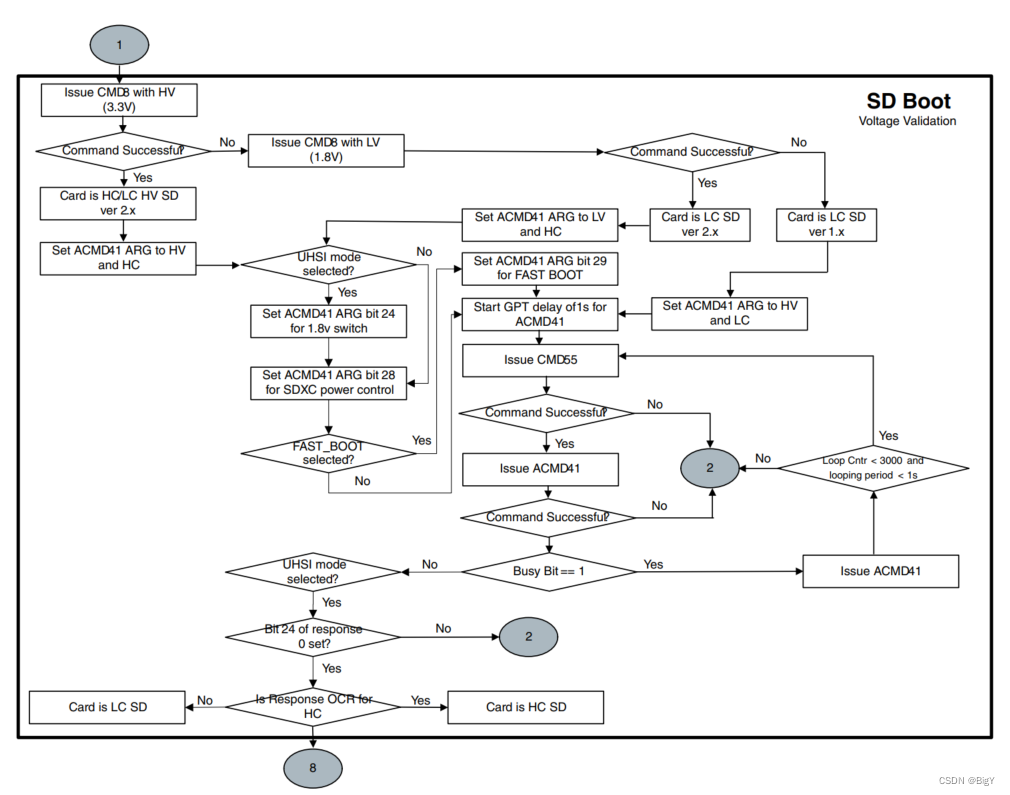

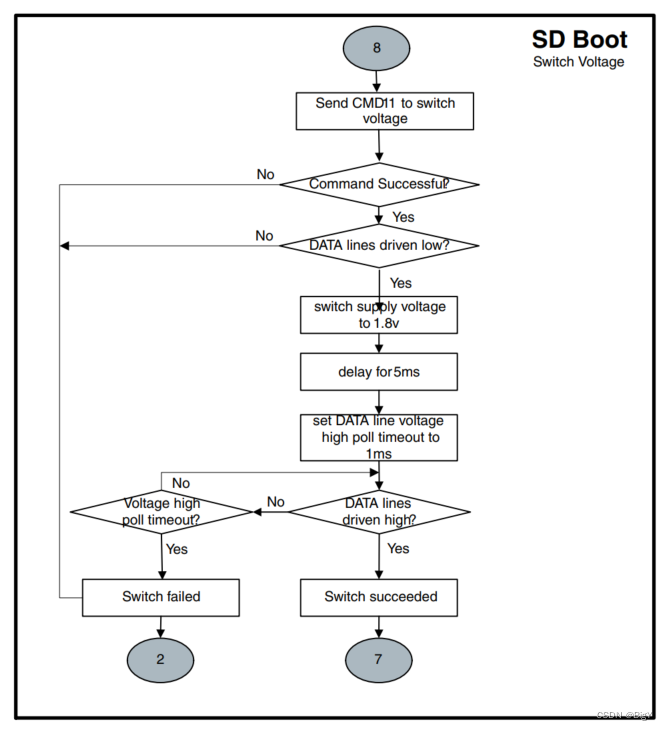

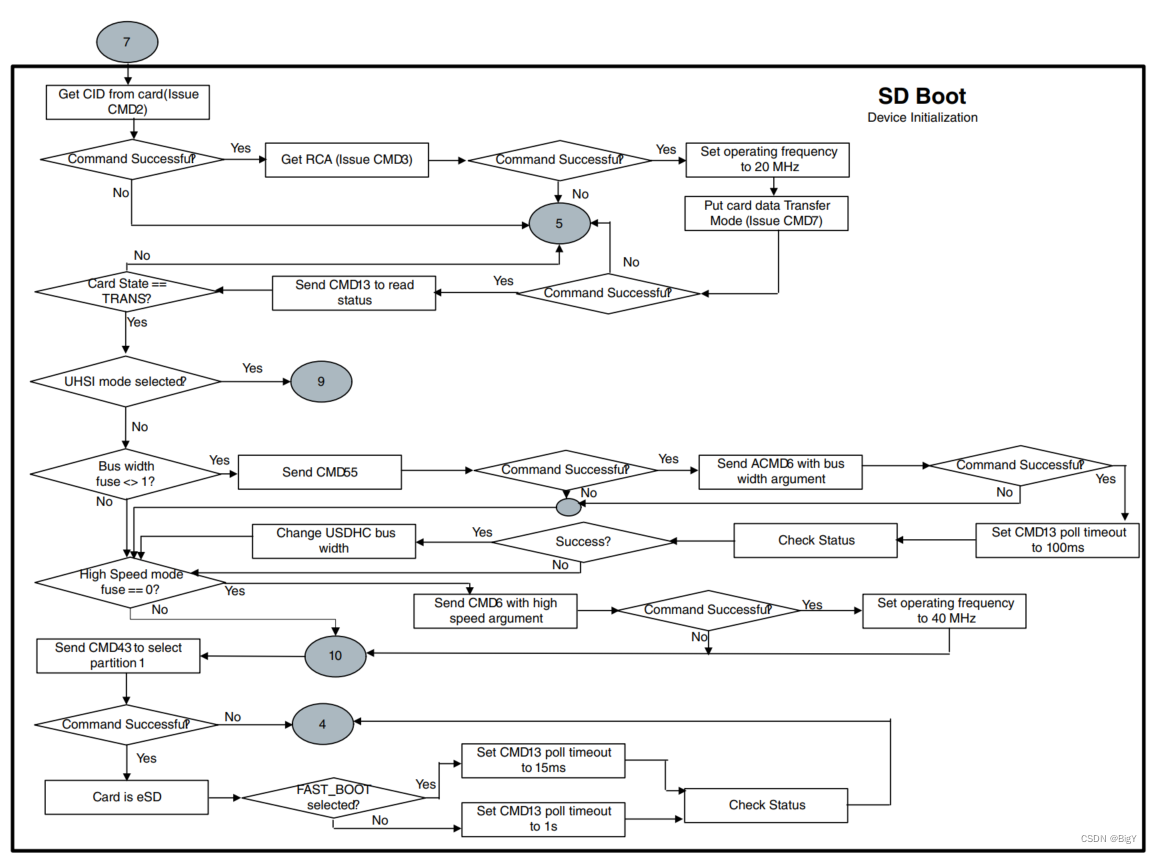

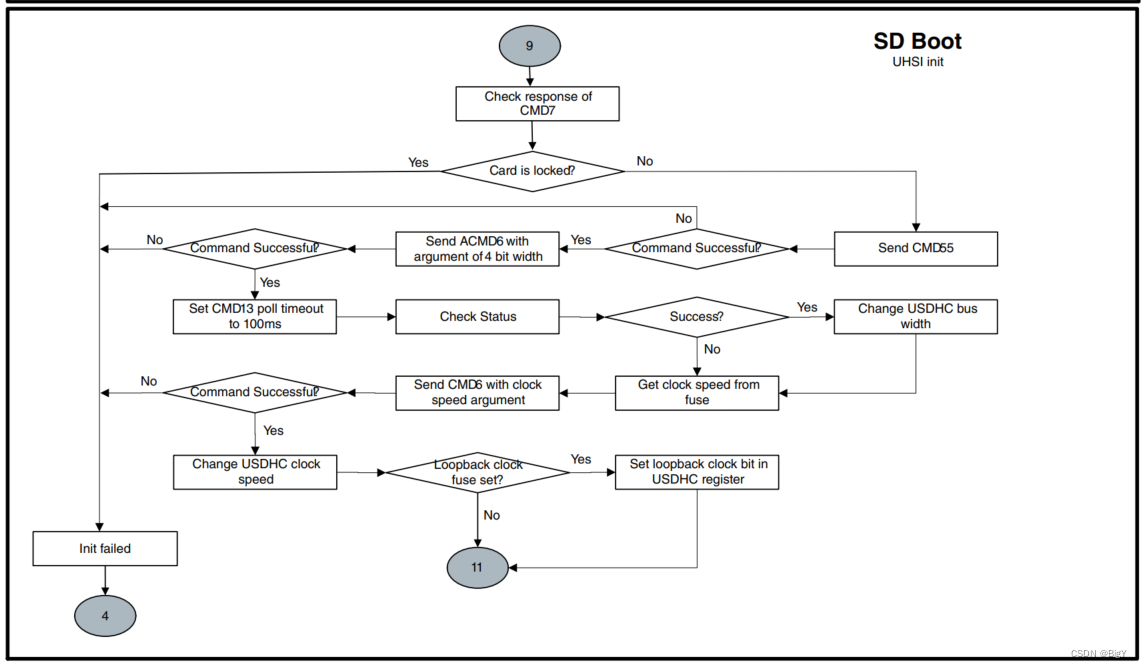

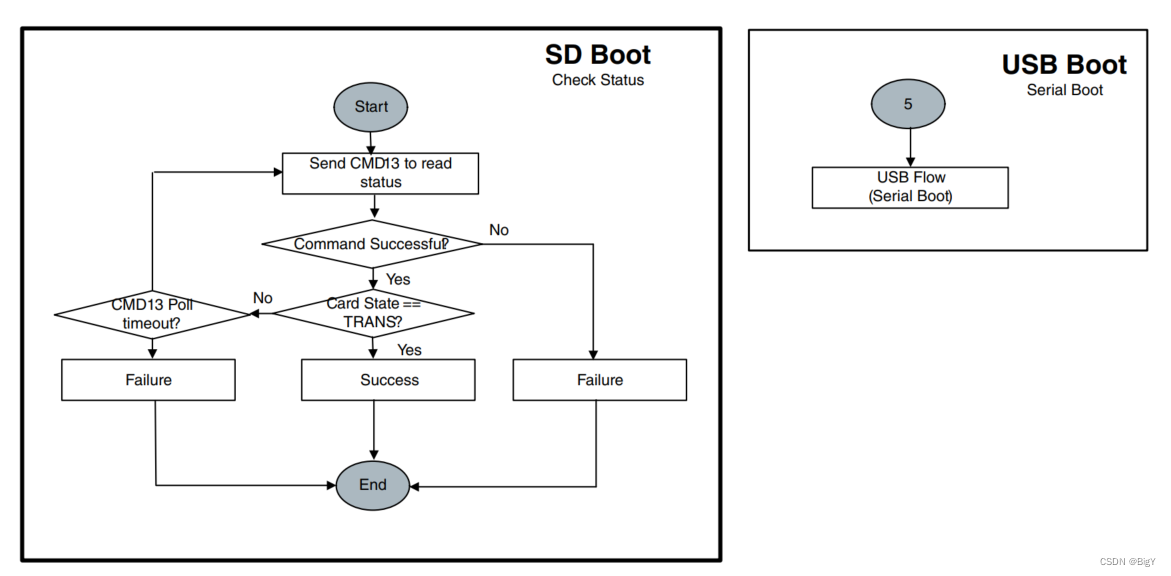

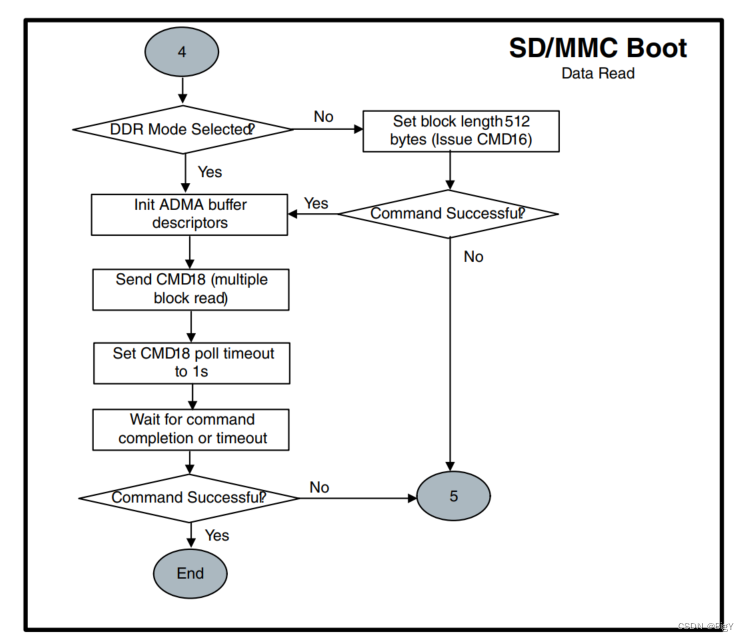

8.5.3 Expansion device

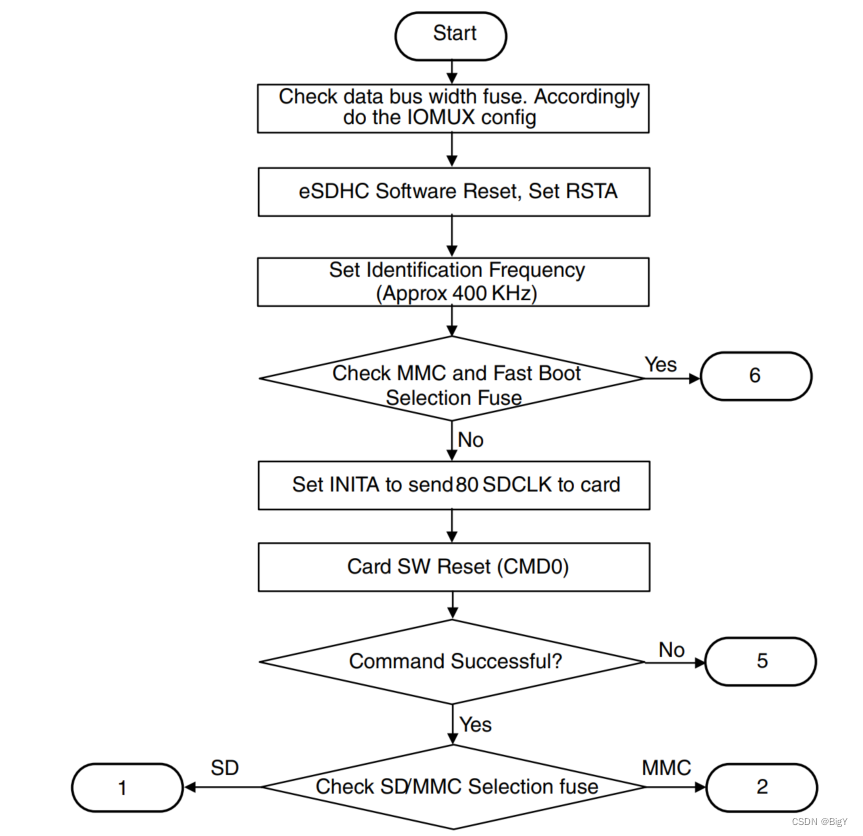

OM支持从符合MMC/eMMC和SD/eSD标准的设备引导。 MMC(MultiMediaCard)是一种闪存存储卡标准,而eMMC(embedded MultiMediaCard)则是一种集成在设备内部的闪存存储解决方案。SD卡(Secure Digital card)和eSD卡(embedded Secure Digital card)也是常见的闪存存储设备标准。ROM能够支持从这些设备中引导系统。

8.5.3.1 Expansion device eFUSE configuration

SD/MMC/eSD/eMMC/SDXC引导可以使用USDHC端口进行,这取决于BOOT_CFG2[4:3](端口选择)熔丝的设置,或者与引导时的GPIO输入值相关联。 USDHC代表可扩展SD主机控制器,是用于SD卡和MMC卡的高速接口。BOOT_CFG2[4:3]熔丝是用于配置引导选项的寄存器。因此,可以通过设置熔丝或GPIO输入来确定使用哪个端口进行SD/MMC/eSD/eMMC/SDXC引导。

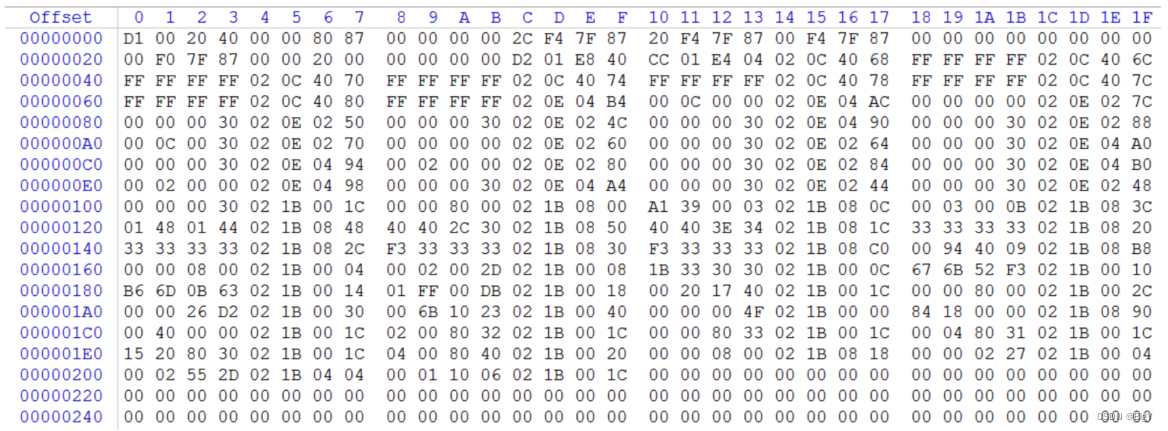

MMC/SD/eSD/SDXC/eMMC可以连接到任何USDHC块,并且可以通过将4 KB的数据从MMC/SD/eSD/eMMC设备复制到内部RAM来进行引导。在检查程序图像中的图像向量表头值(0xD1)后,ROM代码执行DCD检查。在成功提取DCD后,ROM代码从引导数据结构中提取目标指针和要从中执行代码的RAM设备的图像长度。

SD/MMC引导加载的最大图像大小为32 MB。这是由于ROM分配的有限数量的uSDHC ADMA缓冲描述符。

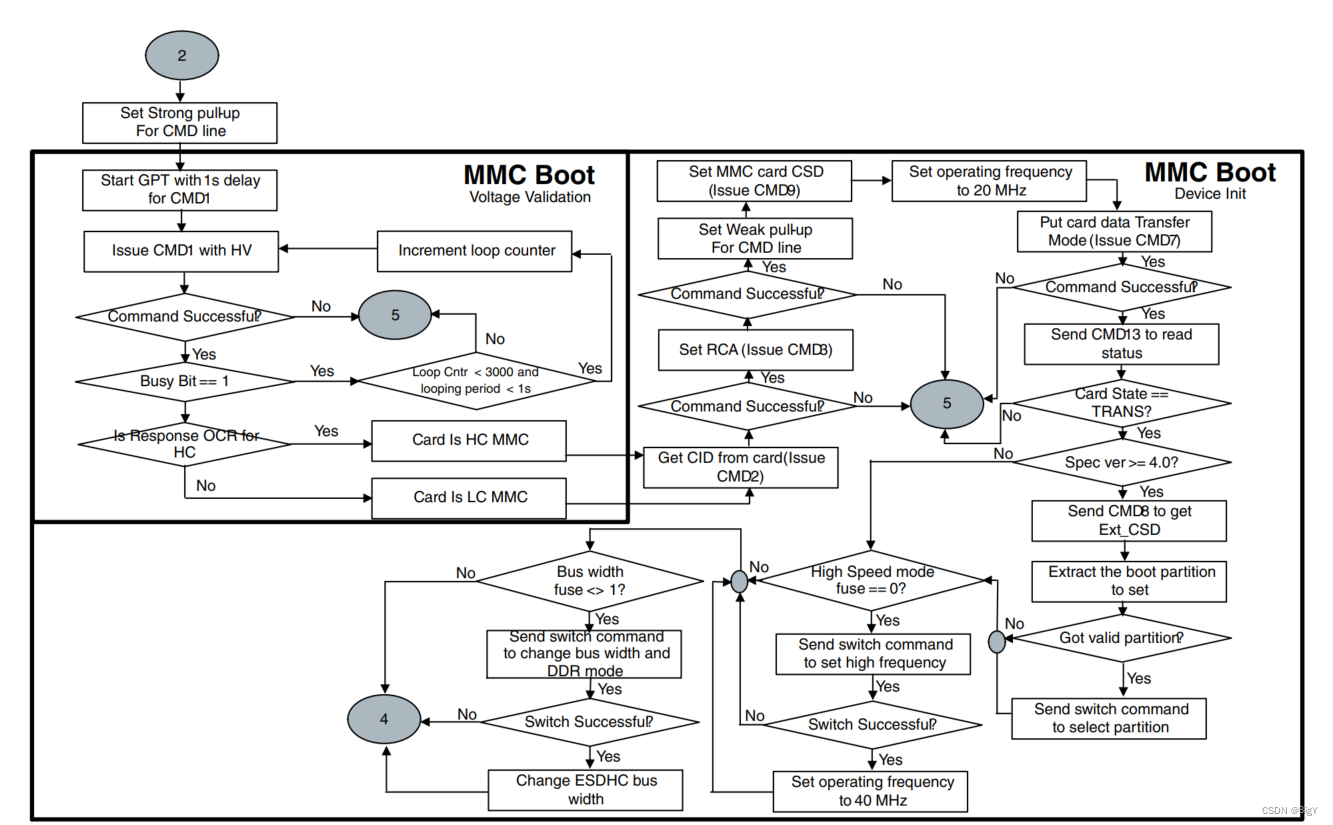

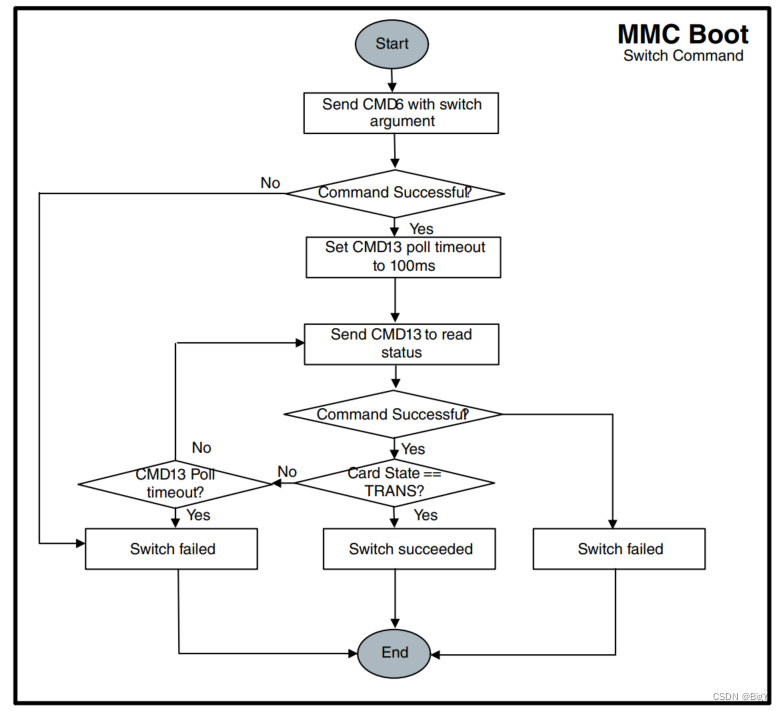

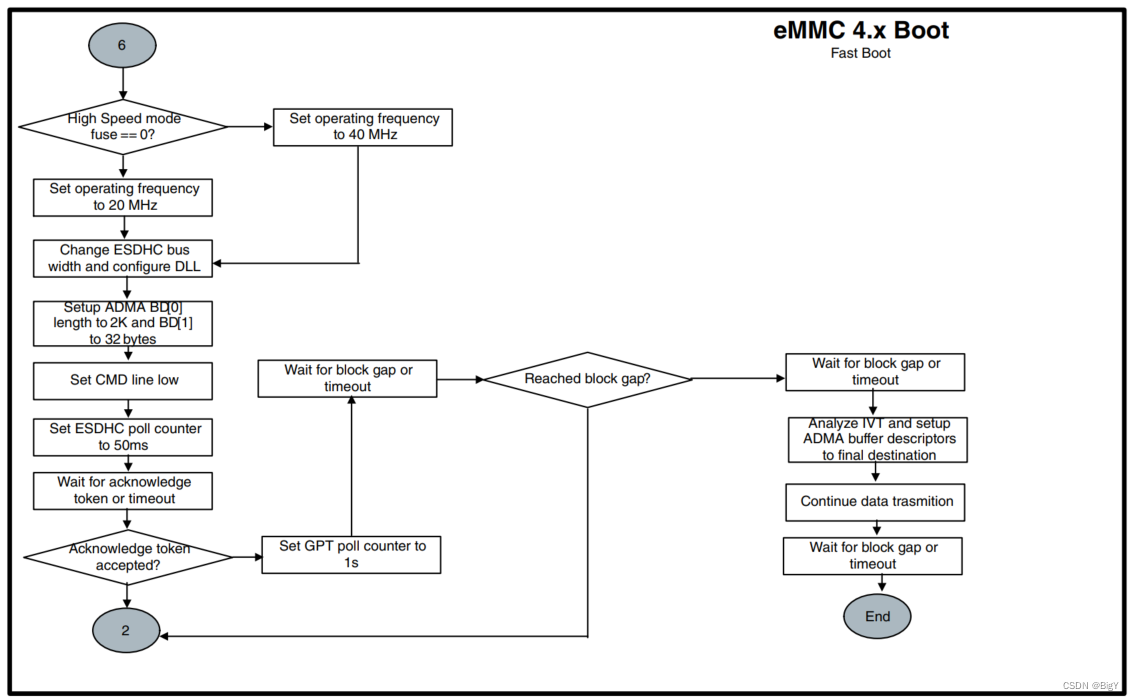

8.5.3.2 MMC and eMMC boot

8.6 QuadSPI serial flash memory boot

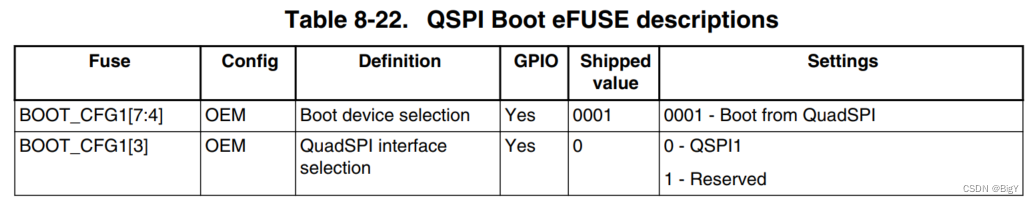

8.6.1 QuadSPI eFUSE configuration

8.6.2 QuadSPI serial flash BOOT operation

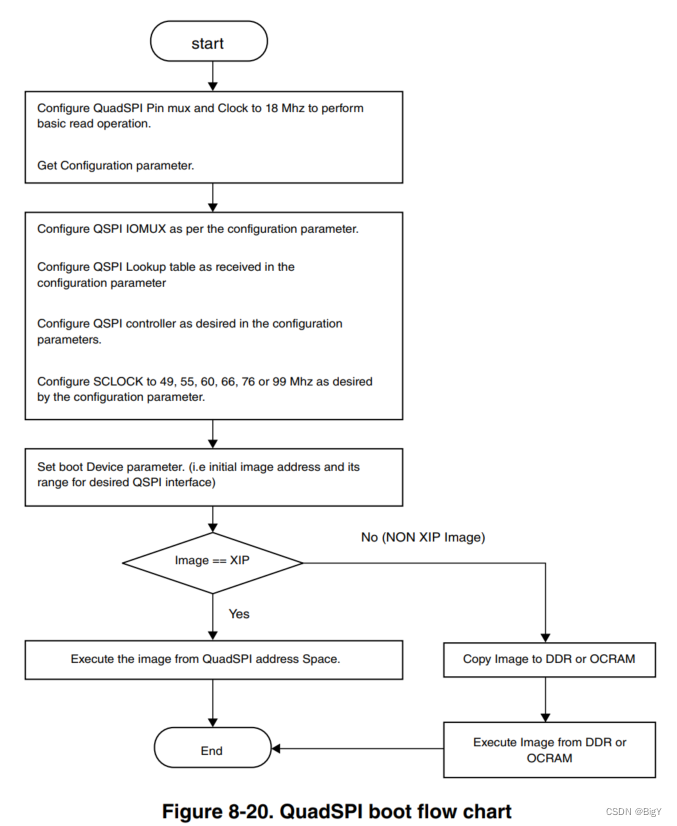

如果将BOOT_CFG1[7:4]熔丝编程为0001(如QuadSPI eFUSE配置表中所示),则引导ROM将尝试从QuadSPI闪存引导。 ROM根据QuadSPI eFUSE配置中的Fuse位BOOT_CFG1[3]初始化所选的QuadSPI接口。QuadSPI接口初始化是一个两步过程。

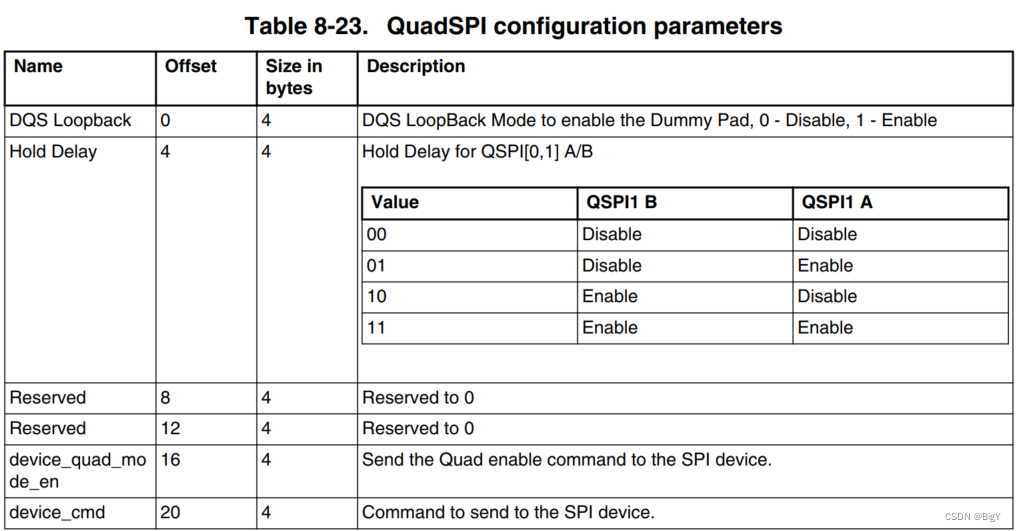

ROM期望在串行闪存的偏移0x400处,长度为512字节的序列闪存中存在QuadSPI配置参数(如QuadSPI配置参数中所述)。 ROM使用QuadSPI接口的LUT中配置的默认读取命令以18 MHz的SCLOCK操作读取这些配置参数。

在第二步中,ROM使用从串行闪存读取的配置参数配置所选的QuadSPI接口,并启动引导过程。有关QuadSPI配置参数的详细信息,请参阅表19-12,并参阅QuadSPI引导流程图以获取QuadSPI的详细引导流程图。

串行闪存支持从XIP和非XIP镜像引导。对于XIP引导,镜像必须构建为QuadSPI地址空间的镜像,而对于非XIP引导,镜像可以构建为从DDR或OCRAM执行。

对于QUAD模式引导,引导ROM期望在引导开始之前,QSPI闪存内部已经设置了四线模式使能位(Quad Enable bit)。因此,在编程时,必须在闪存的非易失性寄存器中设置QUAD使能位。

如果SPI闪存设备需要四线模式使能命令,可以通过以下配置结构字段发送:

device_quad_mode_en、device_cmd、write_cmd_ipcr、write_enable_ipcr、busy_bit_offset和read_status_ipcr。

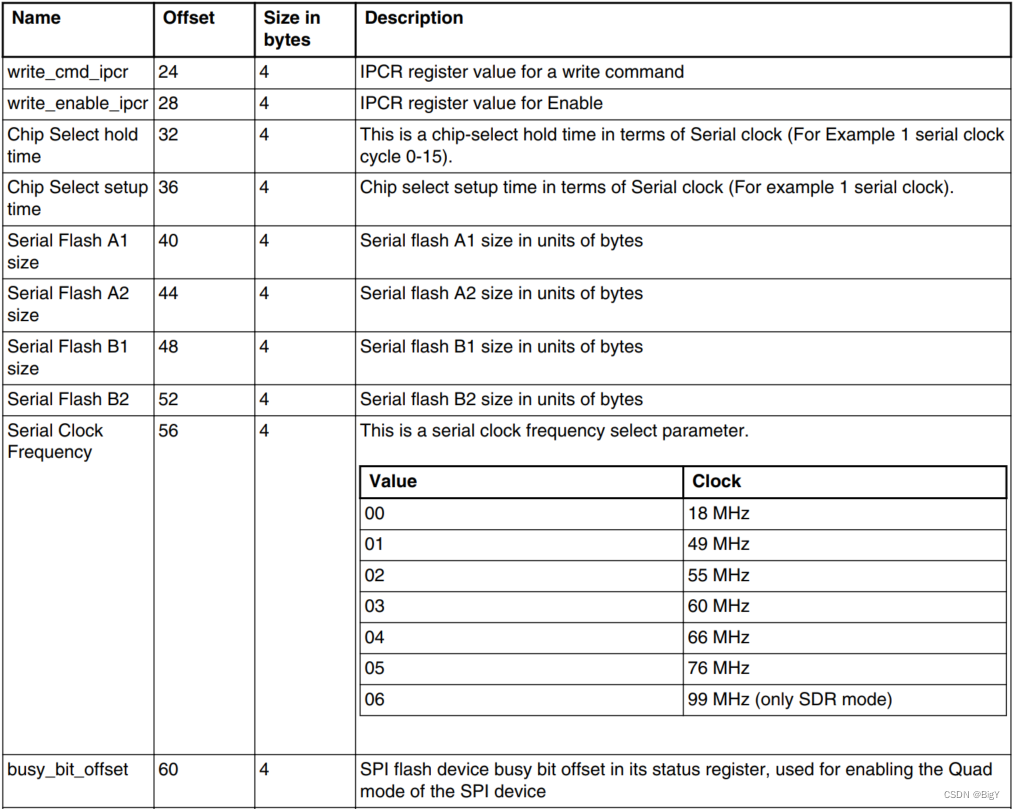

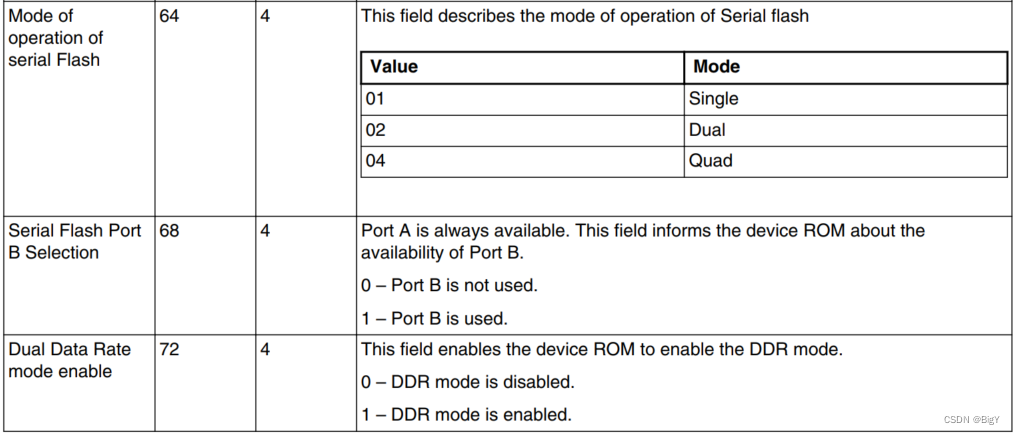

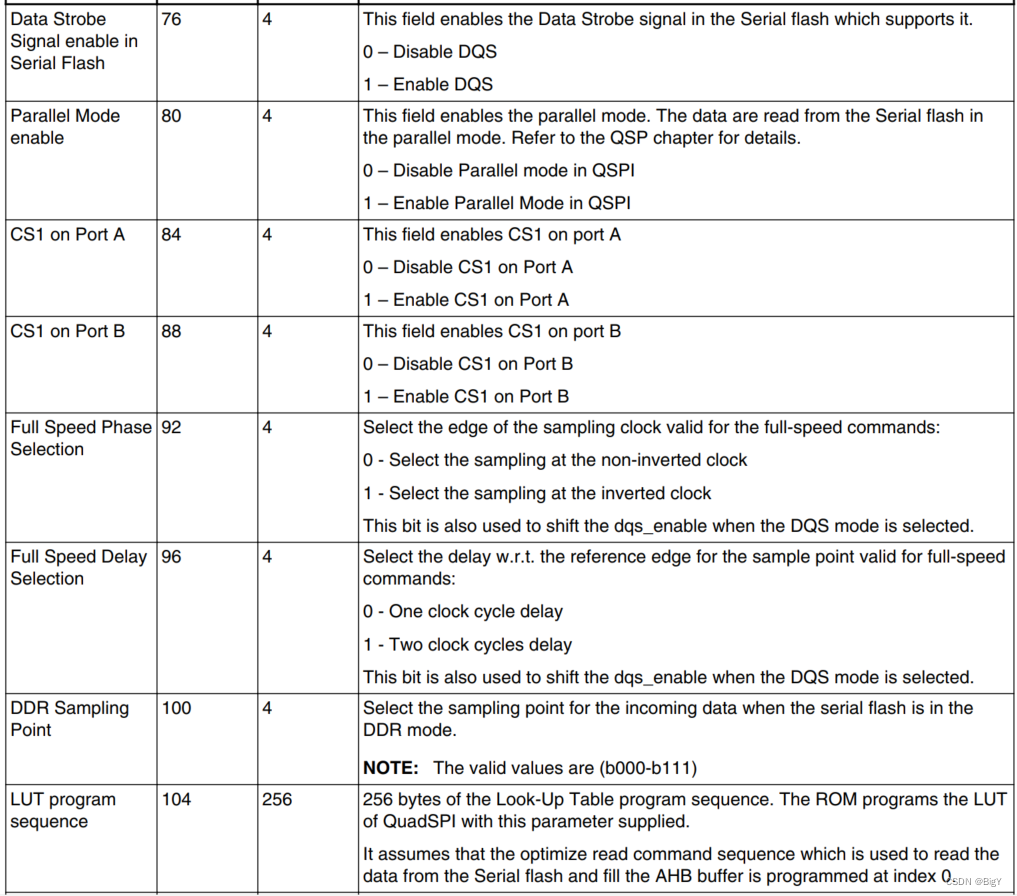

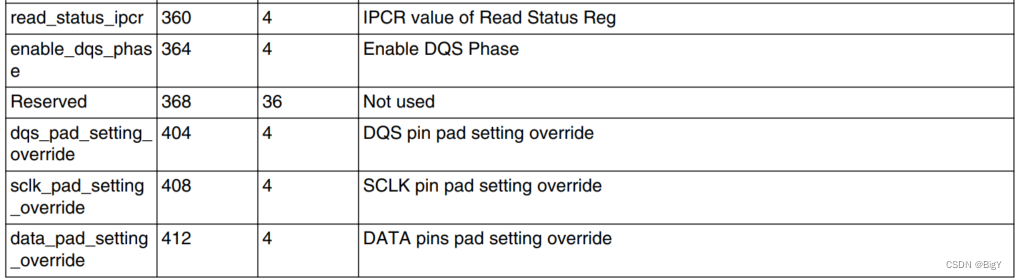

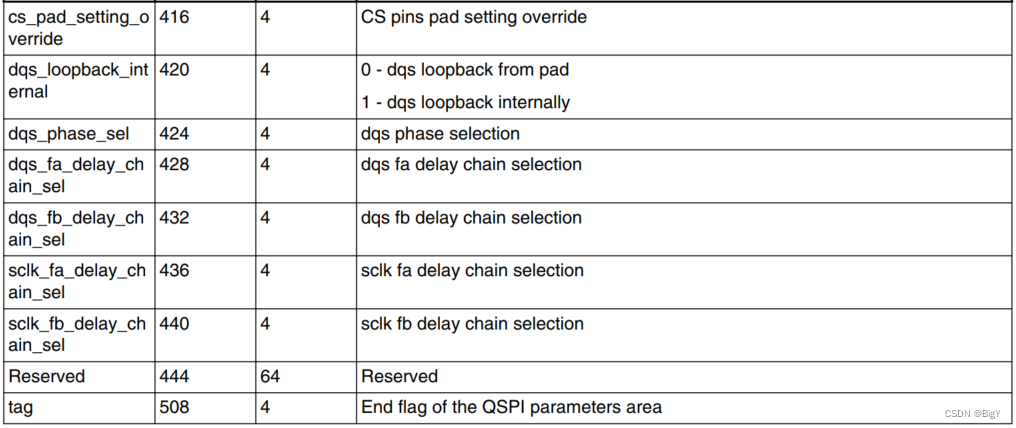

8.6.3 QuadSPI configuration parameters

QuadSPI配置参数表在引导镜像中以固定偏移量0x400(368 B)的QSPI NOR A1基地址处构建。该表列出了各种QuadSPI配置参数:

8.6.5 QuadSPI boot flow chart

如果闪存在LUT程序序列中配置为“高性能模式”(其中命令仅生成一次),则外部复位必须路由到闪存复位,以允许在与上电复位不同的设备复位情况下重新启动。在进入任何低功耗模式之前,应用程序必须退出该高性能模式,其中设备应该从QSPI闪存重新启动以退出低功耗模式。通常,在复位后,设备不会理解外部闪存中的任何保留配置。

8.7 Program image

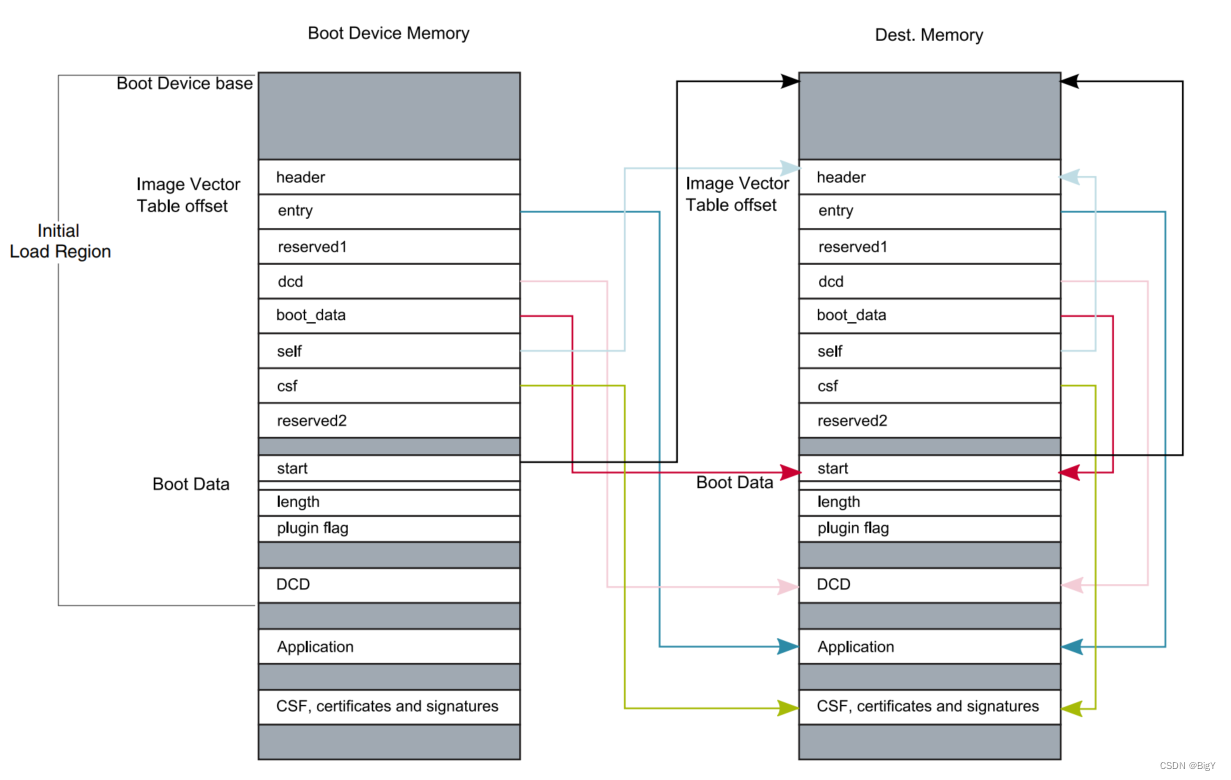

本节描述了必须包含在用户程序镜像中的数据结构。程序镜像包括:

• 镜像向量表 - 位于固定地址上的指针列表,ROM会检查这些指针以确定程序镜像的其他组件的位置。

• 引导数据 - 表示程序镜像的位置、以字节为单位的程序镜像大小和插件标志的表格。

• 设备配置数据 - IC配置数据。

• 用户代码和数据。

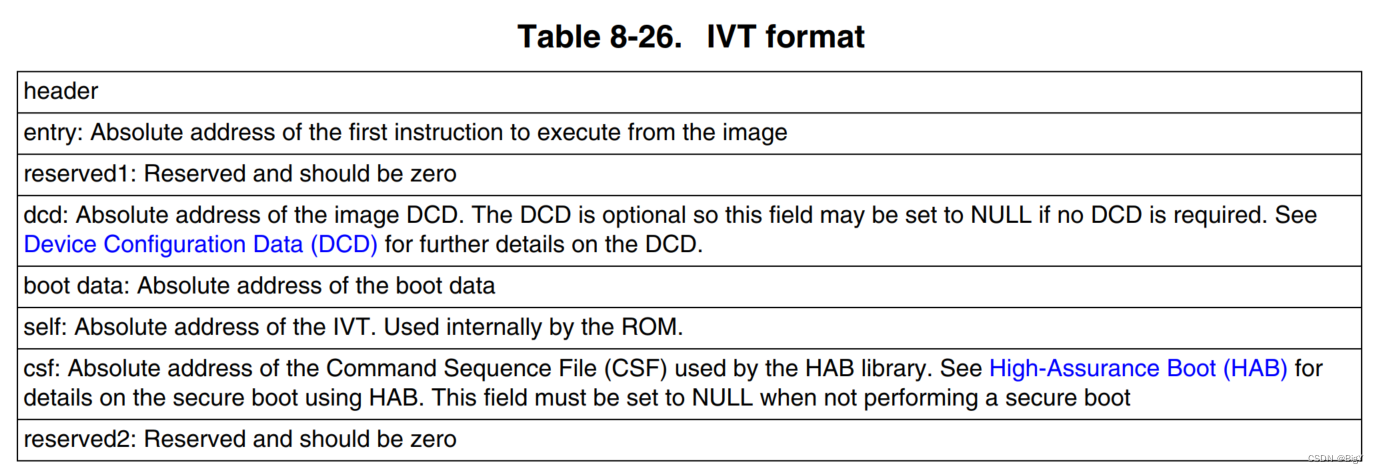

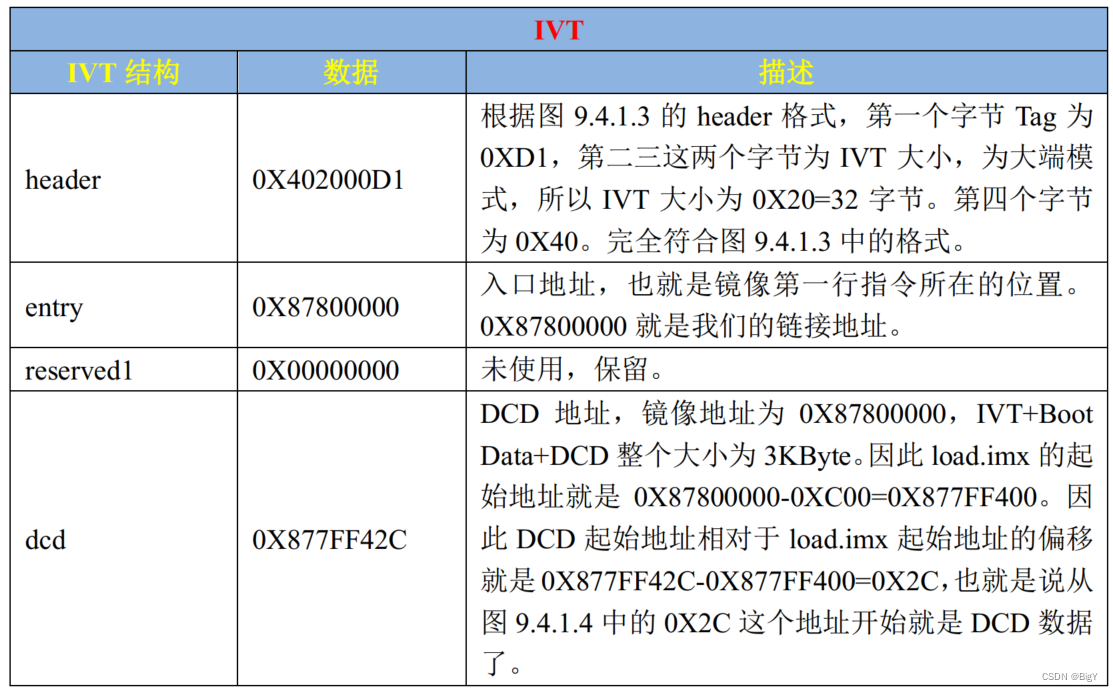

8.7.1 Image Vector Table and Boot Data

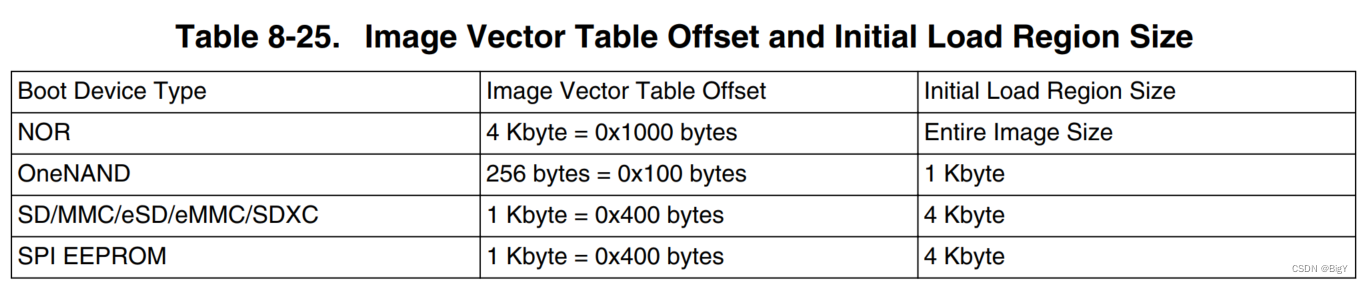

镜像向量表(IVT)是ROM从提供包含必需数据组件的程序镜像的引导设备中读取的数据结构,以执行成功的引导。

IVT包括程序镜像入口点、指向设备配置数据(DCD)的指针以及ROM在引导过程中使用的其他指针。ROM通过连接到芯片的引导设备确定IVT的固定地址。对于每种引导设备类型,IVT相对于基地址的偏移量和初始加载区域大小在下表中定义。IVT的位置是ROM唯一的固定要求。镜像内存映射的其余部分是灵活的,并由IVT的内容确定。

Figure 8-21. Image Vector Table

8.7.1.1 Image vector table structure

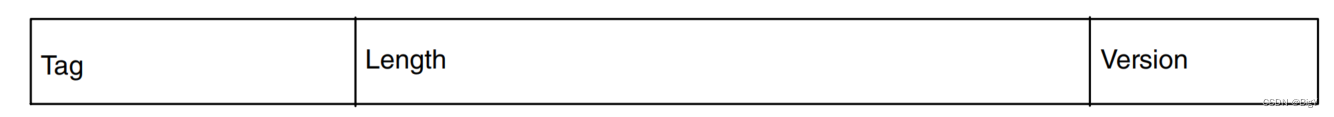

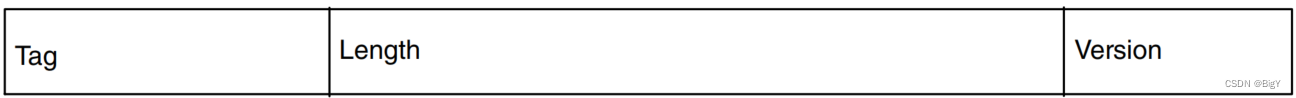

IVT header format

- 标签(Tag):一个设置为0xD1的单字节字段

- 长度(Length):以大端格式表示的两个字节字段,包含IVT的总长度(包括头部)(长度是固定的,必须是32个字节)

- 版本(Version):一个设置为0x40或0x41的单字节字段

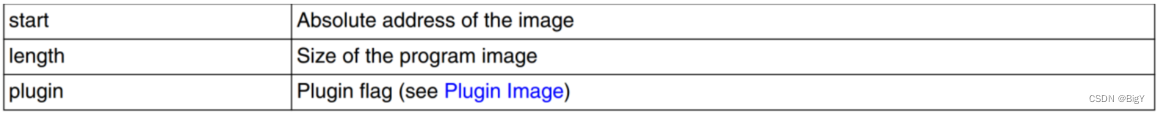

8.7.1.2 Boot data structure

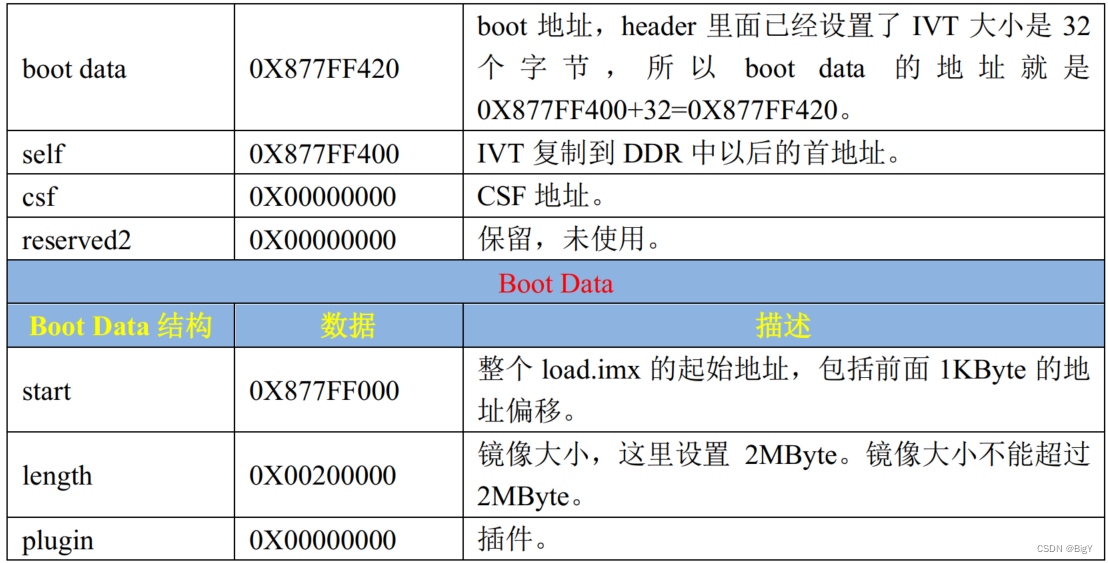

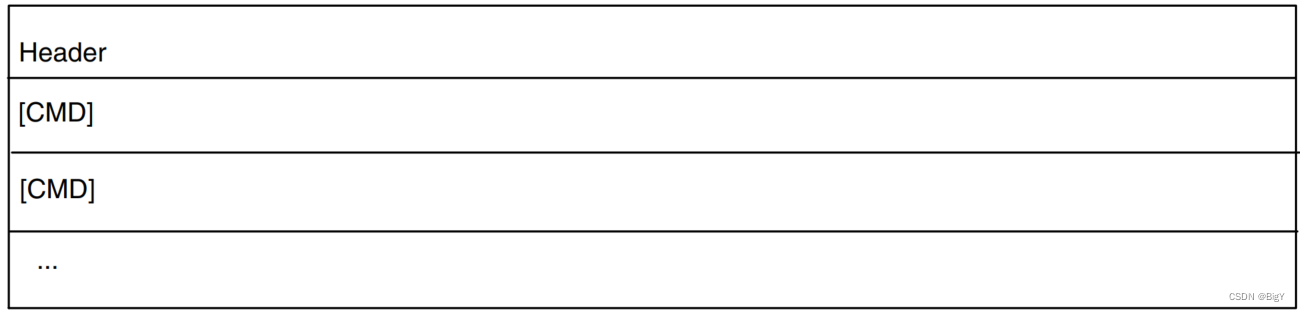

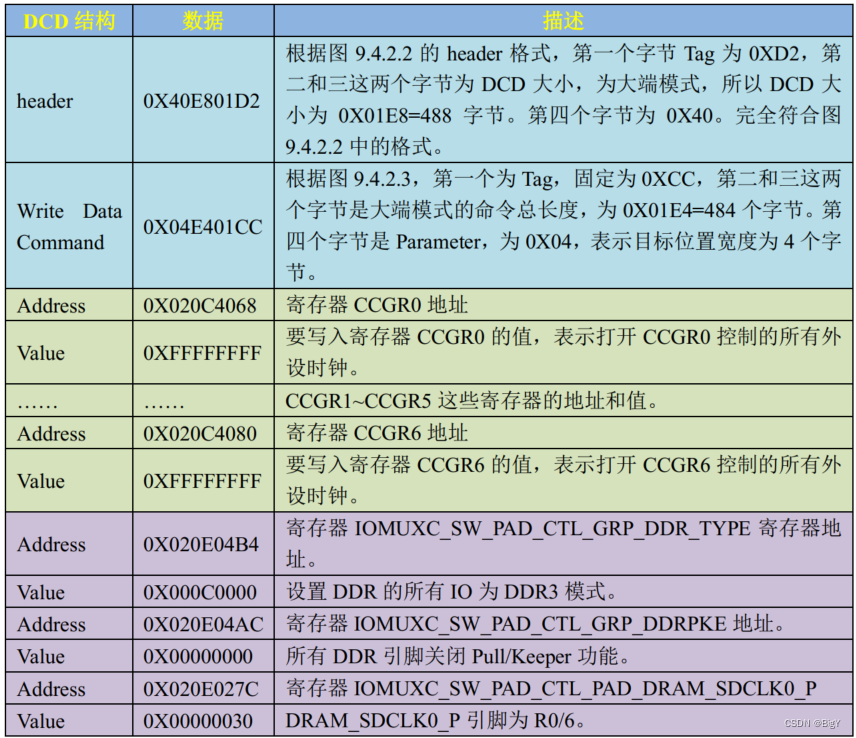

8.7.2 Device Configuration Data (DCD)

在复位时,芯片使用系统中所有外设的默认寄存器值。但是,这些设置通常不是实现最佳系统性能的理想选择,甚至有些外设必须在使用之前进行配置。

DCD是包含在程序镜像(ROM外部)中的配置信息,ROM解释这些信息以配置芯片上的各种外设。例如,EIM的默认设置允许核心在复位后立即与NOR闪存设备进行接口。这使芯片可以与任何NOR闪存设备进行接口,但缺点是性能较慢。此外,某些组件(如DDR)在配置过程中需要一些寄存器编程序列,以使其准备好使用。DCD功能可用于对EIM寄存器和MMDC寄存器进行编程,以获得最佳设置。

ROM根据镜像向量表(IVT)中的信息确定DCD表的位置。有关更多详细信息,请参阅镜像向量表和引导数据。

下面显示的DCD表是一个允许的DCD命令的大端字节数组。DCD的最大大小限制为1768字节。

- 标签(Tag):一个设置为0xD2的单字节字段

- 长度(Length):以大端格式表示的两个字节字段,包含整个DCD(包括头部)的总长度(以字节为单位)

- 版本(Version):一个设置为0x41的单字节字段

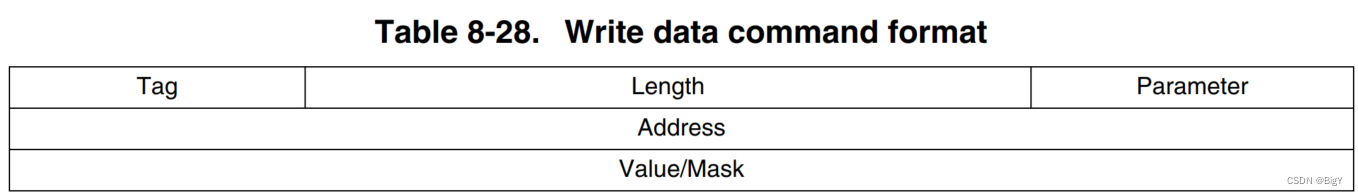

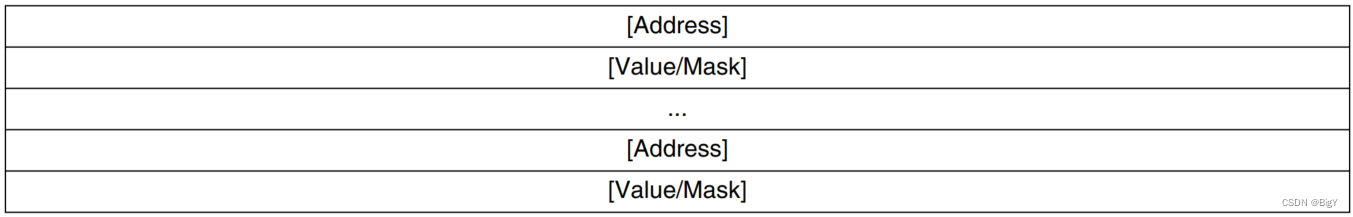

8.7.2.1 Write data command

写入数据命令用于将给定的1、2或4字节值(或位掩码)的列表写入相应的目标地址列表。

写入数据命令的格式(以大端字节数组表示)如下表所示:

- 标签(Tag):一个设置为0xCC的单字节字段

- 长度(Length):以大端格式表示的两个字节字段,包含写入数据命令(包括头部)的长度(以字节为单位)

- 地址(Address):要将数据写入的目标地址

- 数值/掩码(Value/Mask):要写入到前面地址的数据值(或位掩码)

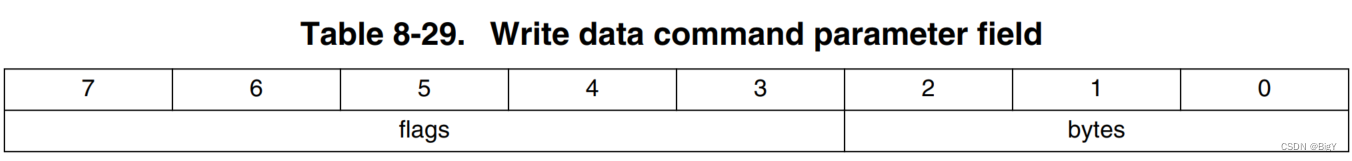

- bytes(字节):目标位置的宽度,以字节为单位(可以是1、2或4)

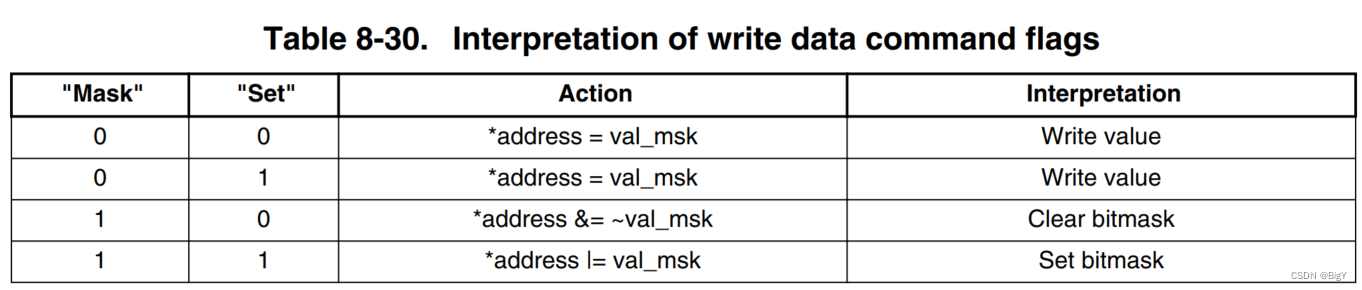

- flags(标志):用于控制命令行为的控制标志

- 数据掩码(Data Mask)= 第3位比特:如果设置,则只有特定位可以在目标地址上进行覆写(否则所有位都可以覆写)

- 数据设置(Data Set)= 第4位比特:如果设置,则目标地址上的位将被此标志覆写(否则将被忽略)

可以指定一个或多个目标地址和值/位掩码对。相同的字节和标志参数适用于命令中的所有位置。

成功时,此命令将根据如下标志写入到每个目标地址:

- 如果Data Mask位被设置,则只有Data Mask指示的位置会被更改,其余位置不受影响。

- 如果Data Set位被设置,则Data Set指示的位将被写入目标地址,其余位置不受影响。

- 如果Data Mask和Data Set都未被设置,则所有位都将被写入目标地址。

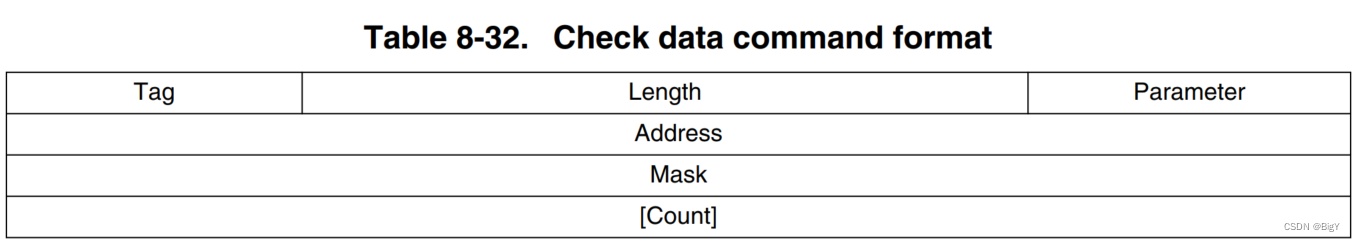

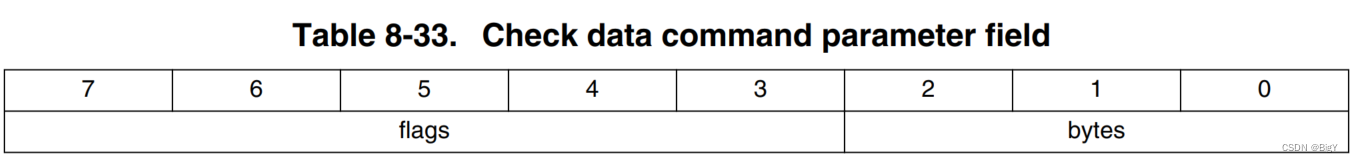

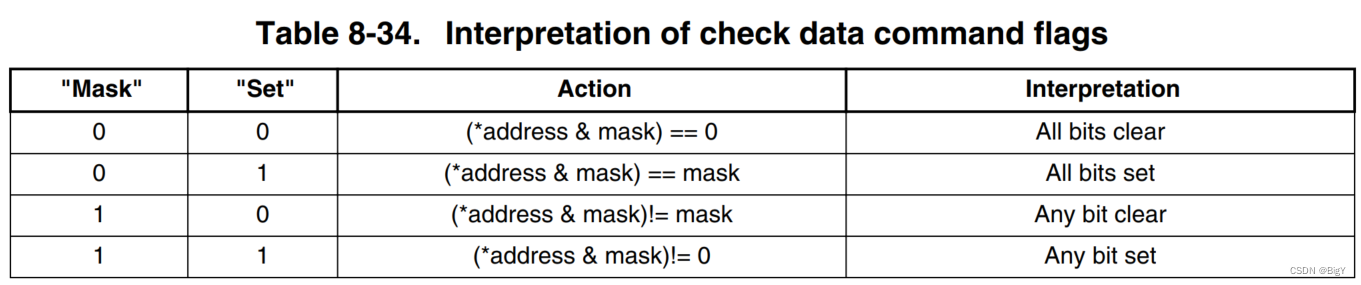

8.7.2.2 Check data command

检查数据命令用于从源地址测试给定的1、2或4字节位掩码。

检查数据命令是一个以大端格式表示的字节数组,其格式如下表所示:

- 标签(Tag):一个设置为0xCF的单字节字段

- 长度(Length):以大端格式表示的两个字节字段,包含检查数据命令(包括头部)的长度(以字节为单位)

- 地址(Address):要测试的源地址

- 掩码(Mask):要测试的位掩码

- 计数(Count):可选的轮询计数;如果未指定计数,则此命令会无限期轮询,直到满足退出条件为止。如果count = 0,则此命令的行为类似于NOP。

- 字节(bytes):目标位置的宽度,以字节为单位(可以是1、2或4)

- 标志(flags):用于控制命令行为的控制标志

- 数据掩码(Data Mask)= 第3位比特:如果设置,则只有特定位可以在目标地址上进行覆写(否则所有位都可以覆写)

- 数据设置(Data Set)= 第4位比特:如果设置,则目标地址上的位将被此标志覆写(否则将被忽略)

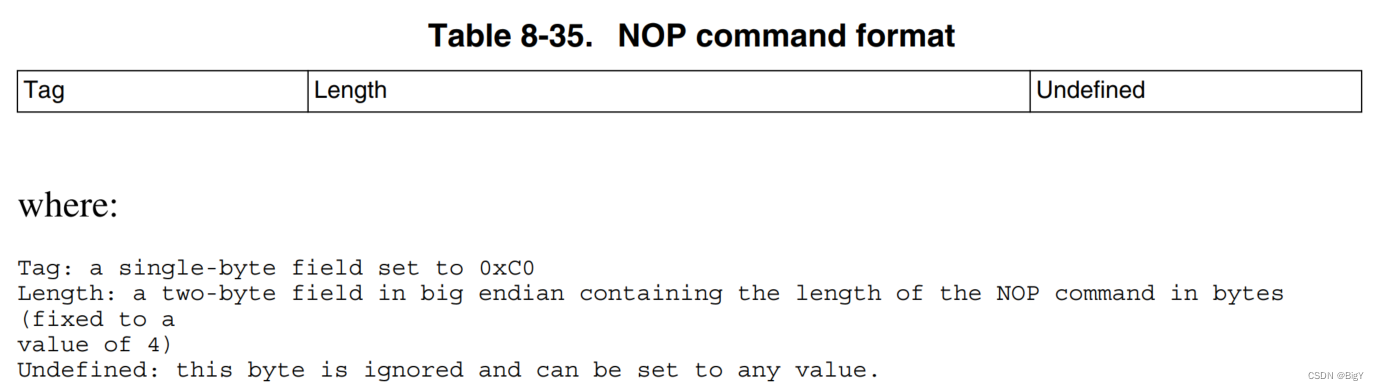

8.7.2.3 NOP command

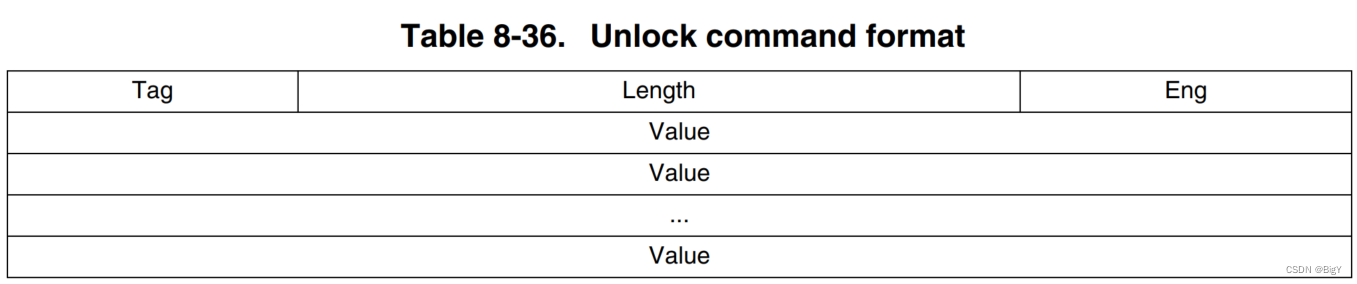

8.7.2.4 Unlock command

解锁命令用于在退出ROM时防止特定的引擎功能被锁定。

解锁命令的格式(以大端式表示)如下表所示:

- 标签(Tag):一个设置为0xB2的单字节字段

- Eng:要解锁的引擎

- Values:[可选]引擎需要的解锁值

8.8 Plugin image

ROM支持有限数量的引导设备。当使用其他设备作为引导源(例如以太网、CDROM或USB)时,必须使用支持的引导设备(通常是串行ROM)作为固件,以提供缺失的引导驱动程序。此外,插件可以定制以支持引导驱动程序,在执行设备初始化时更加灵活,例如条件判断、延迟断言或应用自定义设置到引导设备和内存系统。

除了标准镜像外,芯片还支持插件镜像。插件镜像将执行返回到ROM,而标准镜像则不会。

引导ROM使用引导数据结构的插件标志来检测镜像类型(请参阅引导数据结构)。如果插件标志为1,则ROM将使用镜像作为插件函数。该函数必须初始化引导设备并将程序镜像复制到最终位置。最后,插件函数必须以程序镜像参数返回(有关引导流程的详细信息,请参见高级引导序列)。

在运行插件函数之前,引导ROM对插件镜像进行身份验证,然后对程序镜像进行身份验证。

插件函数必须遵循以下API描述:

typedef BOOLEAN (*plugin_download_f)(void **start, size_t *bytes, UINT32 *ivt_offset);

传递的参数:

- start:退出时的镜像加载地址。

- bytes:退出时的镜像大小。

- ivt_offset:退出时IVT(中断向量表)相对于镜像起始地址的偏移量(以字节为单位)。

RETURN VALUE: - 1 - success

- 0 - failure

串行下载器提供了通过USB和UART串行连接将程序镜像下载到芯片的方式。

8.9 Serial Downloader

在这种模式下,ROM会根据熔丝的WDOG Time-out Select设置(详见熔丝图)将WDOG1编程为指定的超时时间,如果WDOG_ENABLE eFuse为1,并且持续轮询USB和UART连接。如果在USB OTG1和UART 1/2上没有检测到任何活动,并且看门狗定时器超时,Arm核心将被复位。

8.9.1 USB

USB支持由USBOH3USBO2(USB OTG1 USB OTG核控制器,符合USB 2.0规范)和USBPHY(HS USB收发器)组成。

ROM支持用于引导目的的USB OTG端口。芯片上的其他USB端口不支持引导目的。

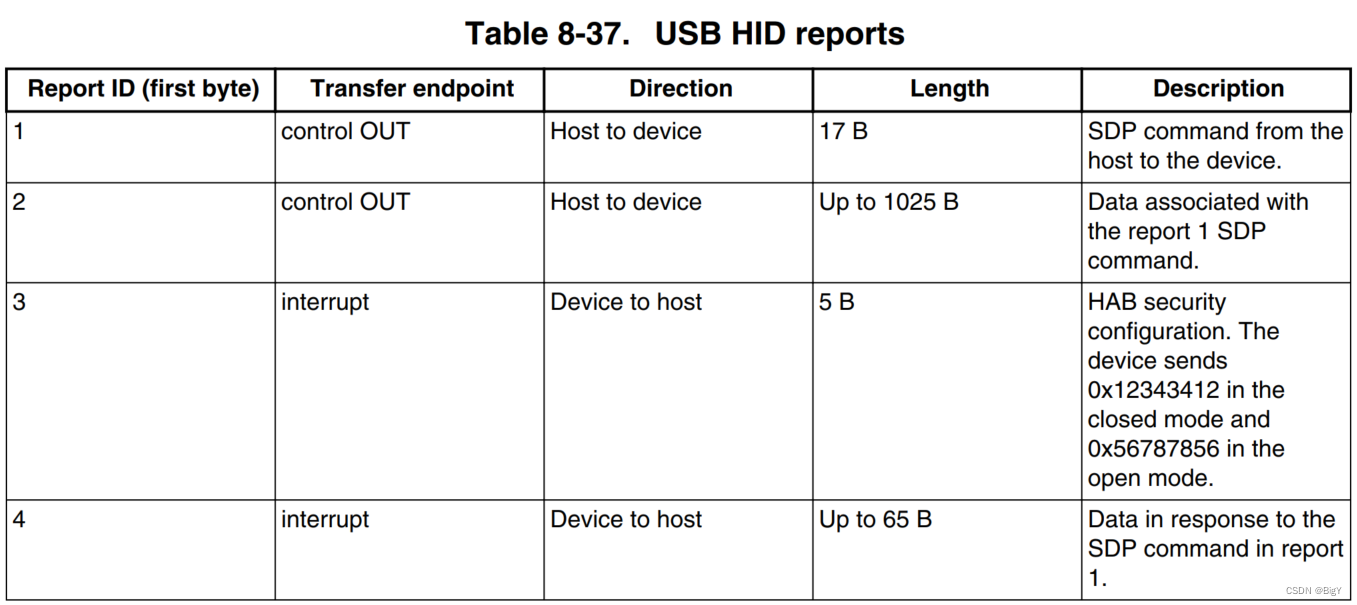

USB驱动程序实现为USB HID类。使用四个HID报告集合来实现SDP协议进行数据传输,如表8-37所述。

8.9.1.1 USB configuration details

USB OTG功能设备驱动程序支持高速(UTMI的HS)非流模式,最大数据包大小为512字节,并提供低级别的USB OTG功能。

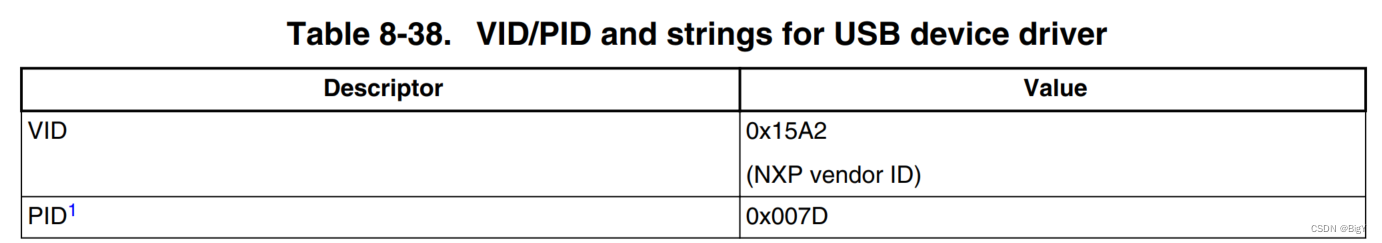

USB设备驱动程序的VID/PID和字符串列在下表中。

8.9.1.2 IOMUX configuration for USB

UTMI PHY的接口信号不在IOMUX中进行配置。UTMI PHY接口使用芯片上的专用引脚。请查看芯片的数据手册获取详细信息。

8.9.2 UART

ROM支持UART1和UART2端口用于引导目的。芯片上的其他UART端口不支持引导目的。

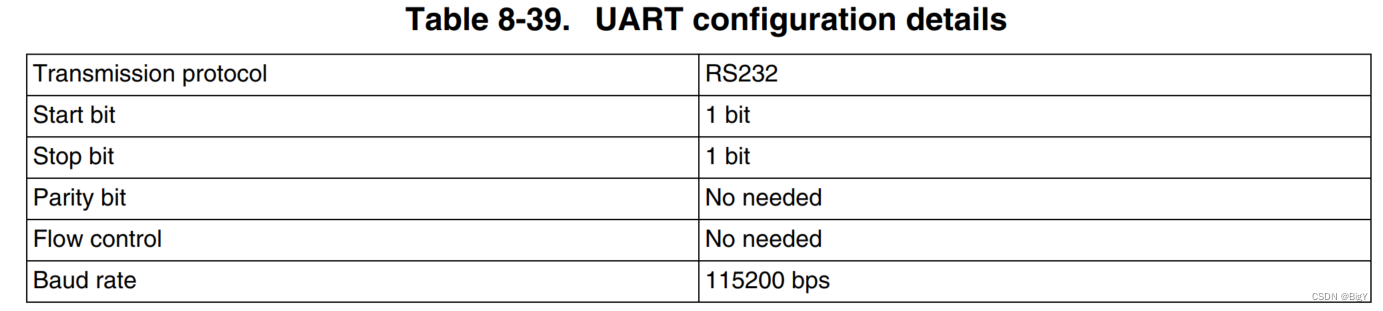

如果检测到UART FIFO中的数据就绪事件,ROM会进入UART串行下载引导模式,并开始从报告数据就绪事件的UART端口读取数据。UART RX数据引脚上的噪声可能会导致UART控制器报告“数据就绪”事件,并进一步导致ROM进入UART串行下载模式。硬件设计人员必须注意避免这种异常情况。

8.9.2.1 UART configuration details

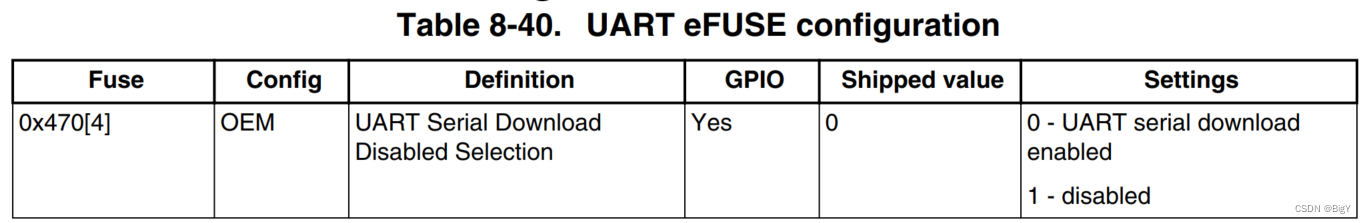

8.9.2.2 UART eFUSE configuration

8.10 Recovery devices

芯片支持恢复设备。如果主引导设备失败,引导ROM会尝试使用ECSPI端口之一从恢复设备引导。

要启用恢复设备,必须设置BOOT_CFG4[6]熔丝。此外,必须根据Serial ROM through SPI中的描述设置串行EEPROM熔丝。

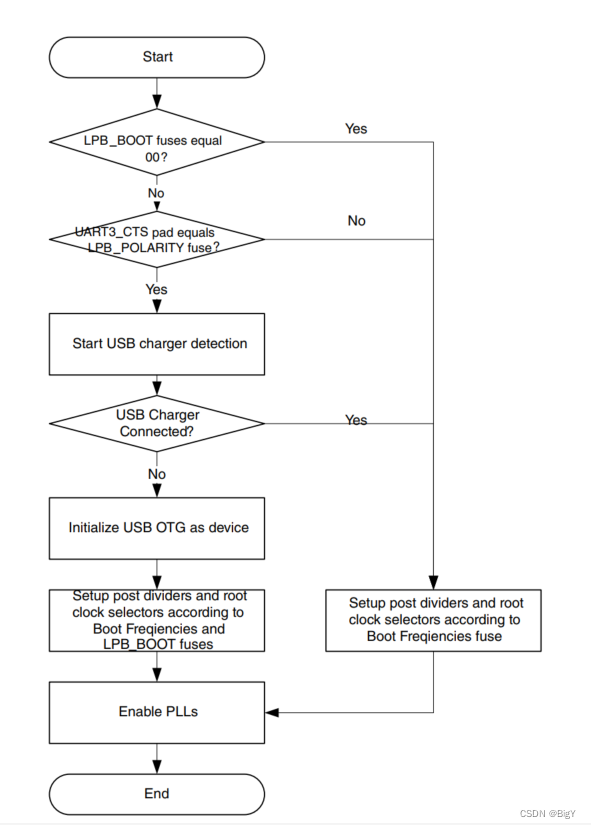

8.11 USB low-power boot

ROM支持USB低功耗引导。此功能使设备能够在连接到USB上游端口时启动和引导,即使设备电池已死或电量不足,无论上游端口是USB充电器还是USB主机/集线器。

如果连接了USB专用充电器或主机/集线器充电器,则设备连接到上游端口后,充电器可以提供稳定电流(最大1.5A)。如果连接了USB主机/集线器,则向设备提供最大100mA的电流,并且设备能够使用少于100mA的电流启动引导映像。

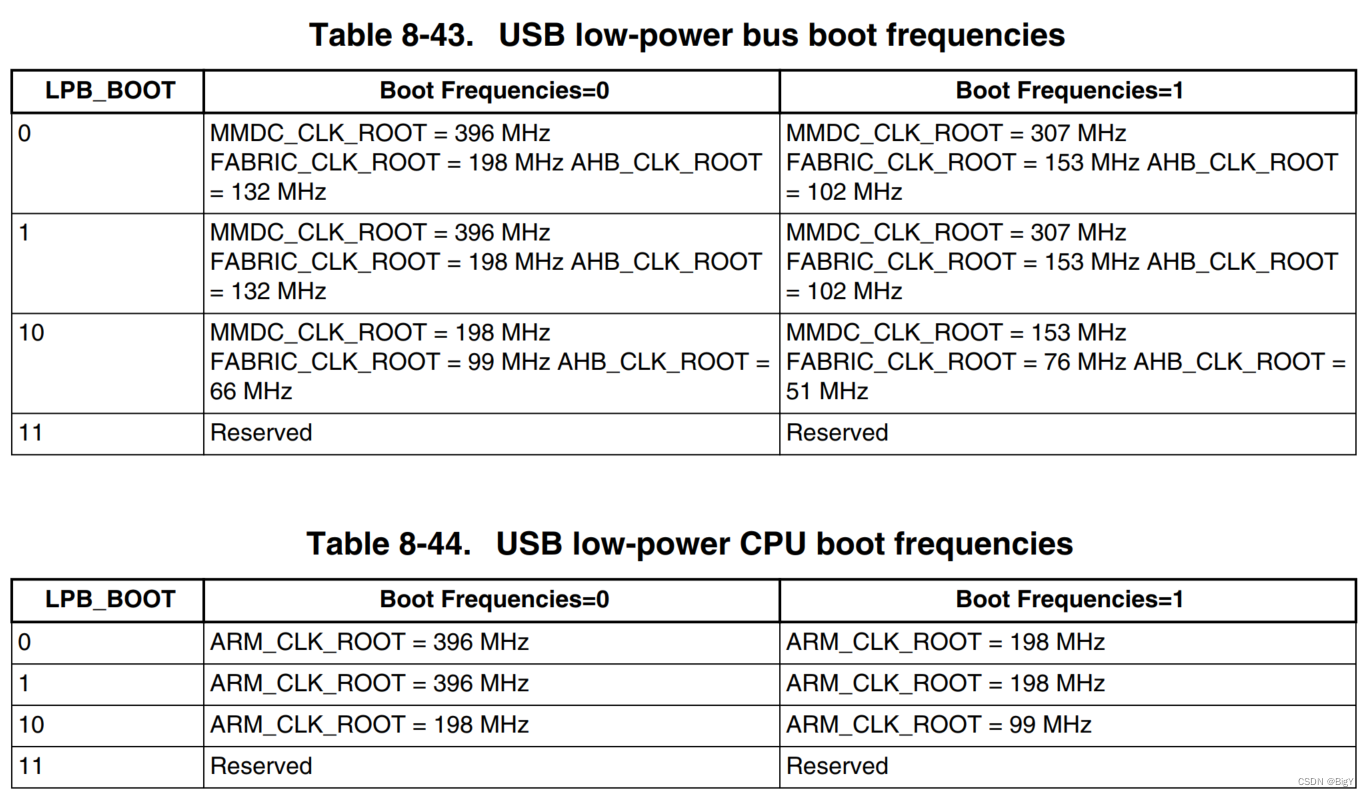

如果吹掉了LPB_BOOT熔丝,则芯片通过UART3_CTS(作为GPIO1_26引脚)检查是否存在低功耗条件。如果存在低功耗引导条件,则激活USB充电器检测。如果没有USB充电器,ROM会将USB初始化为设备,并根据LPB_BOOT熔丝值(参见下表)在Arm、DDR、AXI和AHB根时钟上应用分频因子。UART3_CTS(作为GPIO1_26引脚)上的低功耗引导条件的极性由BT_LPB_POLARITY熔丝设置(如下图所示)。

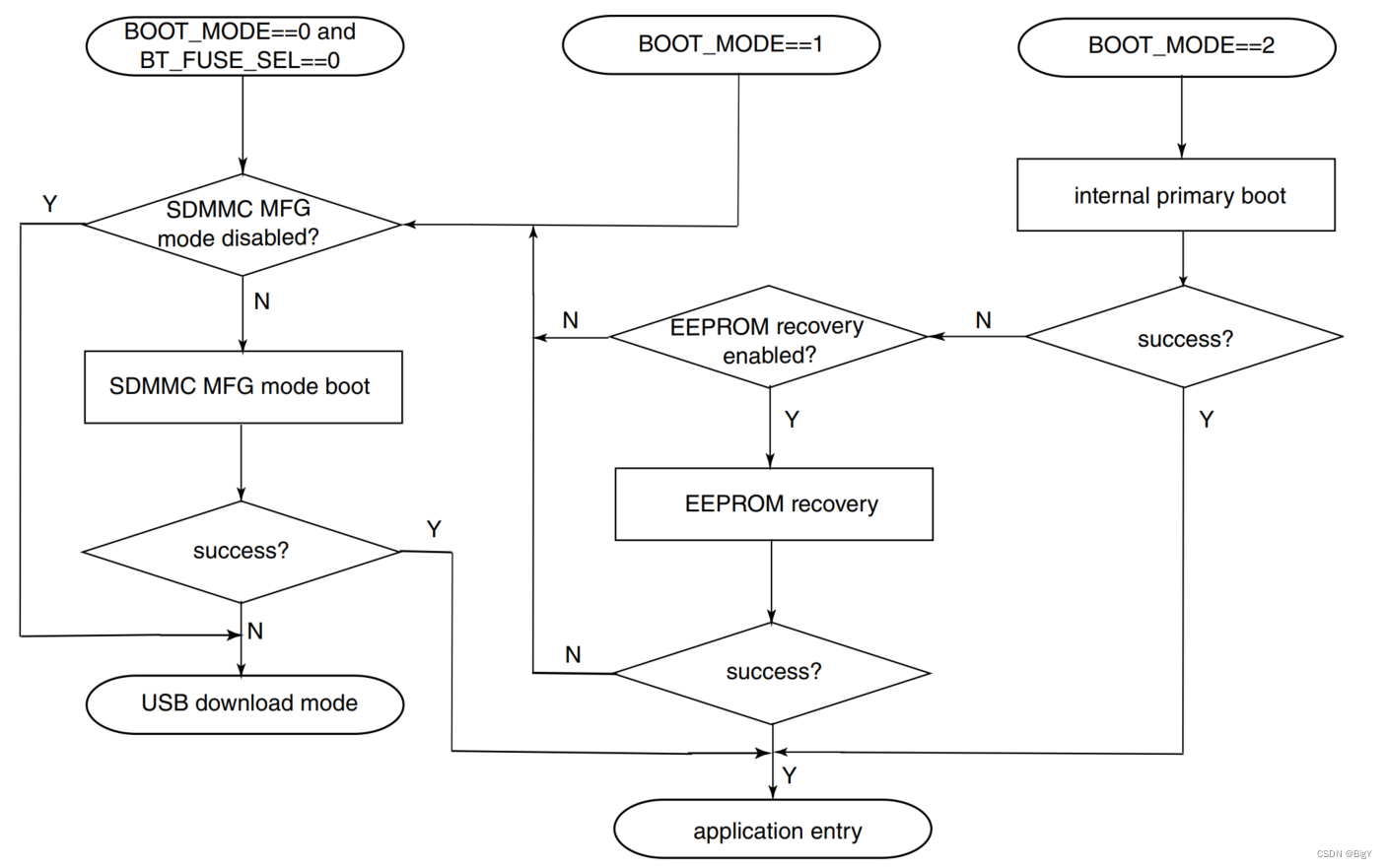

8.12 SD/MMC manufacture mode

当内部引导和恢复引导(如果已启用)失败,并且未设置SDMMC_MFG_DISABLE熔丝位并且设置了EEPROM恢复熔丝位时,引导将进入SD/MMC制造模式,然后才进入串行下载模式。在制造模式下,无论熔丝设置如何,都会使用单位总线宽度。

在制造模式下,将在uSDHC1上扫描SD卡或MMC卡。如果检测到卡并且卡中存在有效的引导映像,则将加载并执行引导映像。SD1_CD引脚用于检测是否插入了卡。

默认情况下,启用了SD/MMC制造模式。吹掉DISABLE_SDMMC_MFG熔丝以禁用它。

本文围绕i.MX 6ULL应用处理器的系统引导展开,介绍了引导过程始于POR,ROM支持多种引导设备和串行下载,具备DCD功能和安全引导特性。还阐述了引导模式、设备配置、初始化等内容,以及不同引导设备的操作流程和相关命令。

本文围绕i.MX 6ULL应用处理器的系统引导展开,介绍了引导过程始于POR,ROM支持多种引导设备和串行下载,具备DCD功能和安全引导特性。还阐述了引导模式、设备配置、初始化等内容,以及不同引导设备的操作流程和相关命令。

6541

6541