http://blog.chinaunix.net/uid-20620288-id-3924448.html

1.独立于介质的接口(MII)

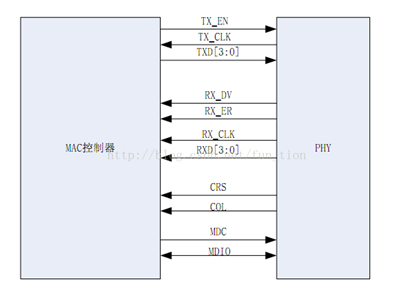

独立于介质的接口(MII)用于MAC与外接的PHY互联,支持10Mbit/s和100Mbit/s数据传输模式。MII的信号线如下图所示:

•MII_TX_CLK:发送数据使用的时钟信号,对于10M位/s的数据传输,此时钟为2.5MHz,对于100M位/s的数据传输,此时钟为25MHz。

•MII_RX_CLK:接收数据使用的时钟信号,对于10M位/s的数据传输,此时钟为2.5MHz,对于100M位/s的数据传输,此时钟为25MHz。

•MII_TX_EN:传输使能信号,此信号必需与数据前导符的起始位同步出现,并在传输完毕前一直保持。

•MII_TXD[3:0]:发送数据线,每次传输4位数据,数据在MII_TX_EN信号有效时有效。MII_TXD[0]是数据的最低位,MII_TXD[3]是最高位。当MII_TX_EN信号无效时,PHY忽略传输的数据。

•MII_CRS:载波侦听信号,仅工作在半双工模式下,由PHY控制,当发送或接收的介质非空闲时,使能此信号。 PHY必需保证MII_CRS信号在发生冲突的整个时间段内都保持有效,不需要此信号与发送/接收的时钟同步。

•MII_COL

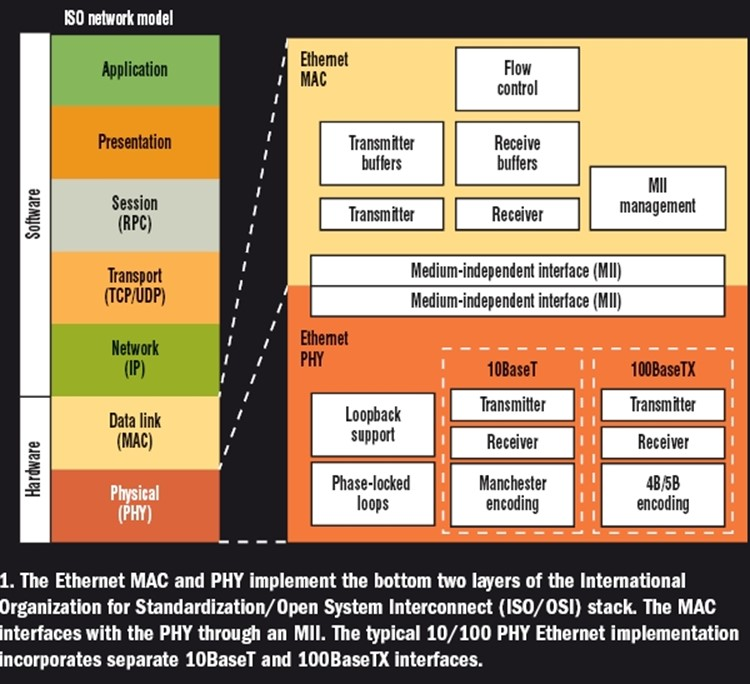

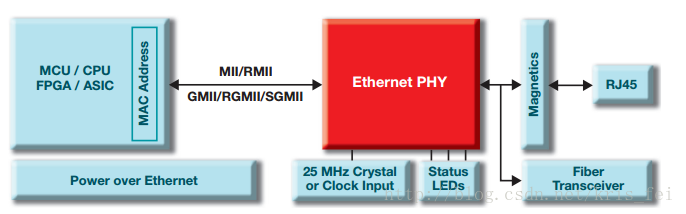

本文详细介绍了独立于介质的接口(MII)、精简的独立于介质的接口(RMII)以及千兆以太网中的GMII和RGMII接口。RMII通过减少信号线来简化硬件设计,而RGMII则进一步减少信号线并提升时钟频率以维持1000Mbps传输速率。此外,文章还提及1000Base-T规范,展示了如何在双绞线上实现全双工千兆传输。

本文详细介绍了独立于介质的接口(MII)、精简的独立于介质的接口(RMII)以及千兆以太网中的GMII和RGMII接口。RMII通过减少信号线来简化硬件设计,而RGMII则进一步减少信号线并提升时钟频率以维持1000Mbps传输速率。此外,文章还提及1000Base-T规范,展示了如何在双绞线上实现全双工千兆传输。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3911

3911

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?