前言:

本系列,将stm32常用片上外设进行整理,包括大致原理和代码,主要是熟悉如何根据手册去编写代码。便于以后需要做实验时,能够快速编写基本的驱动,然后编写应用代码。

本系列基于“标准库”整理,开发板用的是正点原子精英版V1.5,单片机是STM32F103ZET6。开发工具KEIL。主要参考资料有《STM32F103xCDE中文参考手册》《STM32F103xCDE中文数据手册》、《CM3权威指南》、《STM32F103xCDE闪存编程手册》、《精英版原理图V1.5》。

》《STM32F1xx Cortex-M3编程手册-英文版》。

一、NVIC介绍

NVIC是CM3内核的嵌套中断控制系统,即要产生中断,都得经过这个外设,这个外设是CM3内带的,所以只要是以CM3为内核的单片机都是有的。芯片生产厂商在此基础上进行删减。

由于这个NVIC是CM3自带的,而ST公司在其基础上进行删减,所以关于NVIC的手册就有2份,一份是ARM公司写的《CM3权威指南》,一份是ST公司写的《STM32F1xx Cortex-M3编程手册-英文版》。

在《CM3权威指南》的7、8、9节有NVIC最完整的介绍,如下图所示。

在《STM32F1xx Cortex-M3编程手册-英文版》的4.3和4.4有关于ST的NVIC和SCB的详细介绍。

1.中断服务函数

CM3的NVIC支持16个内部中断和240个外部中断,STM32F1系列支持16个内部中断和60个外部中断。STM32F1支持的中断可在startup_stm32f10x_hd.s启动文件中查看,因为这里面定义了所支持的76个中断的中断服务函数。如下图所示。

; Vector Table Mapped to Address 0 at Reset

AREA RESET, DATA, READONLY

EXPORT __Vectors

EXPORT __Vectors_End

EXPORT __Vectors_Size

__Vectors DCD __initial_sp ; Top of Stack

DCD Reset_Handler ; Reset Handler

DCD NMI_Handler ; NMI Handler

DCD HardFault_Handler ; Hard Fault Handler

DCD MemManage_Handler ; MPU Fault Handler

DCD BusFault_Handler ; Bus Fault Handler

DCD UsageFault_Handler ; Usage Fault Handler

DCD 0 ; Reserved

DCD 0 ; Reserved

DCD 0 ; Reserved

DCD 0 ; Reserved

DCD SVC_Handler ; SVCall Handler

DCD DebugMon_Handler ; Debug Monitor Handler

DCD 0 ; Reserved

DCD PendSV_Handler ; PendSV Handler

DCD SysTick_Handler ; SysTick Handler

; External Interrupts

DCD WWDG_IRQHandler ; Window Watchdog

DCD PVD_IRQHandler ; PVD through EXTI Line detect

DCD TAMPER_IRQHandler ; Tamper

DCD RTC_IRQHandler ; RTC

DCD FLASH_IRQHandler ; Flash

DCD RCC_IRQHandler ; RCC

DCD EXTI0_IRQHandler ; EXTI Line 0

DCD EXTI1_IRQHandler ; EXTI Line 1

DCD EXTI2_IRQHandler ; EXTI Line 2

DCD EXTI3_IRQHandler ; EXTI Line 3

DCD EXTI4_IRQHandler ; EXTI Line 4

DCD DMA1_Channel1_IRQHandler ; DMA1 Channel 1

DCD DMA1_Channel2_IRQHandler ; DMA1 Channel 2

DCD DMA1_Channel3_IRQHandler ; DMA1 Channel 3

DCD DMA1_Channel4_IRQHandler ; DMA1 Channel 4

DCD DMA1_Channel5_IRQHandler ; DMA1 Channel 5

DCD DMA1_Channel6_IRQHandler ; DMA1 Channel 6

DCD DMA1_Channel7_IRQHandler ; DMA1 Channel 7

DCD ADC1_2_IRQHandler ; ADC1 & ADC2

DCD USB_HP_CAN1_TX_IRQHandler ; USB High Priority or CAN1 TX

DCD USB_LP_CAN1_RX0_IRQHandler ; USB Low Priority or CAN1 RX0

DCD CAN1_RX1_IRQHandler ; CAN1 RX1

DCD CAN1_SCE_IRQHandler ; CAN1 SCE

DCD EXTI9_5_IRQHandler ; EXTI Line 9..5

DCD TIM1_BRK_IRQHandler ; TIM1 Break

DCD TIM1_UP_IRQHandler ; TIM1 Update

DCD TIM1_TRG_COM_IRQHandler ; TIM1 Trigger and Commutation

DCD TIM1_CC_IRQHandler ; TIM1 Capture Compare

DCD TIM2_IRQHandler ; TIM2

DCD TIM3_IRQHandler ; TIM3

DCD TIM4_IRQHandler ; TIM4

DCD I2C1_EV_IRQHandler ; I2C1 Event

DCD I2C1_ER_IRQHandler ; I2C1 Error

DCD I2C2_EV_IRQHandler ; I2C2 Event

DCD I2C2_ER_IRQHandler ; I2C2 Error

DCD SPI1_IRQHandler ; SPI1

DCD SPI2_IRQHandler ; SPI2

DCD USART1_IRQHandler ; USART1

DCD USART2_IRQHandler ; USART2

DCD USART3_IRQHandler ; USART3

DCD EXTI15_10_IRQHandler ; EXTI Line 15..10

DCD RTCAlarm_IRQHandler ; RTC Alarm through EXTI Line

DCD USBWakeUp_IRQHandler ; USB Wakeup from suspend

DCD TIM8_BRK_IRQHandler ; TIM8 Break

DCD TIM8_UP_IRQHandler ; TIM8 Update

DCD TIM8_TRG_COM_IRQHandler ; TIM8 Trigger and Commutation

DCD TIM8_CC_IRQHandler ; TIM8 Capture Compare

DCD ADC3_IRQHandler ; ADC3

DCD FSMC_IRQHandler ; FSMC

DCD SDIO_IRQHandler ; SDIO

DCD TIM5_IRQHandler ; TIM5

DCD SPI3_IRQHandler ; SPI3

DCD UART4_IRQHandler ; UART4

DCD UART5_IRQHandler ; UART5

DCD TIM6_IRQHandler ; TIM6

DCD TIM7_IRQHandler ; TIM7

DCD DMA2_Channel1_IRQHandler ; DMA2 Channel1

DCD DMA2_Channel2_IRQHandler ; DMA2 Channel2

DCD DMA2_Channel3_IRQHandler ; DMA2 Channel3

DCD DMA2_Channel4_5_IRQHandler ; DMA2 Channel4 & Channel52.中断号

所对应的中断号在stm32f19x.h文件中的IRQn_Type这个类型中,如下图所示,与中断服务函数一一对应。

/**

* @brief STM32F10x Interrupt Number Definition, according to the selected device

* in @ref Library_configuration_section

*/

typedef enum IRQn

{

/****** Cortex-M3 Processor Exceptions Numbers ***************************************************/

NonMaskableInt_IRQn = -14, /*!< 2 Non Maskable Interrupt */

MemoryManagement_IRQn = -12, /*!< 4 Cortex-M3 Memory Management Interrupt */

BusFault_IRQn = -11, /*!< 5 Cortex-M3 Bus Fault Interrupt */

UsageFault_IRQn = -10, /*!< 6 Cortex-M3 Usage Fault Interrupt */

SVCall_IRQn = -5, /*!< 11 Cortex-M3 SV Call Interrupt */

DebugMonitor_IRQn = -4, /*!< 12 Cortex-M3 Debug Monitor Interrupt */

PendSV_IRQn = -2, /*!< 14 Cortex-M3 Pend SV Interrupt */

SysTick_IRQn = -1, /*!< 15 Cortex-M3 System Tick Interrupt */

/****** STM32 specific Interrupt Numbers *********************************************************/

WWDG_IRQn = 0, /*!< Window WatchDog Interrupt */

PVD_IRQn = 1, /*!< PVD through EXTI Line detection Interrupt */

TAMPER_IRQn = 2, /*!< Tamper Interrupt */

RTC_IRQn = 3, /*!< RTC global Interrupt */

FLASH_IRQn = 4, /*!< FLASH global Interrupt */

RCC_IRQn = 5, /*!< RCC global Interrupt */

EXTI0_IRQn = 6, /*!< EXTI Line0 Interrupt */

EXTI1_IRQn = 7, /*!< EXTI Line1 Interrupt */

EXTI2_IRQn = 8, /*!< EXTI Line2 Interrupt */

EXTI3_IRQn = 9, /*!< EXTI Line3 Interrupt */

EXTI4_IRQn = 10, /*!< EXTI Line4 Interrupt */

DMA1_Channel1_IRQn = 11, /*!< DMA1 Channel 1 global Interrupt */

DMA1_Channel2_IRQn = 12, /*!< DMA1 Channel 2 global Interrupt */

DMA1_Channel3_IRQn = 13, /*!< DMA1 Channel 3 global Interrupt */

DMA1_Channel4_IRQn = 14, /*!< DMA1 Channel 4 global Interrupt */

DMA1_Channel5_IRQn = 15, /*!< DMA1 Channel 5 global Interrupt */

DMA1_Channel6_IRQn = 16, /*!< DMA1 Channel 6 global Interrupt */

DMA1_Channel7_IRQn = 17, /*!< DMA1 Channel 7 global Interrupt */

#ifdef STM32F10X_LD

ADC1_2_IRQn = 18, /*!< ADC1 and ADC2 global Interrupt */

USB_HP_CAN1_TX_IRQn = 19, /*!< USB Device High Priority or CAN1 TX Interrupts */

USB_LP_CAN1_RX0_IRQn = 20, /*!< USB Device Low Priority or CAN1 RX0 Interrupts */

CAN1_RX1_IRQn = 21, /*!< CAN1 RX1 Interrupt */

CAN1_SCE_IRQn = 22, /*!< CAN1 SCE Interrupt */

EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

TIM1_BRK_IRQn = 24, /*!< TIM1 Break Interrupt */

TIM1_UP_IRQn = 25, /*!< TIM1 Update Interrupt */

TIM1_TRG_COM_IRQn = 26, /*!< TIM1 Trigger and Commutation Interrupt */

TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

USART1_IRQn = 37, /*!< USART1 global Interrupt */

USART2_IRQn = 38, /*!< USART2 global Interrupt */

EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = 41, /*!< RTC Alarm through EXTI Line Interrupt */

USBWakeUp_IRQn = 42 /*!< USB Device WakeUp from suspend through EXTI Line Interrupt */

#endif /* STM32F10X_LD */

#ifdef STM32F10X_LD_VL

ADC1_IRQn = 18, /*!< ADC1 global Interrupt */

EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

TIM1_BRK_TIM15_IRQn = 24, /*!< TIM1 Break and TIM15 Interrupts */

TIM1_UP_TIM16_IRQn = 25, /*!< TIM1 Update and TIM16 Interrupts */

TIM1_TRG_COM_TIM17_IRQn = 26, /*!< TIM1 Trigger and Commutation and TIM17 Interrupt */

TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

USART1_IRQn = 37, /*!< USART1 global Interrupt */

USART2_IRQn = 38, /*!< USART2 global Interrupt */

EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = 41, /*!< RTC Alarm through EXTI Line Interrupt */

CEC_IRQn = 42, /*!< HDMI-CEC Interrupt */

TIM6_DAC_IRQn = 54, /*!< TIM6 and DAC underrun Interrupt */

TIM7_IRQn = 55 /*!< TIM7 Interrupt */

#endif /* STM32F10X_LD_VL */

#ifdef STM32F10X_MD

ADC1_2_IRQn = 18, /*!< ADC1 and ADC2 global Interrupt */

USB_HP_CAN1_TX_IRQn = 19, /*!< USB Device High Priority or CAN1 TX Interrupts */

USB_LP_CAN1_RX0_IRQn = 20, /*!< USB Device Low Priority or CAN1 RX0 Interrupts */

CAN1_RX1_IRQn = 21, /*!< CAN1 RX1 Interrupt */

CAN1_SCE_IRQn = 22, /*!< CAN1 SCE Interrupt */

EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

TIM1_BRK_IRQn = 24, /*!< TIM1 Break Interrupt */

TIM1_UP_IRQn = 25, /*!< TIM1 Update Interrupt */

TIM1_TRG_COM_IRQn = 26, /*!< TIM1 Trigger and Commutation Interrupt */

TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

TIM4_IRQn = 30, /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = 33, /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = 34, /*!< I2C2 Error Interrupt */

SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

SPI2_IRQn = 36, /*!< SPI2 global Interrupt */

USART1_IRQn = 37, /*!< USART1 global Interrupt */

USART2_IRQn = 38, /*!< USART2 global Interrupt */

USART3_IRQn = 39, /*!< USART3 global Interrupt */

EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = 41, /*!< RTC Alarm through EXTI Line Interrupt */

USBWakeUp_IRQn = 42 /*!< USB Device WakeUp from suspend through EXTI Line Interrupt */

#endif /* STM32F10X_MD */

#ifdef STM32F10X_MD_VL

ADC1_IRQn = 18, /*!< ADC1 global Interrupt */

EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

TIM1_BRK_TIM15_IRQn = 24, /*!< TIM1 Break and TIM15 Interrupts */

TIM1_UP_TIM16_IRQn = 25, /*!< TIM1 Update and TIM16 Interrupts */

TIM1_TRG_COM_TIM17_IRQn = 26, /*!< TIM1 Trigger and Commutation and TIM17 Interrupt */

TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

TIM4_IRQn = 30, /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = 33, /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = 34, /*!< I2C2 Error Interrupt */

SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

SPI2_IRQn = 36, /*!< SPI2 global Interrupt */

USART1_IRQn = 37, /*!< USART1 global Interrupt */

USART2_IRQn = 38, /*!< USART2 global Interrupt */

USART3_IRQn = 39, /*!< USART3 global Interrupt */

EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = 41, /*!< RTC Alarm through EXTI Line Interrupt */

CEC_IRQn = 42, /*!< HDMI-CEC Interrupt */

TIM6_DAC_IRQn = 54, /*!< TIM6 and DAC underrun Interrupt */

TIM7_IRQn = 55 /*!< TIM7 Interrupt */

#endif /* STM32F10X_MD_VL */

#ifdef STM32F10X_HD

ADC1_2_IRQn = 18, /*!< ADC1 and ADC2 global Interrupt */

USB_HP_CAN1_TX_IRQn = 19, /*!< USB Device High Priority or CAN1 TX Interrupts */

USB_LP_CAN1_RX0_IRQn = 20, /*!< USB Device Low Priority or CAN1 RX0 Interrupts */

CAN1_RX1_IRQn = 21, /*!< CAN1 RX1 Interrupt */

CAN1_SCE_IRQn = 22, /*!< CAN1 SCE Interrupt */

EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

TIM1_BRK_IRQn = 24, /*!< TIM1 Break Interrupt */

TIM1_UP_IRQn = 25, /*!< TIM1 Update Interrupt */

TIM1_TRG_COM_IRQn = 26, /*!< TIM1 Trigger and Commutation Interrupt */

TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

TIM4_IRQn = 30, /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = 33, /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = 34, /*!< I2C2 Error Interrupt */

SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

SPI2_IRQn = 36, /*!< SPI2 global Interrupt */

USART1_IRQn = 37, /*!< USART1 global Interrupt */

USART2_IRQn = 38, /*!< USART2 global Interrupt */

USART3_IRQn = 39, /*!< USART3 global Interrupt */

EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = 41, /*!< RTC Alarm through EXTI Line Interrupt */

USBWakeUp_IRQn = 42, /*!< USB Device WakeUp from suspend through EXTI Line Interrupt */

TIM8_BRK_IRQn = 43, /*!< TIM8 Break Interrupt */

TIM8_UP_IRQn = 44, /*!< TIM8 Update Interrupt */

TIM8_TRG_COM_IRQn = 45, /*!< TIM8 Trigger and Commutation Interrupt */

TIM8_CC_IRQn = 46, /*!< TIM8 Capture Compare Interrupt */

ADC3_IRQn = 47, /*!< ADC3 global Interrupt */

FSMC_IRQn = 48, /*!< FSMC global Interrupt */

SDIO_IRQn = 49, /*!< SDIO global Interrupt */

TIM5_IRQn = 50, /*!< TIM5 global Interrupt */

SPI3_IRQn = 51, /*!< SPI3 global Interrupt */

UART4_IRQn = 52, /*!< UART4 global Interrupt */

UART5_IRQn = 53, /*!< UART5 global Interrupt */

TIM6_IRQn = 54, /*!< TIM6 global Interrupt */

TIM7_IRQn = 55, /*!< TIM7 global Interrupt */

DMA2_Channel1_IRQn = 56, /*!< DMA2 Channel 1 global Interrupt */

DMA2_Channel2_IRQn = 57, /*!< DMA2 Channel 2 global Interrupt */

DMA2_Channel3_IRQn = 58, /*!< DMA2 Channel 3 global Interrupt */

DMA2_Channel4_5_IRQn = 59 /*!< DMA2 Channel 4 and Channel 5 global Interrupt */

#endif /* STM32F10X_HD */

#ifdef STM32F10X_HD_VL

ADC1_IRQn = 18, /*!< ADC1 global Interrupt */

EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

TIM1_BRK_TIM15_IRQn = 24, /*!< TIM1 Break and TIM15 Interrupts */

TIM1_UP_TIM16_IRQn = 25, /*!< TIM1 Update and TIM16 Interrupts */

TIM1_TRG_COM_TIM17_IRQn = 26, /*!< TIM1 Trigger and Commutation and TIM17 Interrupt */

TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

TIM4_IRQn = 30, /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = 33, /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = 34, /*!< I2C2 Error Interrupt */

SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

SPI2_IRQn = 36, /*!< SPI2 global Interrupt */

USART1_IRQn = 37, /*!< USART1 global Interrupt */

USART2_IRQn = 38, /*!< USART2 global Interrupt */

USART3_IRQn = 39, /*!< USART3 global Interrupt */

EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = 41, /*!< RTC Alarm through EXTI Line Interrupt */

CEC_IRQn = 42, /*!< HDMI-CEC Interrupt */

TIM12_IRQn = 43, /*!< TIM12 global Interrupt */

TIM13_IRQn = 44, /*!< TIM13 global Interrupt */

TIM14_IRQn = 45, /*!< TIM14 global Interrupt */

TIM5_IRQn = 50, /*!< TIM5 global Interrupt */

SPI3_IRQn = 51, /*!< SPI3 global Interrupt */

UART4_IRQn = 52, /*!< UART4 global Interrupt */

UART5_IRQn = 53, /*!< UART5 global Interrupt */

TIM6_DAC_IRQn = 54, /*!< TIM6 and DAC underrun Interrupt */

TIM7_IRQn = 55, /*!< TIM7 Interrupt */

DMA2_Channel1_IRQn = 56, /*!< DMA2 Channel 1 global Interrupt */

DMA2_Channel2_IRQn = 57, /*!< DMA2 Channel 2 global Interrupt */

DMA2_Channel3_IRQn = 58, /*!< DMA2 Channel 3 global Interrupt */

DMA2_Channel4_5_IRQn = 59, /*!< DMA2 Channel 4 and Channel 5 global Interrupt */

DMA2_Channel5_IRQn = 60 /*!< DMA2 Channel 5 global Interrupt (DMA2 Channel 5 is

mapped at position 60 only if the MISC_REMAP bit in

the AFIO_MAPR2 register is set) */

#endif /* STM32F10X_HD_VL */

#ifdef STM32F10X_XL

ADC1_2_IRQn = 18, /*!< ADC1 and ADC2 global Interrupt */

USB_HP_CAN1_TX_IRQn = 19, /*!< USB Device High Priority or CAN1 TX Interrupts */

USB_LP_CAN1_RX0_IRQn = 20, /*!< USB Device Low Priority or CAN1 RX0 Interrupts */

CAN1_RX1_IRQn = 21, /*!< CAN1 RX1 Interrupt */

CAN1_SCE_IRQn = 22, /*!< CAN1 SCE Interrupt */

EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

TIM1_BRK_TIM9_IRQn = 24, /*!< TIM1 Break Interrupt and TIM9 global Interrupt */

TIM1_UP_TIM10_IRQn = 25, /*!< TIM1 Update Interrupt and TIM10 global Interrupt */

TIM1_TRG_COM_TIM11_IRQn = 26, /*!< TIM1 Trigger and Commutation Interrupt and TIM11 global interrupt */

TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

TIM4_IRQn = 30, /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = 33, /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = 34, /*!< I2C2 Error Interrupt */

SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

SPI2_IRQn = 36, /*!< SPI2 global Interrupt */

USART1_IRQn = 37, /*!< USART1 global Interrupt */

USART2_IRQn = 38, /*!< USART2 global Interrupt */

USART3_IRQn = 39, /*!< USART3 global Interrupt */

EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = 41, /*!< RTC Alarm through EXTI Line Interrupt */

USBWakeUp_IRQn = 42, /*!< USB Device WakeUp from suspend through EXTI Line Interrupt */

TIM8_BRK_TIM12_IRQn = 43, /*!< TIM8 Break Interrupt and TIM12 global Interrupt */

TIM8_UP_TIM13_IRQn = 44, /*!< TIM8 Update Interrupt and TIM13 global Interrupt */

TIM8_TRG_COM_TIM14_IRQn = 45, /*!< TIM8 Trigger and Commutation Interrupt and TIM14 global interrupt */

TIM8_CC_IRQn = 46, /*!< TIM8 Capture Compare Interrupt */

ADC3_IRQn = 47, /*!< ADC3 global Interrupt */

FSMC_IRQn = 48, /*!< FSMC global Interrupt */

SDIO_IRQn = 49, /*!< SDIO global Interrupt */

TIM5_IRQn = 50, /*!< TIM5 global Interrupt */

SPI3_IRQn = 51, /*!< SPI3 global Interrupt */

UART4_IRQn = 52, /*!< UART4 global Interrupt */

UART5_IRQn = 53, /*!< UART5 global Interrupt */

TIM6_IRQn = 54, /*!< TIM6 global Interrupt */

TIM7_IRQn = 55, /*!< TIM7 global Interrupt */

DMA2_Channel1_IRQn = 56, /*!< DMA2 Channel 1 global Interrupt */

DMA2_Channel2_IRQn = 57, /*!< DMA2 Channel 2 global Interrupt */

DMA2_Channel3_IRQn = 58, /*!< DMA2 Channel 3 global Interrupt */

DMA2_Channel4_5_IRQn = 59 /*!< DMA2 Channel 4 and Channel 5 global Interrupt */

#endif /* STM32F10X_XL */

#ifdef STM32F10X_CL

ADC1_2_IRQn = 18, /*!< ADC1 and ADC2 global Interrupt */

CAN1_TX_IRQn = 19, /*!< USB Device High Priority or CAN1 TX Interrupts */

CAN1_RX0_IRQn = 20, /*!< USB Device Low Priority or CAN1 RX0 Interrupts */

CAN1_RX1_IRQn = 21, /*!< CAN1 RX1 Interrupt */

CAN1_SCE_IRQn = 22, /*!< CAN1 SCE Interrupt */

EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

TIM1_BRK_IRQn = 24, /*!< TIM1 Break Interrupt */

TIM1_UP_IRQn = 25, /*!< TIM1 Update Interrupt */

TIM1_TRG_COM_IRQn = 26, /*!< TIM1 Trigger and Commutation Interrupt */

TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

TIM4_IRQn = 30, /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = 33, /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = 34, /*!< I2C2 Error Interrupt */

SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

SPI2_IRQn = 36, /*!< SPI2 global Interrupt */

USART1_IRQn = 37, /*!< USART1 global Interrupt */

USART2_IRQn = 38, /*!< USART2 global Interrupt */

USART3_IRQn = 39, /*!< USART3 global Interrupt */

EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

RTCAlarm_IRQn = 41, /*!< RTC Alarm through EXTI Line Interrupt */

OTG_FS_WKUP_IRQn = 42, /*!< USB OTG FS WakeUp from suspend through EXTI Line Interrupt */

TIM5_IRQn = 50, /*!< TIM5 global Interrupt */

SPI3_IRQn = 51, /*!< SPI3 global Interrupt */

UART4_IRQn = 52, /*!< UART4 global Interrupt */

UART5_IRQn = 53, /*!< UART5 global Interrupt */

TIM6_IRQn = 54, /*!< TIM6 global Interrupt */

TIM7_IRQn = 55, /*!< TIM7 global Interrupt */

DMA2_Channel1_IRQn = 56, /*!< DMA2 Channel 1 global Interrupt */

DMA2_Channel2_IRQn = 57, /*!< DMA2 Channel 2 global Interrupt */

DMA2_Channel3_IRQn = 58, /*!< DMA2 Channel 3 global Interrupt */

DMA2_Channel4_IRQn = 59, /*!< DMA2 Channel 4 global Interrupt */

DMA2_Channel5_IRQn = 60, /*!< DMA2 Channel 5 global Interrupt */

ETH_IRQn = 61, /*!< Ethernet global Interrupt */

ETH_WKUP_IRQn = 62, /*!< Ethernet Wakeup through EXTI line Interrupt */

CAN2_TX_IRQn = 63, /*!< CAN2 TX Interrupt */

CAN2_RX0_IRQn = 64, /*!< CAN2 RX0 Interrupt */

CAN2_RX1_IRQn = 65, /*!< CAN2 RX1 Interrupt */

CAN2_SCE_IRQn = 66, /*!< CAN2 SCE Interrupt */

OTG_FS_IRQn = 67 /*!< USB OTG FS global Interrupt */

#endif /* STM32F10X_CL */

} IRQn_Type;3.中断组和优先级的关系

NVIC有抢占优先级和子优先级两部分组成,那么抢占优先级用几位表示和子优先级是几位表示也是可以选的,一共五组可选,配置由下面代码所示。

/**

* @brief Configures the priority grouping: pre-emption priority and subpriority.

* @param NVIC_PriorityGroup: specifies the priority grouping bits length.

* This parameter can be one of the following values:

* @arg NVIC_PriorityGroup_0: 0 bits for pre-emption priority

* 4 bits for subpriority

* @arg NVIC_PriorityGroup_1: 1 bits for pre-emption priority

* 3 bits for subpriority

* @arg NVIC_PriorityGroup_2: 2 bits for pre-emption priority

* 2 bits for subpriority

* @arg NVIC_PriorityGroup_3: 3 bits for pre-emption priority

* 1 bits for subpriority

* @arg NVIC_PriorityGroup_4: 4 bits for pre-emption priority

* 0 bits for subpriority

* @retval None

*/

void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup)

{

/* Check the parameters */

assert_param(IS_NVIC_PRIORITY_GROUP(NVIC_PriorityGroup));

/* Set the PRIGROUP[10:8] bits according to NVIC_PriorityGroup value */

SCB->AIRCR = AIRCR_VECTKEY_MASK | NVIC_PriorityGroup;

}组一旦配置后,就不会轻易去修改,所以一般只配置一次。

①抢断优先级:高抢断优先级可打断低优先级(编号越小,优先级越高)

②子优先级:同时产生两个中断时,抢断优先级相同,子优先级越高,越先响应。(编号越小,优先级越高)

③中断号:同时产生两个中断时,且抢断优先级和子优先级相同,则中断号小的先响应。

这几条规则在《CM3权威指南》的7.2优先级的定义一节有详细描述。

这NVIC系统内容非常之多,涉及到许多底层的东西,我也只是看了个大概,但是常规使用还是相当简单的。下面就以代码配置来演示。

二、NVIC用标准库配置

NVIC需要配置,分组,中断源,抢占优先级,子优先级,使能中断源,配置如下,调用的标准库。

void usart_nvic_init(void)

{

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2); //设置NVIC中断分组2:2位抢占优先级,2位响应优先级

NVIC_InitStructure.NVIC_IRQChannel = USART1_IRQn; //使能串口所在的外部中断通道

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0x02; //抢占优先级2

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0x00; //子优先级0

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; //使能外部中断通道

NVIC_Init(&NVIC_InitStructure); //根据NVIC_InitStruct中指定的参数初始化外设NVIC寄存器

}三、EXTI框图

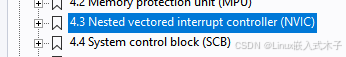

EXTI是外部中断的意思,结构框图在《STM32F103xCDE中文参考手册》的9节,中断和事件的9.2.2框图。红色的只是产生事件,提供给其它外设作为输入源,绿色的线是要执行中断服务函数。

在启动文件中的60个外部中断服务函数中就有他们的定义,一共16路中断线,但是只有7个中断服务函数,因为有些是共用的一个入口地址。

DCD EXTI0_IRQHandler ; EXTI Line 0

DCD EXTI1_IRQHandler ; EXTI Line 1

DCD EXTI2_IRQHandler ; EXTI Line 2

DCD EXTI3_IRQHandler ; EXTI Line 3

DCD EXTI4_IRQHandler ; EXTI Line 4

DCD EXTI9_5_IRQHandler ; EXTI Line 9..5

DCD EXTI15_10_IRQHandler ; EXTI Line 15..10由框图看EXTI还是比较简单,输入线进来后就是检测上升沿触发还是下降沿触发,另外就是使能中断和使能事件位。

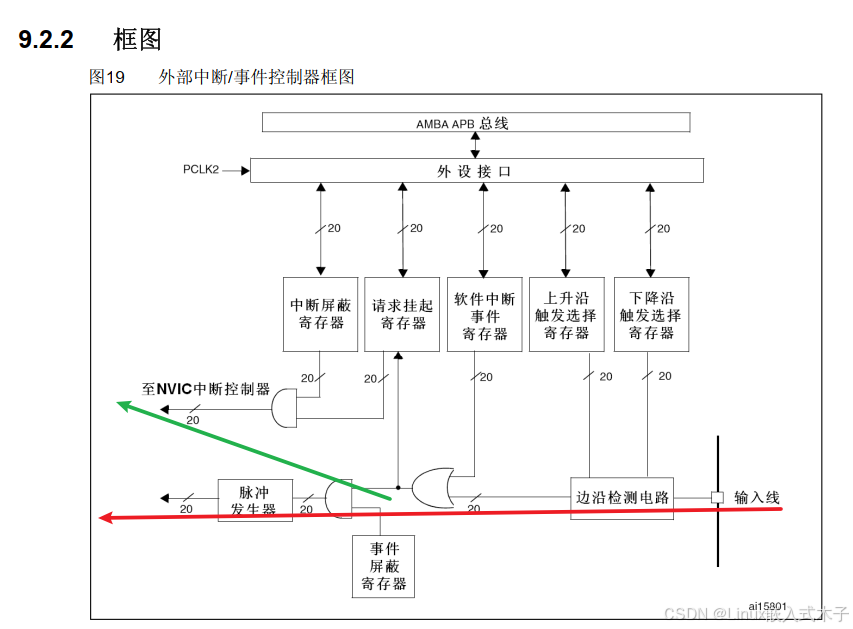

中断线也是要从GPIO复用过来的,复用的规则在《STM32F103xCDE中文参考手册》的9.2.5外部中断/事件线路映像有。如下图所示。EXTI0只能从所有GPIO组中选择一路,作为输入源。

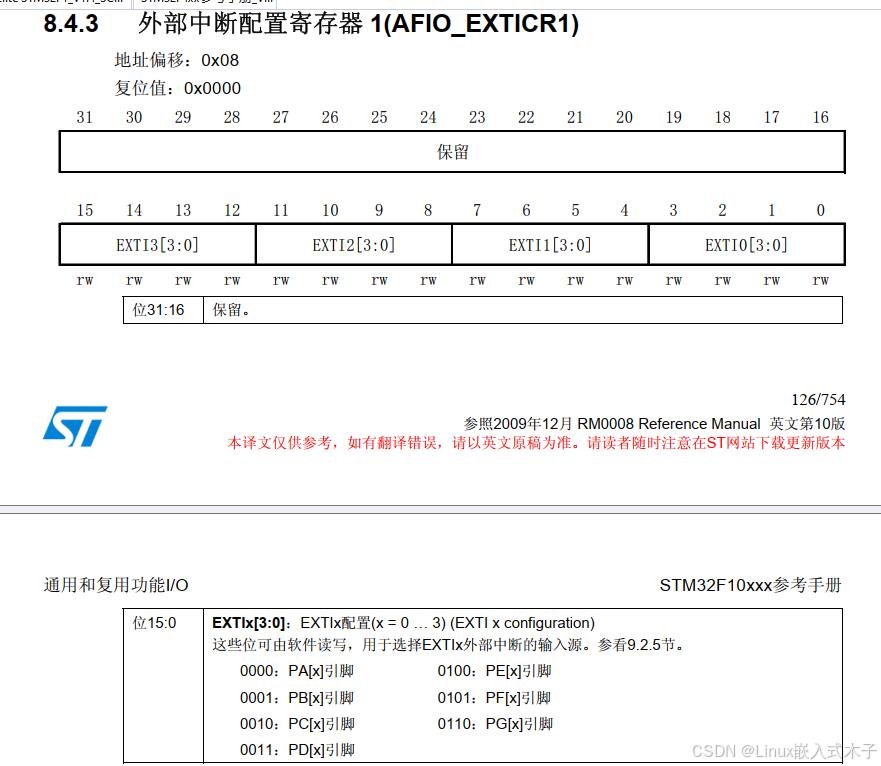

具体选择那一路作为输入源,由AFIO的EXTICRx控制,如下图所示

四、EXTI用标准库配置

以下为精英版V1.5的EXTI实验,将按键1和按键2配置为EXTI输入源,然后在中断服务函数中将LED灯翻转。有库再结合框图,感觉都不用看寄存器了。

void EXTIX_Init(void)

{

EXTI_InitTypeDef EXTI_InitStructure;

NVIC_InitTypeDef NVIC_InitStructure;

KEY_Init(); // 按键端口初始化

RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO,ENABLE); //使能复用功能时钟

//GPIOE.3 中断线以及中断初始化配置 下降沿触发 //KEY1

GPIO_EXTILineConfig(GPIO_PortSourceGPIOE,GPIO_PinSource3);

EXTI_InitStructure.EXTI_Line=EXTI_Line3;

EXTI_InitStructure.EXTI_Mode = EXTI_Mode_Interrupt;

EXTI_InitStructure.EXTI_Trigger = EXTI_Trigger_Falling;

EXTI_Init(&EXTI_InitStructure); //根据EXTI_InitStruct中指定的参数初始化外设EXTI寄存器

//GPIOE.4 中断线以及中断初始化配置 下降沿触发 //KEY0

GPIO_EXTILineConfig(GPIO_PortSourceGPIOE,GPIO_PinSource4);

EXTI_InitStructure.EXTI_Line=EXTI_Line4;

EXTI_Init(&EXTI_InitStructure); //根据EXTI_InitStruct中指定的参数初始化外设EXTI寄存器

//GPIOA.0 中断线以及中断初始化配置 上升沿触发 PA0 WK_UP

GPIO_EXTILineConfig(GPIO_PortSourceGPIOA,GPIO_PinSource0);

EXTI_InitStructure.EXTI_Line=EXTI_Line0;

EXTI_InitStructure.EXTI_Trigger = EXTI_Trigger_Rising;

EXTI_Init(&EXTI_InitStructure); //根据EXTI_InitStruct中指定的参数初始化外设EXTI寄存器

NVIC_InitStructure.NVIC_IRQChannel = EXTI0_IRQn; //使能按键WK_UP所在的外部中断通道

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0x02; //抢占优先级2,

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0x03; //子优先级3

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; //使能外部中断通道

NVIC_Init(&NVIC_InitStructure);

NVIC_InitStructure.NVIC_IRQChannel = EXTI3_IRQn; //使能按键KEY1所在的外部中断通道

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0x02; //抢占优先级2

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0x01; //子优先级1

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; //使能外部中断通道

NVIC_Init(&NVIC_InitStructure); //根据NVIC_InitStruct中指定的参数初始化外设NVIC寄存器

NVIC_InitStructure.NVIC_IRQChannel = EXTI4_IRQn; //使能按键KEY0所在的外部中断通道

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0x02; //抢占优先级2

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0x00; //子优先级0

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; //使能外部中断通道

NVIC_Init(&NVIC_InitStructure); //根据NVIC_InitStruct中指定的参数初始化外设NVIC寄存器

}五、总结与展望

NVIC很复杂,需要细看《CM3权威指南》和《STM32F1xx Cortex-M3编程手册-英文版》,还有标准库,主要是熟悉标准库中如何配置,最好熟悉寄存器操作,调试的时候直接看寄存器方便很多。EXTI的配置还是挺简单,但是后续要应用起来的话还是得多做实验。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?