12bit 100MHz pipelined ADC 设计

65nm工艺,电源电压1.2V,ENOB=11.6

结构:

栅压自举开关

CDAC

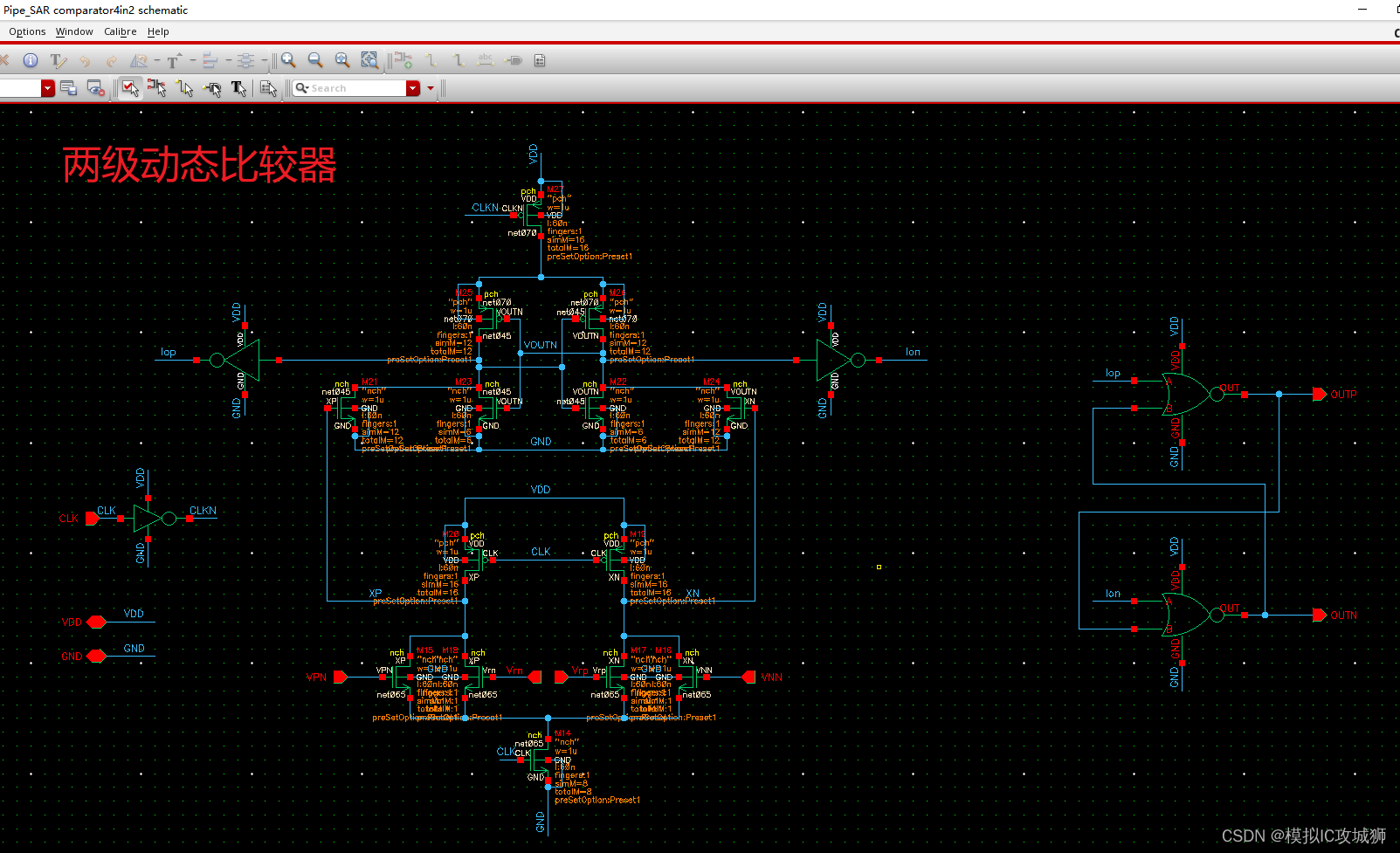

两级动态比较器

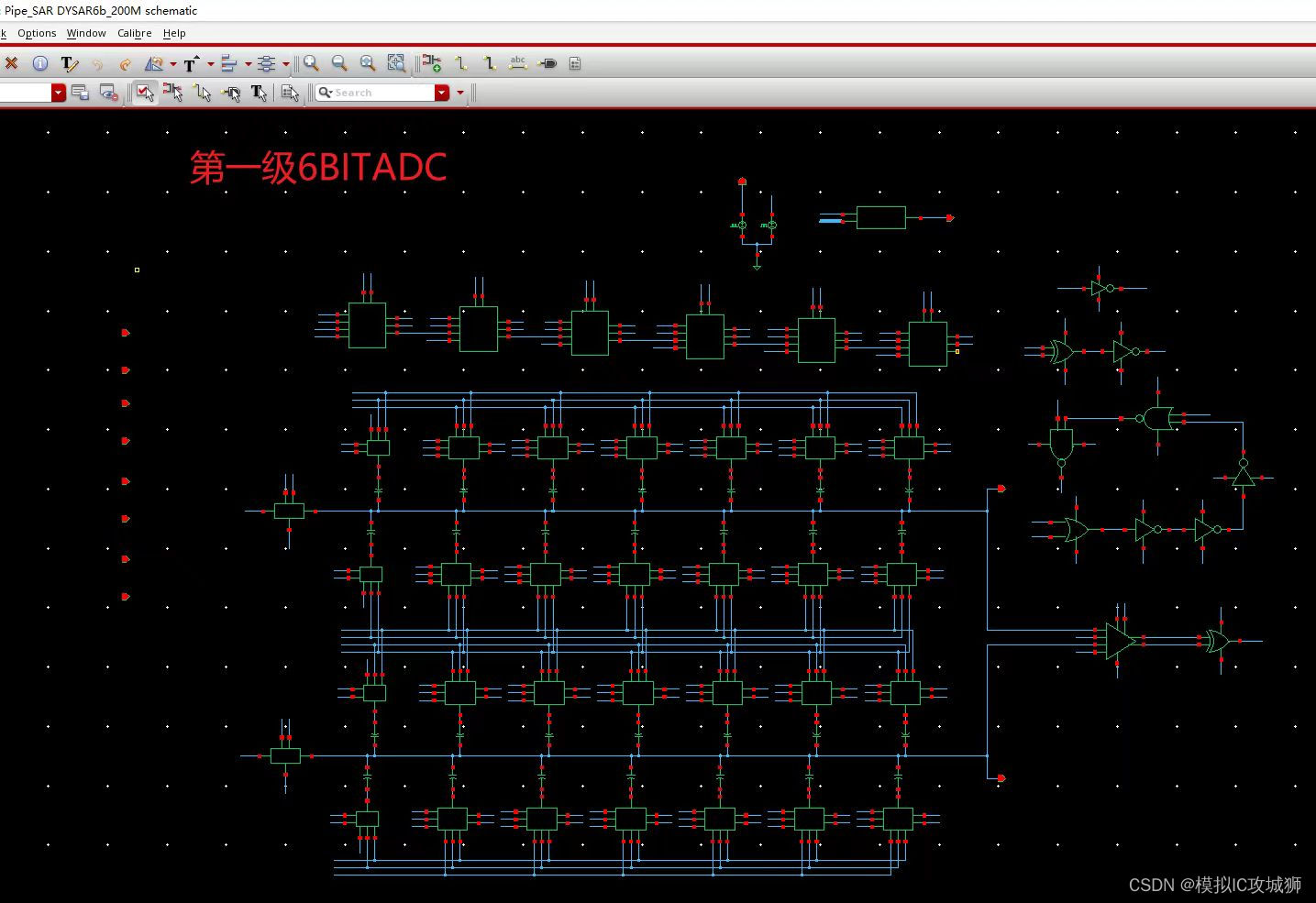

第一级6位SAR ADC

余量放大器

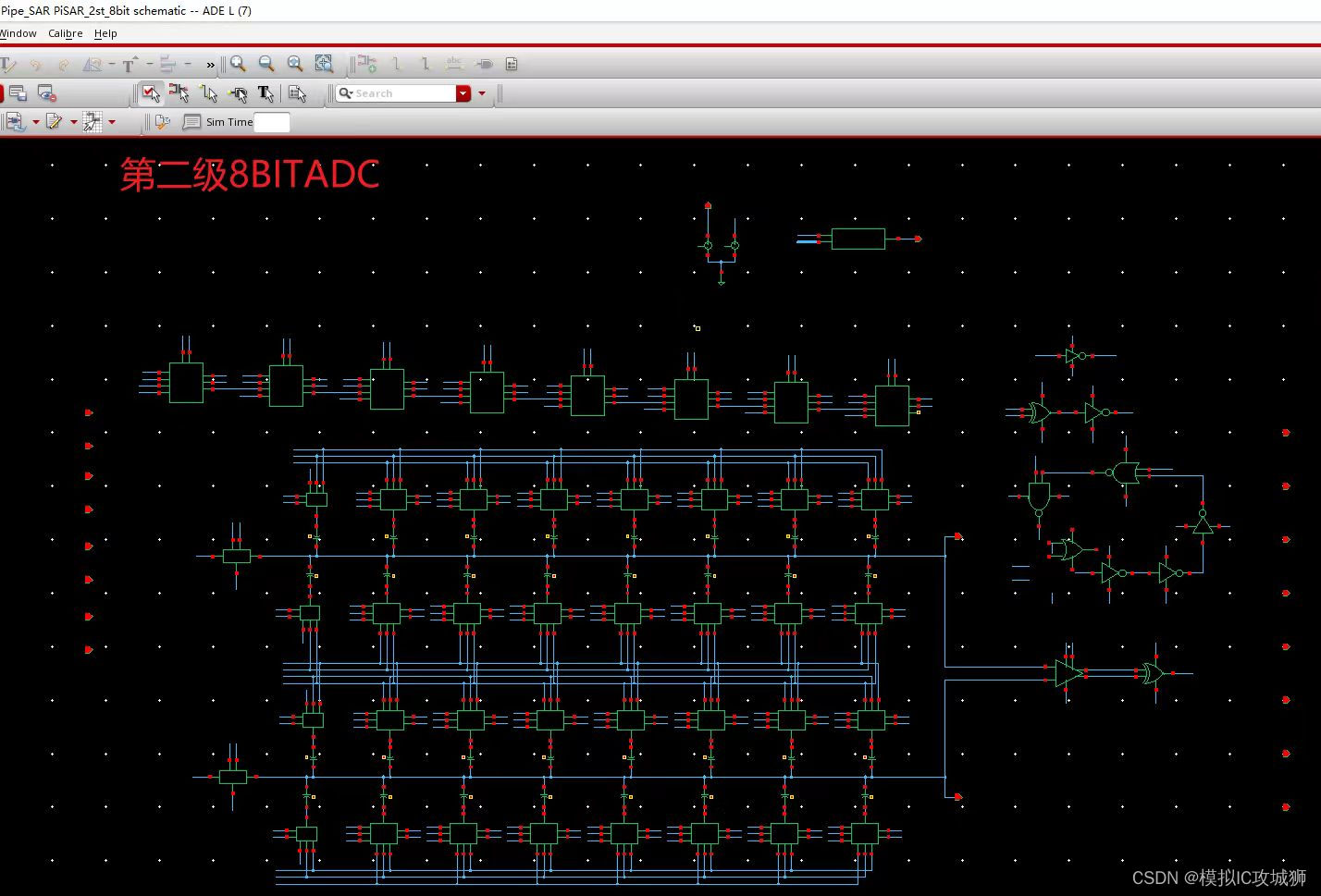

第二级8位SAR ADC

同步和异步SAR logic都有

n 采用TSMC65nm工艺,电源电压1.2V,采样时钟100MHz,信号带宽50MHz

系统总体指标:输入fclk=100MHz, fin=47×fclk/1024Hz,Vcm=600mV,amp=400mV,为ADC满摆幅输入

n 有效位数ENOB:11.6bit

n 信噪比SNR:61.20dB

n 无杂散动态范围SFDR:71.26dB

n 总谐波失真THD:-70.97dB

第一位ADC:输入fin=47×fclk/1024Hz,Vcm=600mV,amp=400mV,为第一位ADC满摆幅输入

n 有效位数ENOB:9.86bit

n 信噪比SNR:61.20dB

n 无杂散动态范围SFDR:71.26dB

n 总谐波失真THD:-70.97dB

第二位ADC:输入fin=47×fclk/1024Hz,Vcm=600mV,amp=200mV,为第二位ADC满摆幅输入

n 有效位数ENOB:9.86bit

n 信噪比SNR:61.20dB

n 无杂散动态范围SFDR:71.26dB

n 总谐波失真THD:-70.97dB

第一级 6BIT SAR ADC

第二级 8BIT SAR ADC

两级动态比较器

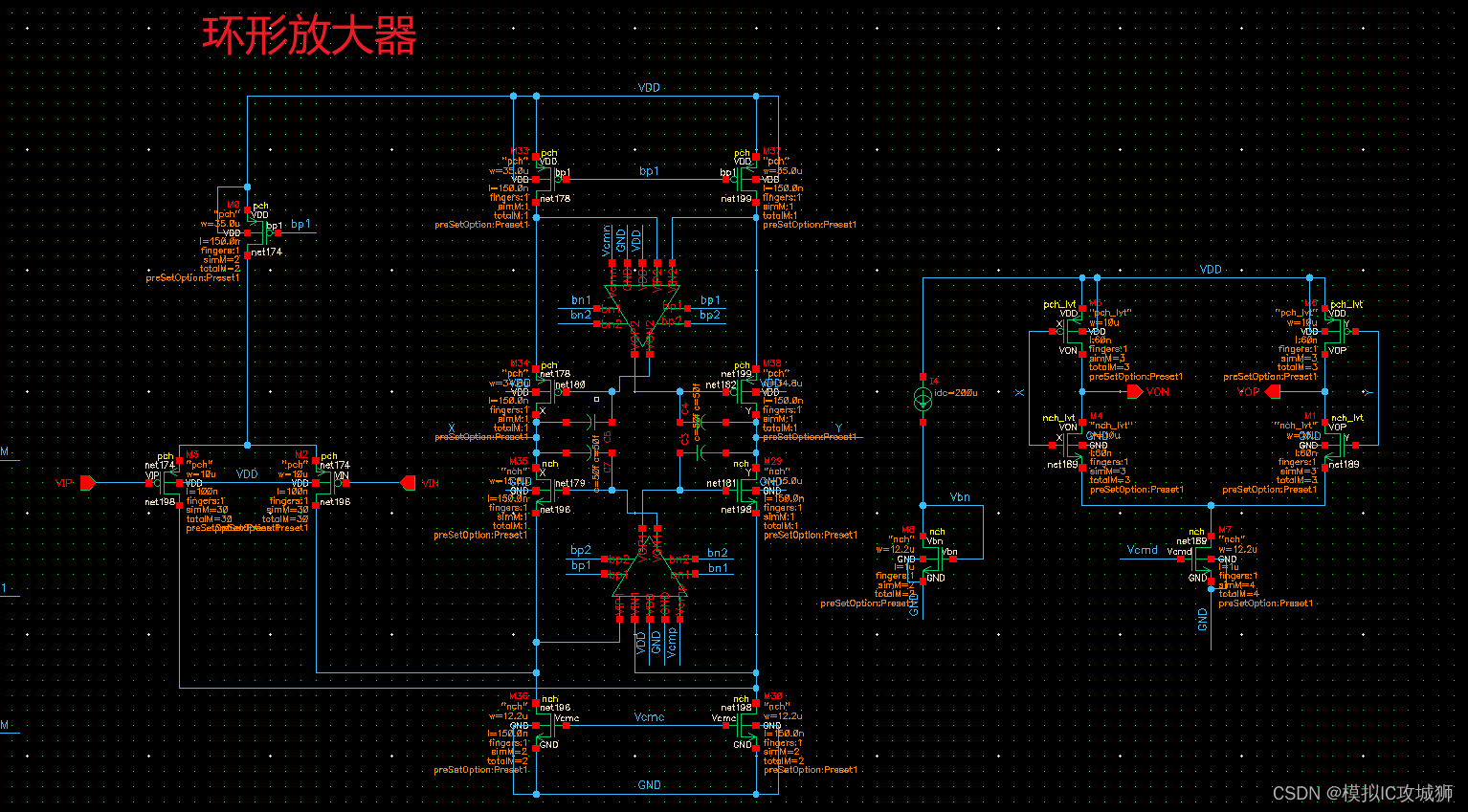

环形放大器

详细原理讲解

本文详细介绍了使用65nm工艺的12bit100MHzpipelinedADC设计,包括其架构(栅压自举开关、两级SARADC和动态比较器)、性能指标(ENOB、SNR、SFDR和THD),以及对环形放大器的运用。

本文详细介绍了使用65nm工艺的12bit100MHzpipelinedADC设计,包括其架构(栅压自举开关、两级SARADC和动态比较器)、性能指标(ENOB、SNR、SFDR和THD),以及对环形放大器的运用。

2930

2930