1.Overview of DRAMs

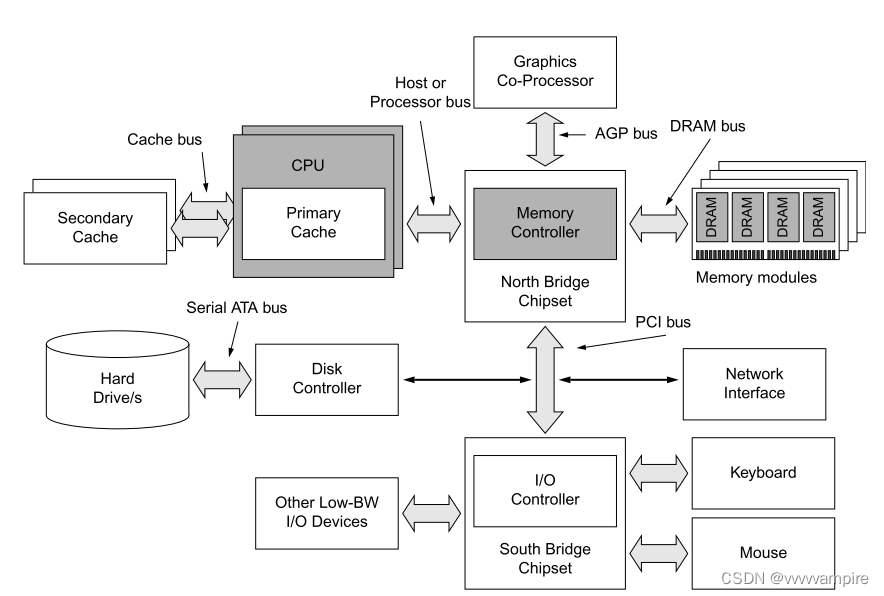

单个DRAM设备通常通过存储器控制器(Memory Controller)间接连接到CPU。 在PC系统中,存储器控制器是north-bridge 芯片组的一部分,它处理潜在的多个微处理器、图形协处理器、与sorth-bridge 芯片组的通信(南桥芯片组处理系统的所有I/O功能)以及与DRAM系统的接口(Interface)。 尽管现在仍然经常被称为“芯片组”,北桥和南桥芯片组不再是一组芯片; 它们通常被实现为单个芯片,在某些系统中,两者的功能被合并到单个芯片中。

(“芯片组”术语通常是特指计算机主板或扩展卡上的芯片。当讨论基于英特尔的奔腾级处理器的个人电脑时,芯片组一词通常指两个主要的主板芯片组:北桥和南桥。)

由于DRAM通常是一个外部设备,因此在它的使用、设计和分析时必须考虑在使用、设计和分析片上存储器(如SRAM缓存和scratch-pads)时经常被忽略的实现效果。 设计者必须考虑的问题包括:

- 引脚(例如,它们的电容和电感)

- 信号

- 信号完整性

- 封装

- 时钟和同步

- 时序约定

7.1 DRAM Basics: Internals, Operation

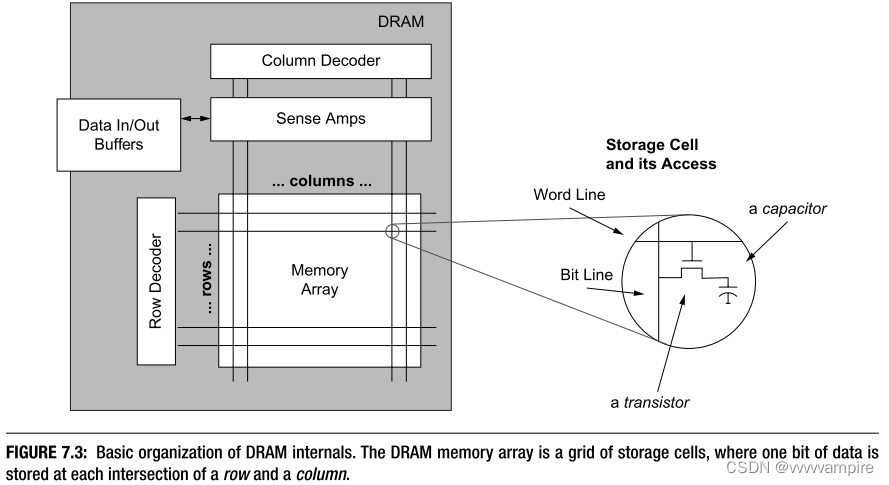

随机存取存储器(RAM)每一位都使用单个晶体管-电容对,称为动态随机存取存储器或DRAM。由于电容存储电子会产生泄露,因此DRAM的每个电容需要周期性的进行刷新(read 或 rewritten操作)。每个DRAM die包含一个或多个存储器阵列,每个cell储存一个比特的数据,组成矩形网格。

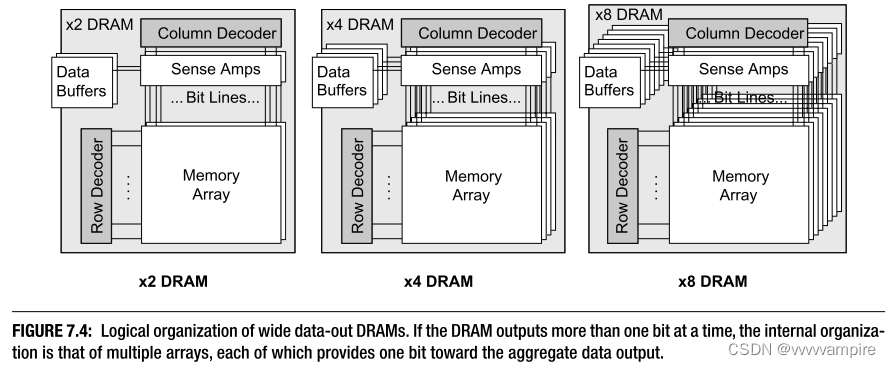

存储芯片内的存储阵列可以以几种不同的方式工作。 unison/completely independently,或者以介于其他两者之间的方式行动。 如果存储器阵列被设计成unison act,则它们作为一个单元操作,并且存储器芯片通常在存储器控制器每次访问DRAM时发送或接收等于阵列(array)数量的比特数。

每个DRAM 的图都表示多个array,但只有一个存储体(bank)。 独立于其他集合运行的每一组memory array被称为一个存储体,而不是一个array。 每个bank是独立的,因为只有一些限制,它可以被激活、预充电、读出等,同时其他存储体(在同一DRAM设备上或在其他DRAM设备上)被激活、预充电等。自DRAM发明以来,使用多个独立的存储体一直是计算机设计中的常见做法。interleaving多个存储体是使用低带宽设备实现高带宽存储总线的流行方法,控制电路在多个bank之间来回切换以实现高数据速率。

一个系统可以有多个DIMM,每个DIMM可以被认为是一个独立的bank,而每个DIMM上的DRAM设备可以在内部实现多个独立的bank,所以引入了 "rank "一词来区分DIMM级的独立操作和内部bank级的独立操作。图7.5说明了现代DRAM系统中的各种组织层次。一个系统是由潜在的许多独立DIMM组成的。每个DIMM可能包含一个或多个独立的rank。每个rank都是一组统一操作的DRAM设备,在内部,每个DRAM设备都实现了一个或多个独立的bank。最后,每个bank由从属的内存阵列组成,阵列的数量等于DRAM部分的数据宽度(即,一个x4部分在每个bank有四个从属阵列)。在rank级和bank级上有并发性,可以通过流水线请求提供带宽。多个DRAM在rank级上一致作用,多个array在bank级上一致作用,以并行访问的形式提供带宽。

JEDEC-style组织中的总线按其功能和组织分为数据、地址、控制和芯片选择总线。图7.6是一个arrangement的例子,它描述了一个连接到两个memory模块的memory控制器。在DRAM之间传输数据的数据总线是比较宽的。它通常是64位宽,在高性能系统中它可以更宽。专用的地址总线将行和列的地址传送给DRAM,其宽度随着DRAM设备上的物理存储而增长(目前典型的宽度约为15位)。控制总线由行和列选通(strobe)、输出使能、时钟、时钟使能和其他相关信号组成。

(A “strobe” is a signal that indicates to the recipient that another signal, e.g., data or command, is present and valid.)

这些信号类似于地址总线信号,因为它们都从存储器控制器连接到系统中的每个DRAM。 最后,有一个芯片选择网络,从存储器控制器连接到一个rank中的每个DRAM(一组可单独寻址的DRAM)。 例如,存储器模块可以包含两个rank级的DRAM设备; 对于系统中的每个DIMM,可以有两个独立的芯片选择网络,因此,芯片选择“总线”的大小与系统中的最大物理内存量成比例。

芯片选择信号包含一条单独的线,用于系统中每一个rank的DRAM。芯片选择信号通过每一小组DRAM特有的线路,并启用或禁用该等级的DRAM,使它们分别处理当前总线上的请求或忽略当前总线上的请求。因此,只有请求所指向的DRAM才会处理该请求。尽管系统中的所有DRAM都连接到相同的地址和控制总线上,并且在理论上可以同时响应同一个请求,但芯片选择总线阻止了这种情况的发生。

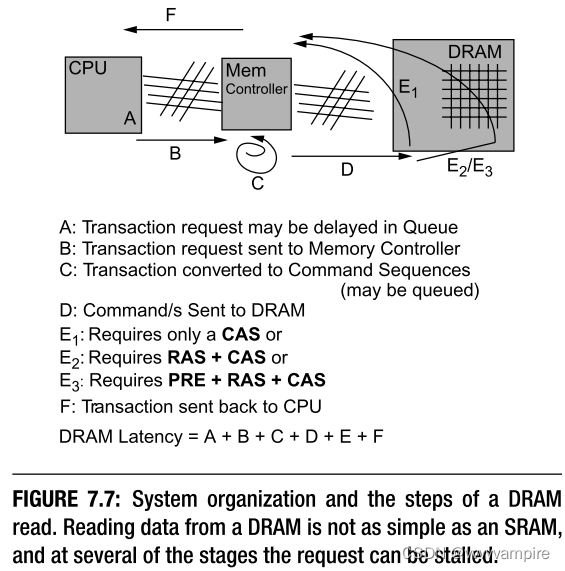

存储器控制器充当CPU和DRAM之间的联络,使得CPU不需要知道DRAM操作的细节。DIMM是消费者购买DRAM最常见的物理形式,这些都是小型的PCB,每个都有少量的DRAM设备。 存储器控制器通常连接到至少一个DIMM,因此一次连接到多个DRAM设备。

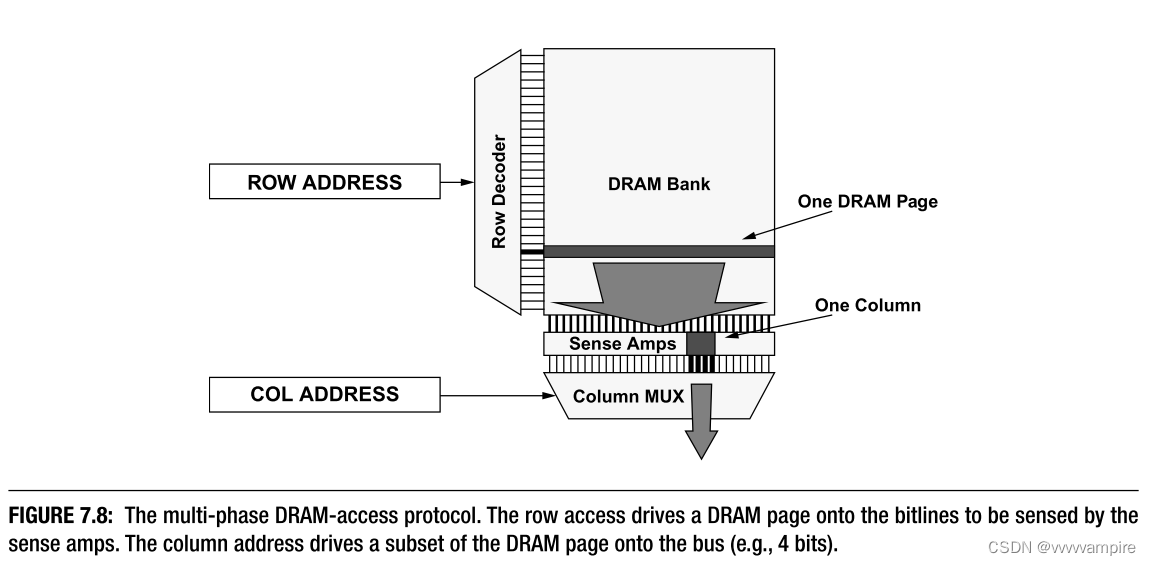

图7.8详细显示了行地址选通(RAS)和列地址选通(CAS)组件。 存储器控制器必须将提供的数据地址分解成识别存储器系统中适当等级的组件,rank级中的bank,以及识别bank中的行和列。识别行和列的组件被称为行地址和列地址。bank的标识符通常是一个或多个地址位。rank号最终导致芯片选择信号通过单独的芯片选择线发送出去。

一旦标识了rank、bank和row,就必须对相应bank中的位线进行预充电(设置为介于0和1之间的逻辑电平)。 一旦存储体被预充电,第二步是通过设置芯片选择信号以激活包括所需存储体的DRAM,通过地址总线发送行地址和bank标识,并向DRAM的引脚发出信号(行地址选通-指示信号在低时有效)来激活所标识的rank和bank内的适当行。 这告诉DRAM将整行数据(数千位)发送到DRAM的读出放大器(检测和放大由该行存储单元中的电荷表示的微小逻辑信号的电路)。 这通常需要几十纳秒,并且步骤可能已经完成(行或页可能已经打开或激活,这意味着检测放大器中可能已经有有效数据)。

一旦读出放大器恢复了值,并且位线被拉到适当的逻辑电平,存储器控制器执行最后一步,即读取列(列是给所需行的数据子集的名称),方法是设置芯片选择信号以激活包括所需bank的DRAMs集合,通过地址总线发送列地址和存储体标识,并向DRAM的引脚发出信号(列地址选通-指示信号在低时)。这就使得读出放大器中只有几个选择的位连接到输出驱动器,在那里它们将被驱动到数据总线上。 读取列数据需要几十纳秒的时间。 当存储器控制器接收到数据时,它将数据转发给微处理器。

在两个不同的步骤中发送地址(即,分别发送行和列地址)的过程与SRAMs不同。 最初,DRAMS的I/O引脚数量很少,因为制造成本主要取决于封装中的I/O引脚数量。 这种限制I/O引脚的需求对DRAM架构产生了长期影响; 大多数DRAMs的地址引脚仍然是多路复用的,这意味着数据地址的两个不同部分在不同的时间通过相同的引脚发送,而不是使用更多的地址引脚并一次发送整个地址。

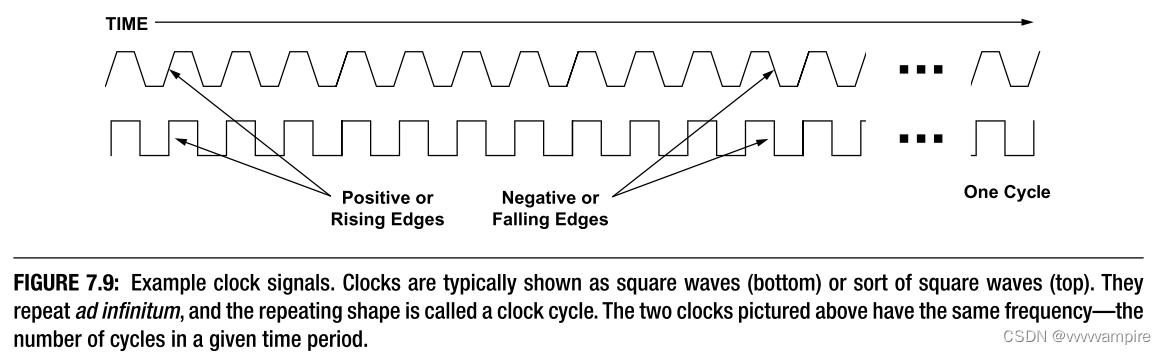

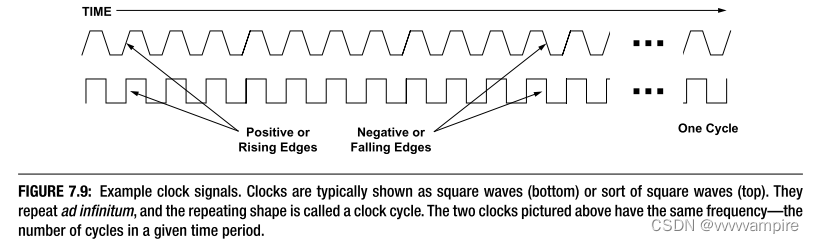

计算机系统中的主时钟被称为系统时钟或全局时钟,它通常在主板(包含微处理器和内存总线的PCB)上。 系统时钟直接驱动微处理器和存储器控制器以及许多相关的外围设备。 如果时钟直接驱动DRAM,则DRAMs称为同步DRAMs。 如果时钟不直接驱动DRAM,则DRAMs称为异步DRAMs。 在同步DRAM中,DRAM内部的步骤与时钟的一个或多个边沿同步发生。 在异步DRAM中,当存储器控制器命令DRAM动作时,DRAM内部的操作步骤发生,并且这些命令通常与系统时钟的一个或多个沿同步发生。

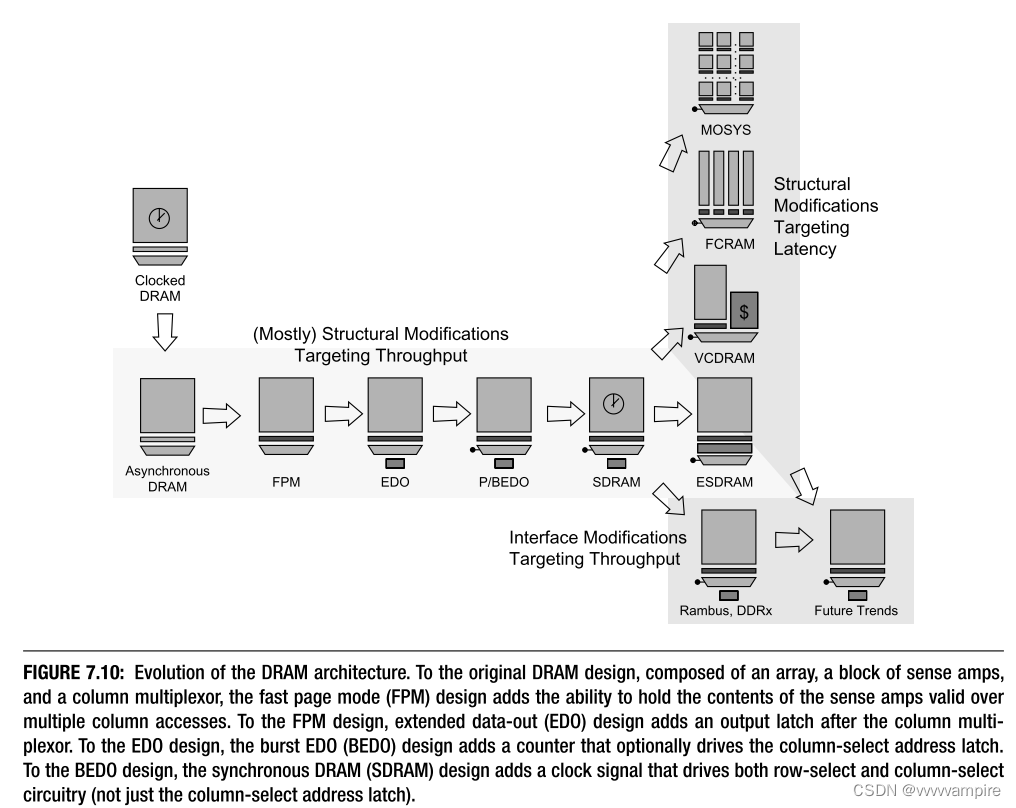

7.2 Evolution of the DRAM Architecture

the basic DRAM architecture :

- clocked

- the conventional asynchronous

- fast page mode (FPM)

- extended dataout (EDO)

- burst-mode EDO (BEDO)

- synchronous(SDRAM)

7.2.1 Structural Modifications Targeting Throughput

与传统的DRAM相比,FPM只允许行在多个CAS命令之间保持开放,只需要很少的额外电路。 为此,EDO将输出驱动器更改为输出锁存器,以便它们将有效的数据保存在bus更长的一段时间。 为此,BEDO添加了一个内部计数器来驱动地址锁存器,这样,如果所需的地址仅仅是前一个CAS命令的一个地址,则存储器控制器不需要在每个CAS命令上向DRAM提供新的地址。 因此,在BEDO中,DRAM的列选择电路由内部产生的信号驱动,而不是外部产生的信号; 控制信号的源在空间和时间上都接近于它所控制的电路,这使得电路的激活时间更加精确。 最后,SDRAM更进一步,通过时钟驱动所有内部电路(行选择、列选择、数据读出),而不是RAS和CAS选通。

本文介绍了DRAM的工作原理及其在计算机系统中的角色。涵盖了从传统异步到同步DRAM的发展历程,并探讨了提高吞吐量的结构修改。

本文介绍了DRAM的工作原理及其在计算机系统中的角色。涵盖了从传统异步到同步DRAM的发展历程,并探讨了提高吞吐量的结构修改。

3356

3356

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?