1.存储程序思想

计算机由输入设备、输出设备、运算器、存储器、控制器 组成

运算器+控制器=CPU

CPU+主存=主机

输入|输出设备+外存=外设 or I/O设备

程序基本单位:指令=操作码+地址码

( 冯.若依曼思想)核心:存储程序是指在计算机解题之前,事先编号程序,并连同所需的数据预先存入主存储器中。在解题过程中,由控制器按事先编好并存入存储器自动地、连续地从存储器中依次取出指令并执行,直到获得所要求的结果为止。高速运行的基础。

other

速度:汇编>高级>应用

CAD 设计 带动 CAM 制造

2.10->2

up down

请忽略这个zero

extra:

next:

阶码表示指数部分,移码作为阶码是因为便于比较值的大小

Core:

and

在0.XXXXX系列,符号位是指“+0” ”-0“

反码到补码 只差一个末位加1

补->移码后,数值位也取反,且末位加1

other

循环冗余校验码 是在 n位 有效信息位后拼接k位校验码构成的,他通过 除法运算来建立有效信息 和校验码之间的约定关系,是一种检错纠错能力很强的校验码。

3.变形补码

双符号位罢了,和补码没什么关系(大概)

0表示正,00为正数,无益出,01,表示正溢出

then

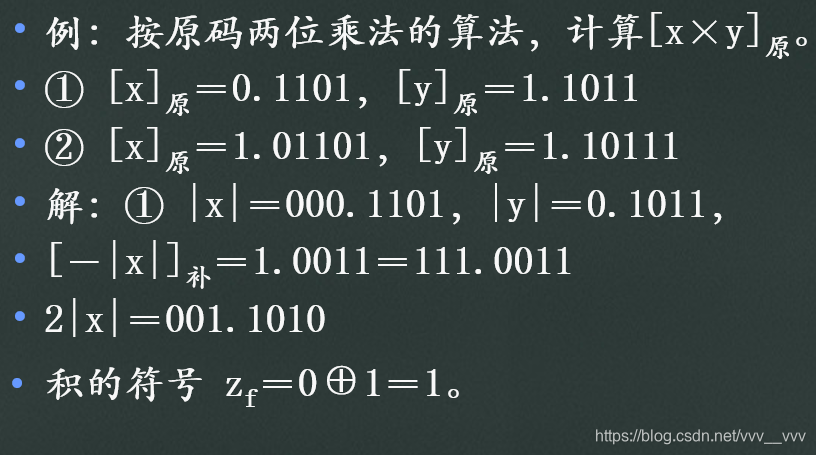

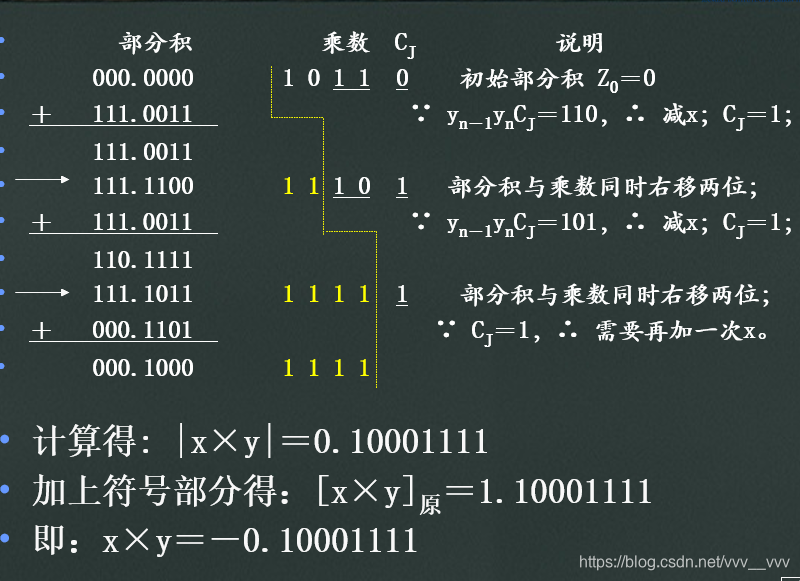

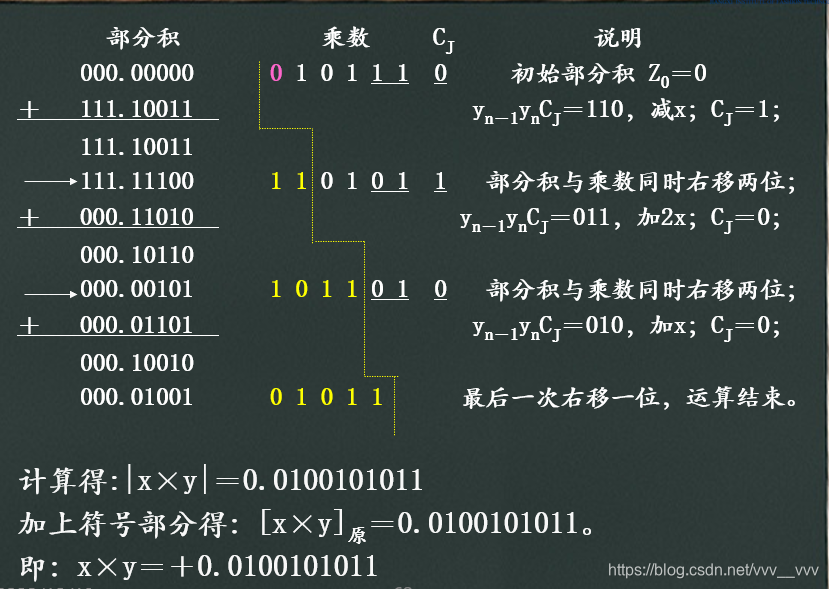

原码两位乘法

讨论x * y = z 采用原码两位乘法,已知x和y,如何求得z(积的符号)

符号位不参加运算

部分积和被乘数x均采用三位符号,乘数y末位每次要加一个c,c一开始是0,第一次加减也要由后三位决定

根据如下法则进行运算:(求出结果后右移右移后,观察后三位,决定下次要加的数)

· 000 -》 部分积加0, 右移两位,c变为0

· 001 -》 部分积加|x|, 右移两位,c变为0

· 010 -》 部分积加|x|, 右移两位,c变为0

· 011 -》 部分积加2|x|,右移两位,c变为0

· 100 -》 部分积加2|x|,右移两位,c变为0

· 101 -》 部分积减|x|, 右移两位,c变为1

· 110 -》 部分积减|x|, 右移两位,c变为1

· 111 -》 部分积加0, 右移两位,c变为1

所谓减x,就是-x的补码

而乘数y用双符号还是单符号表示得根据乘数y的数值的奇偶性判断,而且最后一步移位与否也与乘数y的数值的奇偶性有关:

· 如果乘数y的尾数n的位数为偶数,去掉符号位直接用,最后一步不移位

· 如果乘数y的尾数n的位数为奇数,去掉符号位而且要在前面补个0,最后一步要移一位

如果为0,请忽略

example:

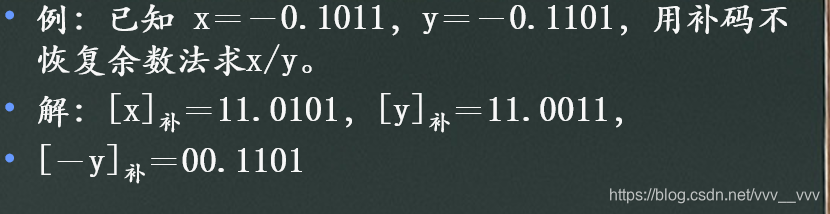

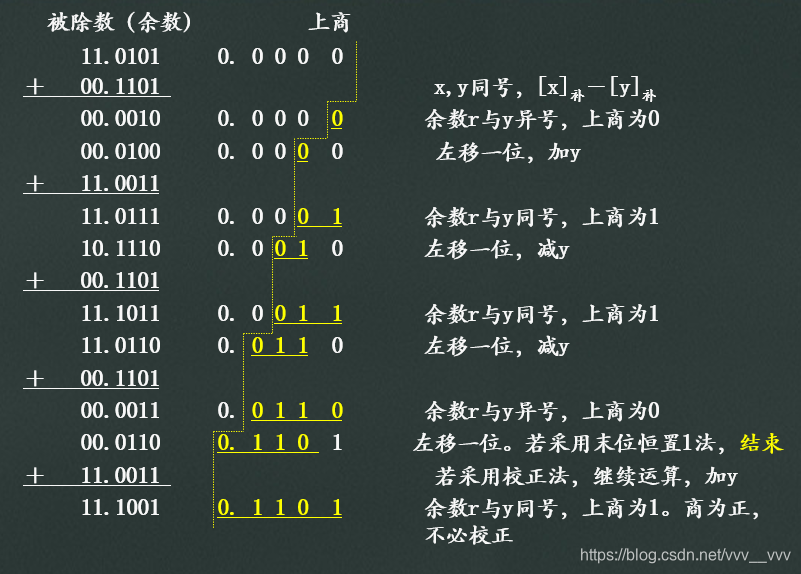

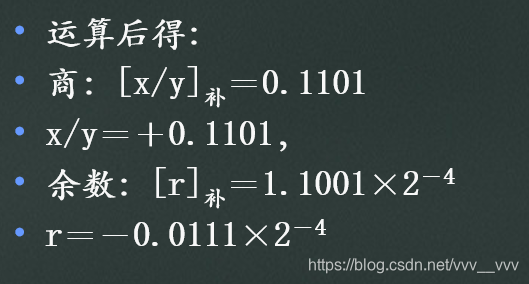

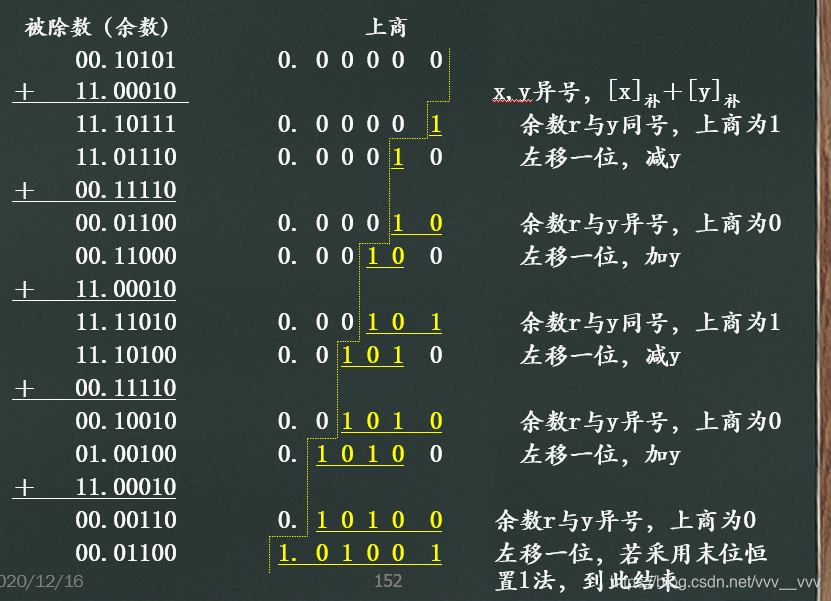

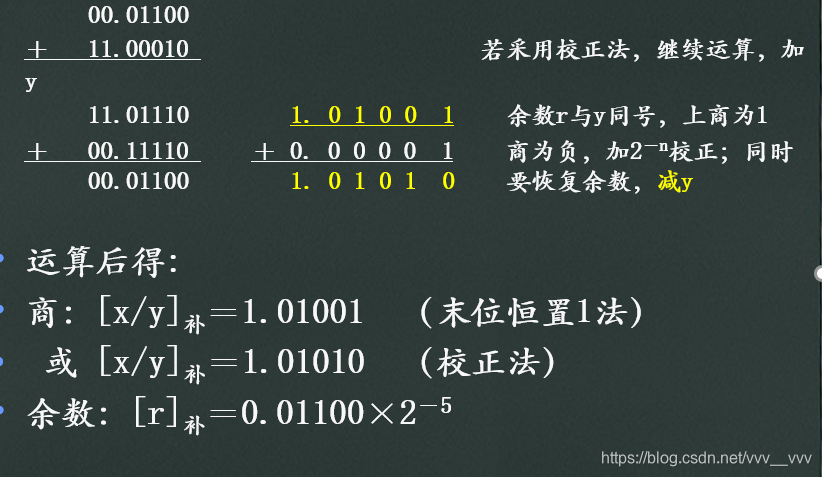

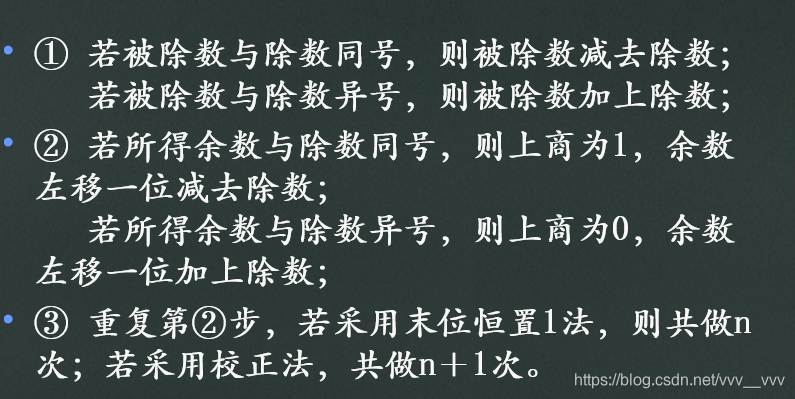

补码不回复除数法:

opinion

说明这两种方法的(主要)顺序:

原码两位乘法:

先右移,判CJ,在由后三位决定后面加什么。

补码不回复除法:

先由同异号决定加减,在由除数与y比较同异号(这个同时也决定了下次的加减),得商,并且带着商左移一位。

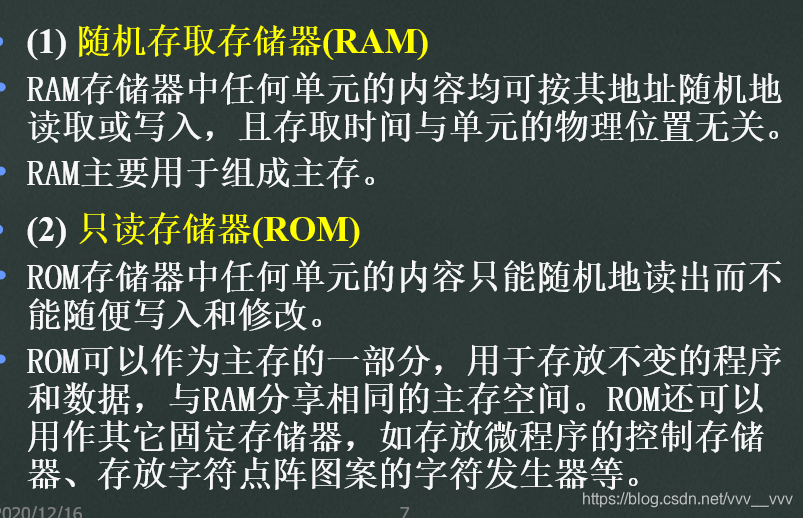

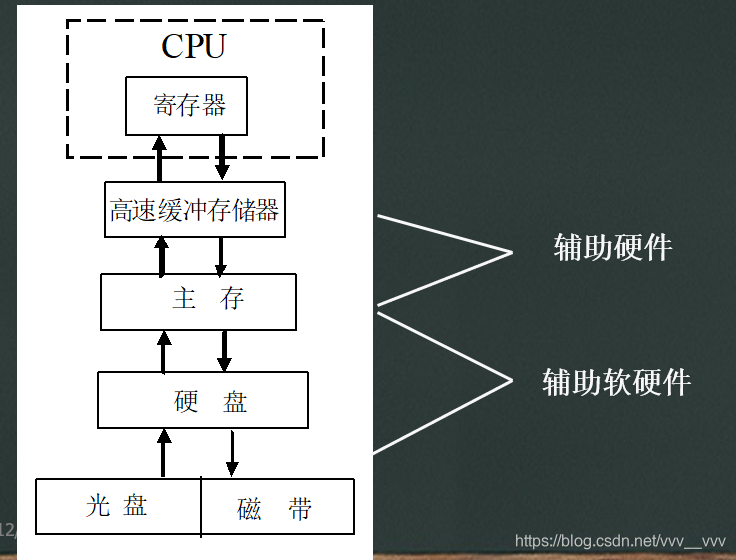

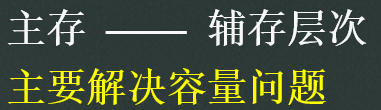

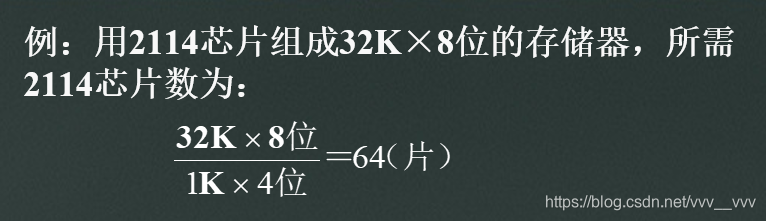

4.存储器

then

then

字长=数据总线 N位N条

地址线:256=8

k=10

10+8=18

other

四种刷新方式:

集中式 分散式 异步式 隐含式

then

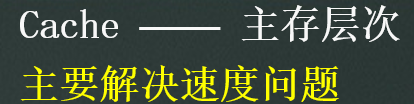

当CPU存储数据或指令时,按 数据 或 指令 在内存中的内存地址去与Cache中已存放的数据或指令的地址相比较。若相等,说明Cache中找到了需要的数据与指令(称为Cache命中),则CPU不需要任何等待状态,Cache就可以将信息传给它。若不相等,说明需要的数据或指令不在Cache中(称为未命中),存储器控制电路从内存中取出数据或指令传送给CPU,同时拷贝一份副本到Cache中。

‘then

5.begin

then

important:

sametimes:

unimportant

then

加粗样式

6begin

then

then

then

core

same

7.begin

then

then

8.begin

9.begin

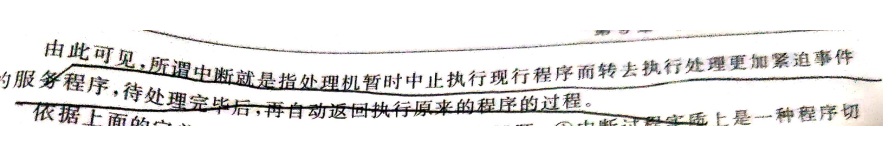

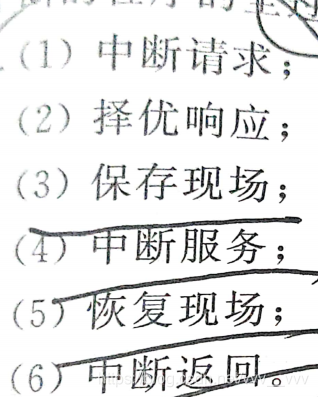

then:

断点:堆栈

本文详述了计算机组成原理的核心概念,包括存储程序思想、计算机的五大部分组成、运算器与控制器的功能。讲解了冯·诺依曼结构的工作原理,强调了高速运行的基础。此外,还涉及了指令系统、数据表示(如移码和补码)、循环冗余校验码的原理,以及原码两位乘法的运算规则。同时,概述了存储器的字长、地址线计算以及四种刷新方式。

本文详述了计算机组成原理的核心概念,包括存储程序思想、计算机的五大部分组成、运算器与控制器的功能。讲解了冯·诺依曼结构的工作原理,强调了高速运行的基础。此外,还涉及了指令系统、数据表示(如移码和补码)、循环冗余校验码的原理,以及原码两位乘法的运算规则。同时,概述了存储器的字长、地址线计算以及四种刷新方式。

823

823

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?