PCIe(Peripheral Component Interconnect Express)是一种高速串行计算机扩展总线标准,用于计算机硬件设备的连接。它继承了 PCI 总线的概念,并进行了显著的改进,以支持更高的数据传输速率和更灵活的拓扑结构。

PCIe 协议的主要特点

-

高速串行连接:

-

PCIe 使用高速串行连接,每个通道(lane)可以独立传输数据,支持更高的数据传输速率。

-

例如,PCIe 4.0 的每个通道可以达到 16 GT/s(Gigatransfers per second),而 PCIe 5.0 提高到 32 GT/s。

-

-

点对点连接:

-

PCIe 采用点对点的连接方式,每个设备都有自己的专用连接,避免了传统并行总线中的共享带宽问题。

-

-

动态配置:

-

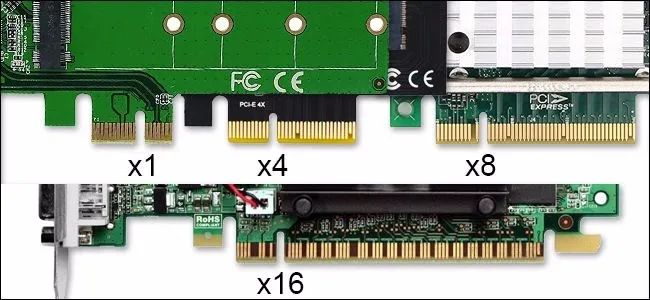

PCIe 支持动态配置,设备可以在运行时动态调整其连接的宽度(如 x1、x4、x8、x16 等)和速度。

-

-

热插拔支持:

-

PCIe 支持热插拔,允许在不重启系统的情况下插入或移除设备。

-

-

电源管理:

-

PCIe 提供了多种电源管理功能,允许设备在不使用时进入低功耗模式。

-

PCIe 协议的版本

-

PCIe 1.0:2003年发布,每个通道速率2.5 GT/s。

-

PCIe 2.0:2007年发布,每个通道速率5 GT/s。

-

PCIe 3.0:2010年发布,每个通道速率8 GT/s。

-

PCIe 4.0:2017年发布,每个通道速率16 GT/s。

-

PCIe 5.0:2019年发布,每个通道速率32 GT/s。

-

PCIe 6.0:2021年发布,每个通道速率64 GT/s。

PCIe 协议的拓扑结构

-

根复合体(Root Complex):

-

PCIe 架构的起点,通常位于 CPU 或芯片组中,负责初始化和管理 PCIe 总线。

-

-

交换机(Switch):

-

用于扩展 PCIe 总线,允许更多的设备连接到 PCIe 总线。

-

-

端点(Endpoint):

-

PCIe 设备,如 GPU、NIC、SSD 等,连接到 PCIe 总线并提供特定的功能。

-

PCIe 协议的工作原理

-

事务层(Transaction Layer):

-

负责处理数据传输的事务,包括读写操作、中断等。

-

-

数据链路层(Data Link Layer):

-

负责数据的封装和解封装,确保数据的完整性和顺序。

-

-

物理层(Physical Layer):

-

负责电气信号的传输,包括信号的编码、解码和时钟恢复。

-

PCIe 协议的应用场景

-

计算机硬件:

-

PCIe 是现代计算机中连接 GPU、NIC、SSD 等设备的标准接口。

-

-

数据中心:

-

PCIe 用于连接服务器中的各种扩展卡,如 GPU 加速卡、网络接口卡等。

-

-

嵌入式系统:

-

PCIe 也用于嵌入式系统中,连接各种高性能设备。

-

总结

PCIe 协议是一种高性能、灵活的串行总线标准,广泛应用于计算机硬件、数据中心和嵌入式系统中。随着技术的不断进步,PCIe 的数据传输速率不断提高,支持更多的功能和应用场景。

PCIe插槽

主板支持的 PCIe 版本: 不同版本的 PCIe 速度不同,需要选择与主板兼容的版本。

PCIe 插槽类型:常见的 PCIe 插槽有 x1、x4、x8、x16 等,数字越大,通道数越多,带宽越高。

设备对带宽的需求:根据设备的性能需求选择合适的 PCIe 版本和插槽类型。

参考资料

1816

1816

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?