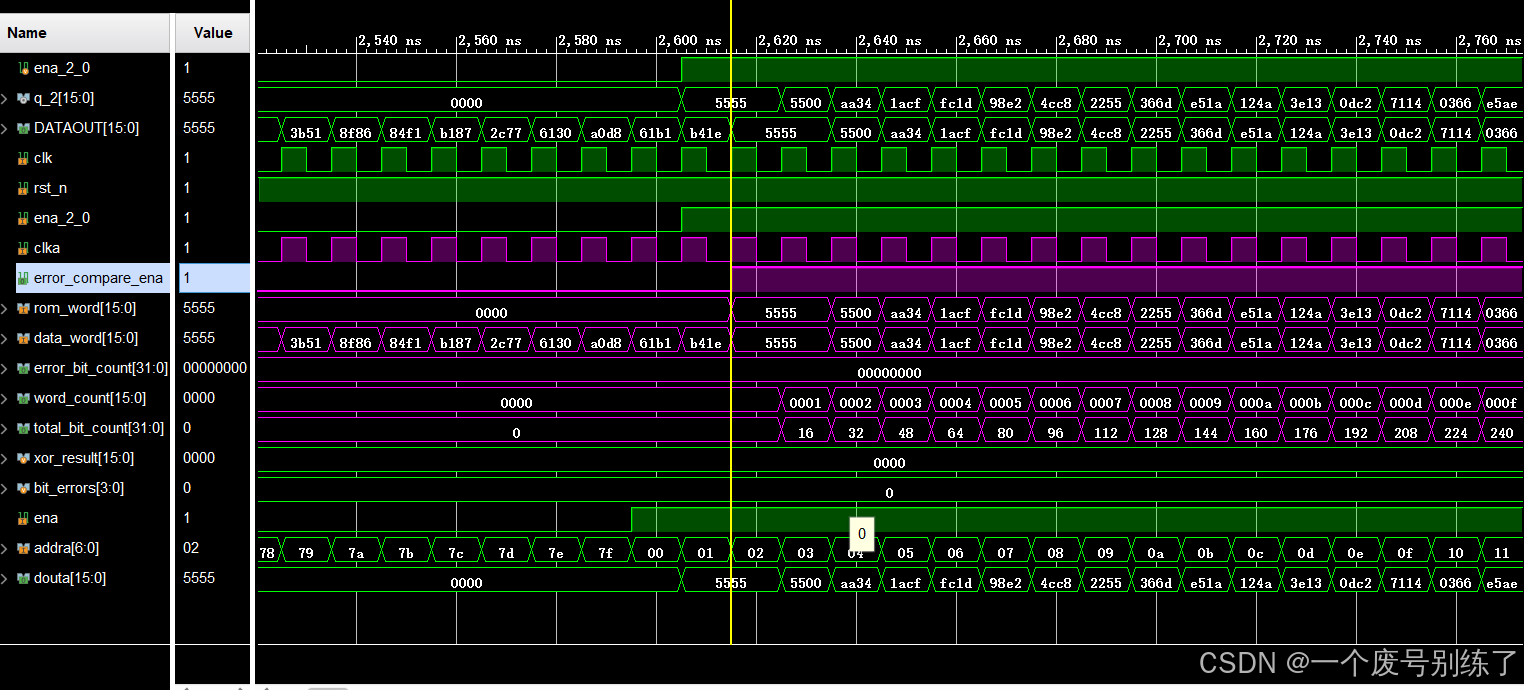

ROM存储标准帧数据,开启使能,按地址输出数据;信道传输之后的数据,通过打拍子,时序对齐之后,对比使能信号开启,两个数据帧对应的word数据进行异或处理,根据相同为0,相异为1,判断异或结果的1的个数,判断误码bit数量。

ROM存储标准帧数据,开启使能,按地址输出数据;信道传输之后的数据,通过打拍子,时序对齐之后,对比使能信号开启,两个数据帧对应的word数据进行异或处理,根据相同为0,相异为1,判断异或结果的1的个数,判断误码bit数量。

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2024/10/24 15:52:07

// Design Name:

// Module Name: error_compare

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module error_compare (

input wire clk, // 时钟信号

input wire rst_n, // 复位信号,低有效

input wire ena_rom_2, // ROM使能控制信号

input wire ena_2_0, // 数据帧使能控制信号

input wire [15:0] rom_word, // ROM中的标准帧word,16位宽

input wire [15:0] data_word, // 需要对比的数据帧word,16位宽

output reg [31:0] error_bit_count, // 错误的bit数量

output reg [15:0] word_count, // 对比的word数量

output reg [31:0] total_bit_count, // 对比的总bit数量

output reg error_compare_ena,

output reg error_bit_count_ena

);

// 内部寄存器

reg [15:0] xor_result; // ROM和data_word的异或结果

reg [3:0] bit_errors; // 当前word中错误的bit数量

// 初始化和复位逻辑

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

error_compare_ena<=0;

end else begin

error_compare_ena<=ena_2_0;

end

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

error_bit_count <= 32'b0;

word_count <= 16'b0;

total_bit_count <= 32'b0;

xor_result <= 16'b0;

bit_errors <= 4'b0;

end

else if (error_compare_ena) begin // 使能信号都为高时,进行word对比

xor_result <= rom_word ^ data_word; // 对比两个word的异或结果

bit_errors <= xor_result[0] + xor_result[1] + xor_result[2] + xor_result[3] + // 手动累加异或结果中为1的位数,表示错误的bit数

xor_result[4] + xor_result[5] + xor_result[6] + xor_result[7] +

xor_result[8] + xor_result[9] + xor_result[10] + xor_result[11] +

xor_result[12] + xor_result[13] + xor_result[14] + xor_result[15];

error_bit_count <= error_bit_count + bit_errors;// 累加错误的bit数量

word_count <= word_count + 1;// 累加word数量

total_bit_count <= total_bit_count + 16;// 累加总bit数量(每个word有16位)

end

end

endmodule

7060

7060

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?