带着以下问题阅读本文,可能会让你觉得不那么凌乱

1、什么是静态时序分析和动态时序分析?

2、静态时序分析和动态时序分析的优缺点?

3、在SOC芯片的门级仿真中,静态时序分析和动态时序分析的辨证关系?

4、静态时序分析的原理?静态时序分析的四种时序路径?如何进行静态时序分析?

5、如何挑选用于动态时序分析的case?

6、PVT corner和RC corner?

7、best condition和worst condition?

8、如何解决建立时间违例和保持时间违例?

静态时序分析(STA)在没有激励输入的情况下分析路径中触发器是否满足建立时间和保持时间,静态时序分析是采用穷尽分析方法来提取出整个电路存在的所有时序路径,计算信号在这些路径上的传播延时,检查信号的建立和保持时间是否满足时序要求,通过对最大路径延时和最小路径延时的分析,找出时序违例(建立时间违例和保持时间违例)。由于可以比较准确地确定路径的最小延时,静态时序分析可以理论上计算出电路的最大时钟频率,同时也可以通过静态时序分析的结果优化电路,提高最大时钟频率。数字集成电路的三大要素:速度(时钟频率)、面积和功耗,因此静态时序分析在数字集成电路中占据重要一环。

静态时序分析的优点是不需要输入向量就能穷尽所有的路径,且运行速度较快、占用内存较少,不仅可以对设计进行全面的时序检查,而且还可利用时序分析的结果来优化设计。但静态时序分析通常用于分析同步电路,不能分析异步电路(时钟相差整数倍的异步电路是可以分析的)

动态时序分析(DTA)是在有激励输入的情况下分析路径中触发器是否满足建立时间和保持时间。动态时序分析的优点是比较精确,而且同静态时序相比较,它适用于更多的设计类型(同步电路+异步电路),但动态分析速度较慢,随着规模增大,所需要的向量数量以指数增长,且不可能覆盖到所有的输入情况,这使得它在分析的过程中有可能会遗漏一些关键路径。

SOC芯片存在数量众多的时钟域,显然没办法对整个SOC芯片做静态时序分析,通常情况下,后端做静态时序分析时,会略过跨时钟域部分的时序检查,静态时序分析会穷尽所有的时序路径,后端会给时序路径加上约束,但可能存在的问题是所加的约束不对,甚至有的时序路径漏加了约束,这些可能的情况后端是很难检查出来的,因此需要前端通过动态仿真进行double check,另外,跨时钟域部分的时序检查也需要通过动态仿真来做。综上所述,SOC芯片的门级仿真往往是静态时序分析和动态时序分析相结合。

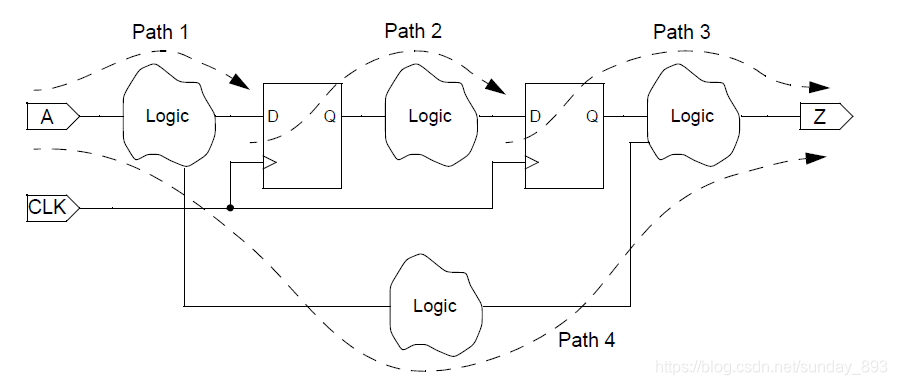

下图是静态时序分析时的四条时序路径

path1 开始于输入PAD(A) 且结束于时序元件的数据输入端(D)

path2 开始于时序元件的时钟端(CLK)且结束于时序元件的数据输入端

path3 开始于时序元件的时钟端且结束在输出PAD(Z)

path4 开始于输入PAD 且结束于输出PAD(这种path实际上是很少见的)

后端在做静态时序分析时需要把BUS以及IP的时钟频率设置到最大,对于有的IP,可能需要通过PAD对外提供时钟,而有的IP,其function时钟由外部通过PAD提供,这些时钟的频率同样应该设置到最大,另外对于一些高速IP会有一些额外设置,这些设置是时序约束,写在时序约束文件中,当然时序约束文件中还会有延时等其他约束。

后端在完成静态时序分析后会提供一个delay反标文件,门级电路是一个个cell,cell之间通过线连接,delay反标是指给这些线和cell加delay,以模拟实际的芯片,前端根据delay反标文件进行动态时序分析。前面讲到,动态时序分析速度较慢,很显然,功能仿真的case不可能全部用于动态时序分析,那么前端在做动态时序分析时怎么选择case呢?由上图中静态时序分析的四条时序路径,path1和path3是IP到PAD或PAD到IP,那么与PAD相关的case是需要的,path2是IP内部的时序路径或IP之间的时序路径,关于IP内部的时序路径,IP在交付使用之前已经做过详细的时序分析了,所以只需要关注IP之间的时序路径,IP之间的操作有CPU访问IP的寄存器、IP产生中断、IP产生DMA REQ、IP访问存储器以及IP与IP之间的其他操作,那么这些case也是需要用于动态时序分析的。

功能仿真不涉及到具体的延时信息,所以功能仿真对时钟频率是没要求的,动态时序分析涉及到具体的延时信息,且后端在做静态时序分析时,已经把BUS以及IP的时钟频率设置到最大,所以在以上挑选用于动态时序分析的case中也应当做同样设置。

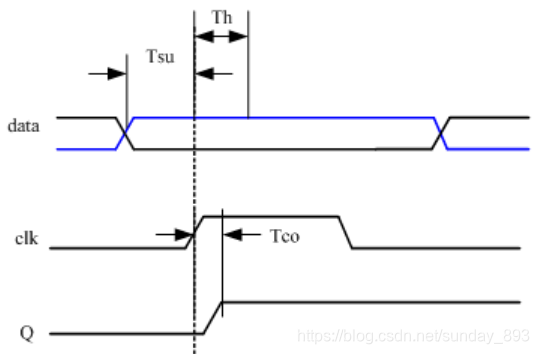

建立时间:在CLK端的时钟上升沿到来之前,D端的数据保持稳定的最小时间,在CLK端的时钟上升沿到来之前,D端的数据保持稳定的时间应大于触发器的建立时间,否则数据不能在这个时钟上升沿被稳定的打入触发器

保持时间:在CLK端的时钟上升沿到来之后,D端的数据继续保持稳定的最小时间,在CLK端的时钟上升沿到来之后,D端的数据保持稳定的时间应该大于触发器的保持时间,否则数据同样也不能在这个时钟上升沿被稳定的打入触发器

那么怎么判断是否满足建立时间和保持时间呢?

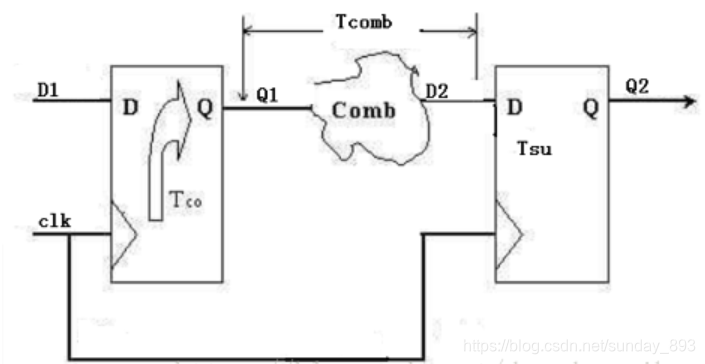

不考虑时钟偏移和时钟延时差的情况

建立时间,DFF1在第一个时钟上升沿驱动数据,DFF2在第二个上升沿采样数据,建立时间很好理解

T-Tco-Tcomb>Tsu

保持时间,DFF1在第二个时钟上升沿驱动新的数据,DFF2在第二个时钟上升沿采样DFF1在第一个时钟上升沿驱动的数据

Tco+Tcomb>Th

如果考虑时钟偏移,时钟偏差为Tskew,时钟偏移有两种情况,正向偏移(时钟周期变大)和反向偏移(时钟周期变小)

时钟偏移只影响建立时间,不影响保持时间

T+Tskew-Tco-Tcomb>Tsu

如果考虑时钟延时差,同样的,时钟延时差也只影响建立时间,不影响保持时间,时钟源到DFF1和DFF2的CLK端的延时差为Tdelay

T+Tskew+Tdelay-Tco-Tcomb>Tsu

FAB会提供标准单元库,标准单元库包括版图库、符号库以及电路逻辑库,电路逻辑库包含时序逻辑、组合逻辑、功能单元、特殊类型单元等以及它们的时序信息,时序逻辑如触发器(Tsu、Th以及Tco)、组合逻辑如与门和非门等(Tcomb),这些标准单元被统称为cell,当然标准单元库中不仅有cell的时序信息,同时还会提供wire的延时信息,任何PATH都是wire和cell的组合,PATH的延时即wire和cell延时的累加。门级网表(netlist)是一个个cell,cell间通过wire连接起来,这里的cell是触发器以及逻辑门等标准单元的模型,GDSII文件是提供给FAB的,其中是整个SOC芯片的晶体管级描述。

corner分为对晶体管的偏差建模的PVT corner和互连线偏差建模的RC corner,PVT corner包括process corner、voltage corner以及temprature corner,由于制造工艺偏差,可能导致有的晶体管速度较快,有的较慢,根据工艺偏差对CMOS管中NMOS和PMOS的影响不同,根据晶体管的速度,可以分为以下五种process corner

1、TT: nominal

2、SS: slow N slow P

3、FF: fast N fast P

4、SF: slow N fast P

5、FS: fast N slow P

晶体管的速度会随着电压的升高而加快,数字逻辑的正常工作电压是1.0v,一般允许的偏差是10%,即数字逻辑可以正常的电压范围是0.9v~1.1v。温度同样也会影响晶体管的速度,温度过高或过低都会使晶体管的速度减慢,通常晶体管能正常工作的范围是-40~125。在做时序分析时,通常是分为best和worst两种情况,best是晶体管速度比较快的(对应的是传输延时较小),而worst是晶体管速度比较慢的(对应的是传输延时较大),best用于检查保持时间是否出现违例,而worst用于检查建立时间是否出现违例。如果出现建立时间违例和保持时间违例,触发器的Q端将出现x,log文件会有Timing violation,怎样消除这些违例呢?

对于保持时间,有如下措施

1、可以插入延时(增大Tcomb,插入BUFF以增大延时,通常用反相器)

2、选用延时更大的cell(增大Tco或Tcomb)

对于建立时间,有如下处理措施

1、提高时钟质量(减小时钟偏移Tskew)

2、选用延时更小的cell(减小Tco或Tcomb)

3、降低时钟频率(增大T)

4、插入触发器(减小Tcomb)

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?