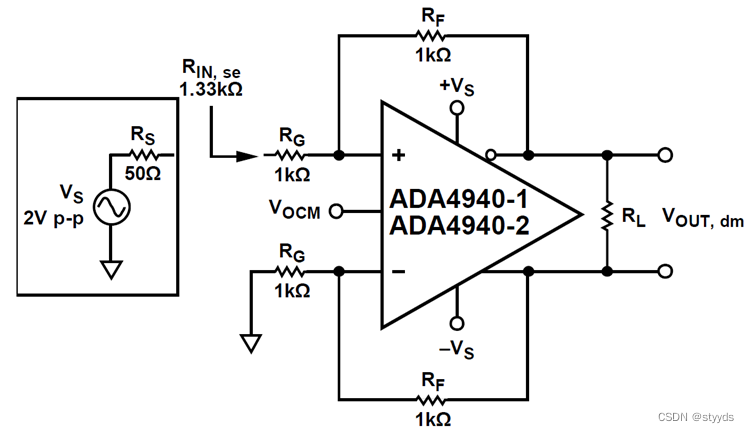

单端输入阻抗公式推导

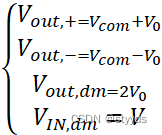

由此得到下式中(1)(2),再根据运放的虚短,虚断得到(3)(4)

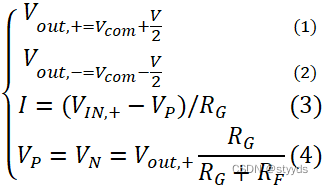

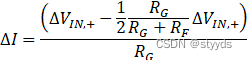

(1)(2)(3)(4)结合得到(5)式:

由于![]() ,则

,则![]() 。

。

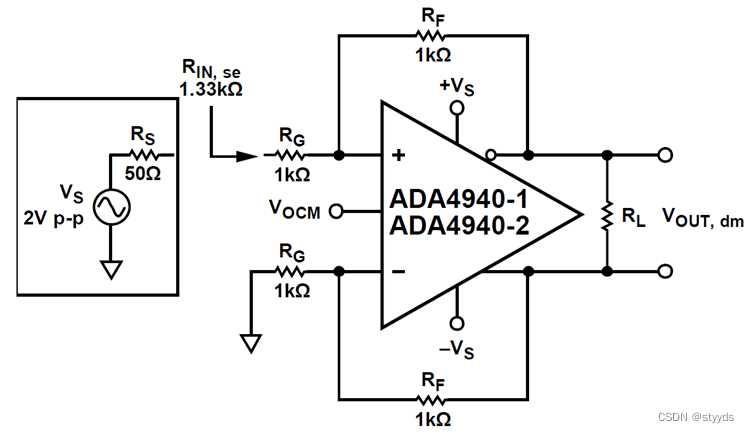

单端输入,阻抗匹配

1.求单端输入阻抗

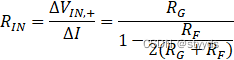

根据上一部分的推导得: ![]()

2.降低输入阻抗

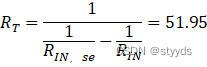

为使输入阻抗等于50Ω,并联一个小电阻![]() 使得

使得![]()

根据阻值表选择最为相近的误差在1%的![]() 52.3Ω。

52.3Ω。

3.平衡增益

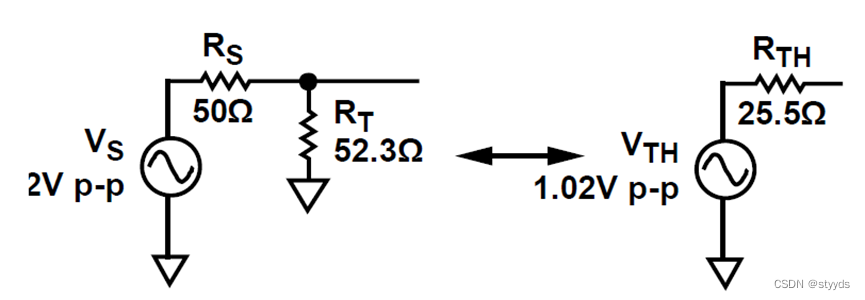

由于上环路增加了终端电阻,导致上下两个环路增益不相等,因此需要在下环路串联一个矫正电阻![]() 。根据戴维宁定理,对输入源和

。根据戴维宁定理,对输入源和![]() 进行等效变换得到图3。

进行等效变换得到图3。

因此![]()

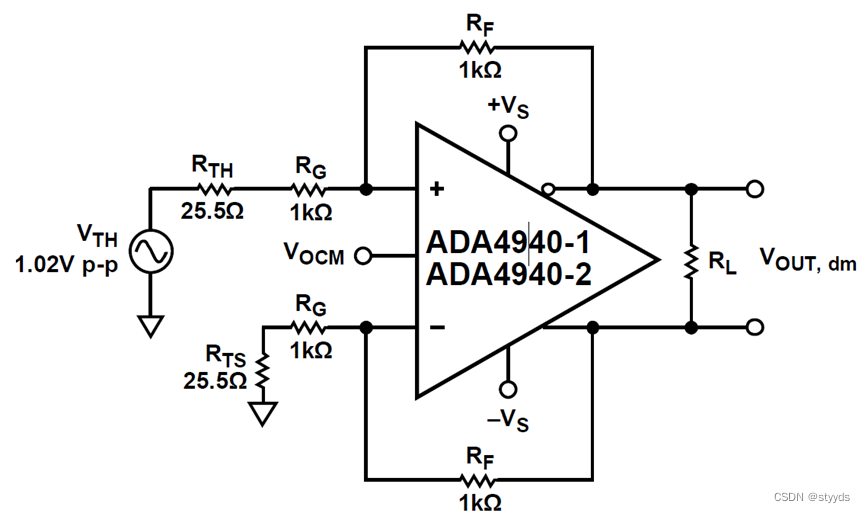

4.调整差分运放增益

根据图4知,等效![]() 的值增大,使得运放增益降低,

的值增大,使得运放增益降低,![]() 。

。

至此,差分运算放大器的增益由原来的![]() 变为

变为 ![]() ,增益降低,如果想要输出

,增益降低,如果想要输出![]() ,可以根据公式(6)可以算出需要把RF变为多少。

,可以根据公式(6)可以算出需要把RF变为多少。

![]()

此时RF*≈2K

疑问:

更改了RF的值,根据输入阻抗的公式,按照图4计算,发现输入阻抗不等于50Ω,这个RF值的更改会不会导致先前的匹配工作白白浪费。还是我不应从等效电路去计算输入阻抗,希望有大佬帮忙解答。

参考资料:

2.ada4940-1/ ada4940-2数据手册中APPLICATIONS INFORMATION部分Terminating a Single-Ended Input.

1026

1026