3.19 A 12 bit bipolar DAC has a 10.00-V reference.

a. What output voltage results from digital inputs of 4A6H, 02BH, and D5DH?

b. An output of 4.740 V is needed. What digital input would come closest to this value? By what percentage is the actual output different?

c. Suppose the output picks up a high-frequency noise of 50 mV rms. How many output bits are boscured by this noise?

3.24 A 10-bit, unipolar ADC with a reference of 5.00 V and a conversion time will be used to collect data on time constant measurement.Thus the input will be of the form

What is the minimum value of for which reliable data samples can be taken if no S/H circuit is used?

The maximum value of the rate of change occurs at t=0, so the condition on conversion becomes:

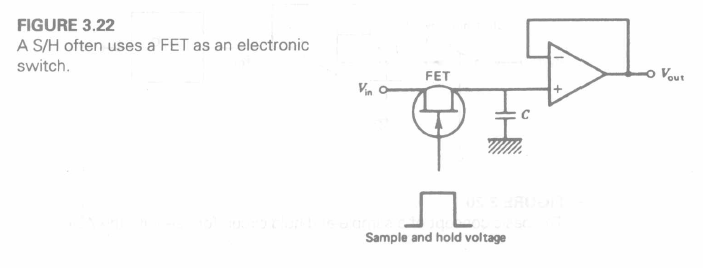

3.26 A sample-and-hold circuit like the one shown in Figure 3.22 has , and the ON resistance of the FET is

. For what signal frequency is the sampling capacitor voltage down 3 dB from the signal voltage? How does this limit the application of the sample hold?

The limitation is the fact that the system cannot be used to sample signals with a frequency greater than about 4.5 kHz because of attenuation.

3.29 A sensor signal is converted to a frequency that varies from 4.6 to 37kHZ. This is to be used with a counter-based ADC of 10 bits. Specify the count time, . What is the count for the minimum frequency of 4.6 kHZ?

3.37 A sensor linearly changes resistance from 2.35 to 3.57 over a range of some measured variable. The measurement must have a resolution of at least

and be interfaced to a computer. Design the signal conditioning and specify the characteristics of the required ADC.

3.41 A digital control system is to provide regulation of pressure within 1.2 kPa in the range 30 to 780 kPa. How many bits must be used for the data acquisition?

3.42 A computer will be used to control flow through 10 pumping stations. The pumps exhibit a surging effect with a period of 2.2 s. What is the minimum sampling rate to ensure quality data? How much time can be spent processing each station's data? Data-acquisition hardware and software take for a channel.

Tt takes 0.22 s to be spent processing each station's data.

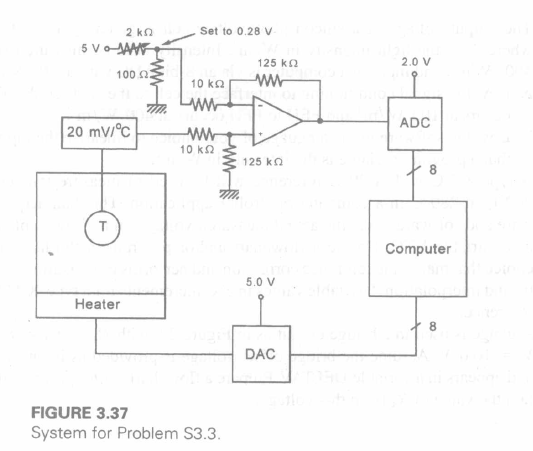

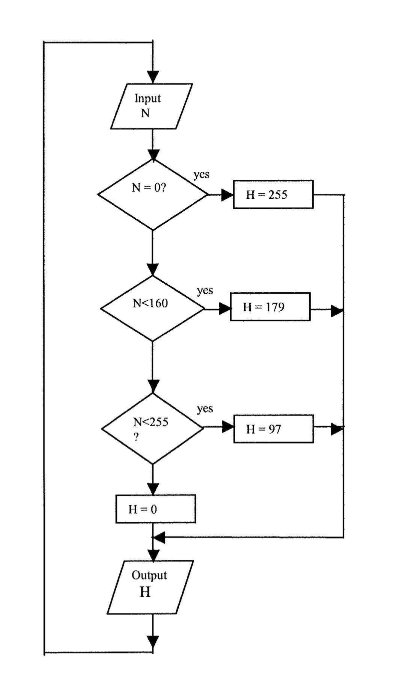

S3.3 A system is persented in Figure 3.37 to provide computer temperature control, The heater requires a voltage from 0.0 to 5.0V for off (0%) to full on (100%). The following algorithm will be used by the computer to determine the heater setting:

1. If : heater at 100%

2. If : heater at 70%

3. If : heater at 38%

4. If : heater at 0%

a. Determine the ADC output for each critical temperature.

b. Determine the necessary heater voltages and the proper DAC input to produce those voltages.

C. Prepare a flowchart showing how a computer program would satisfy the algorithm requirements.

4285

4285

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?